Z-Match ATU ステッピングモーター

バイポーラステッピングモーターとモータードライバー及び5V2AのDCDCコンバーターがそろいましたので、初めてのステッピングモーター動作確認です。 確認する為に、まずPICでモータードライバーのテストプログラムを作ります。

テスト回路配線図 steping_motor_test.pdfをダウンロード

テストプログラム STEPPING_MOTOR_Test.cをダウンロード

実際のATUの場合、EEPROMが1Kバイトは必要になりますが、手持ちが無いので、NB-ATUのコントローラーに使っていたPIC18F25K42でテスト用のプログラムを作り、モーターを思うようにコントロールできるかどうかのテストです。 テストプログラムはTimer1で周期的な割り込みを発生させ、割り込みが発生する度にモーターのSTEP入力を反転させます。 反転周期の2倍がワンクロックとなりその逆数がクロック周波数となります。実験ではクロック周波数100Hzで行いました。 またこのSTEP入力は常時LレベルでMOTOR ON SWを1回押すと、指定したパルスの数だけクロックが発生し、最後にLレベルで停止するようにソフトを組んであります。 ソフトの行数が多いのはMOTOR ON SWのチャタリングを除去する為の処理です。

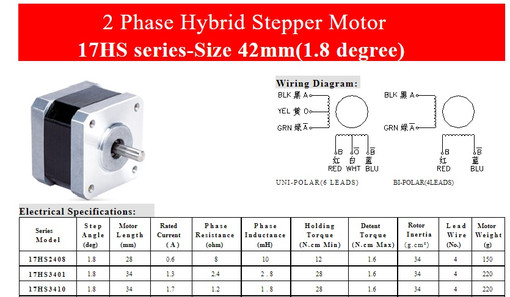

上の表に出てくるモーターの型番の最後にSの文字が付きませんが、この実験で使用しているモーターの型番は17HS3401Sで、中文で書かれた仕様書では、定格電流1A, 定格電圧7.3V、コイル抵抗3.4Ω となっており、他の解説資料に書かれている、定格電圧=定格電流xコイル抵抗 の定義に合いません。 そこで電圧3.4Vの電源と電流リミッターを0.25Aに設定して、テストを開始しました。 基本となるワンステップ1.8度の回転は成功しましたので、次は基準の1/2となるワンステップ0.9度にトライ。 ところが、うんともすんとも言わず全く動きません。 配線がわるいのかと全接続をチェックしましたがまったくダメ。 電流制限を1Aにしてもモーターが起動しません。 試しに1/4はどうかとテストすると、やはり起動しませんが、電源OFF状態でモーターのローターを何度分か回転してやると回転を始めます。一度回転を始めて、止めてまたONしてもちゃんと回転します。 起動トルクは1/2ステップより1/4ステップの方が大きい様です。 従い、以後、1/4ステップのみで実験を継続する事にしました。

そして、確実にモーターが起動する為には、モーター電圧は5V以上、電流制限は0.75A以上の設定が必要という事がわかりました。 安定してドライブ出来る為にはモーター電圧6V、電流制限1Aとし、モーター回転中、及び停止中の12V電源の消費電流は0.45A程度で有る事が判りました。 この状態は、ステッピングモーターの解説書にある定格電圧の2倍くらいの電源電圧に設定し、電流を定格以下で使うという説明にはまだ合致しません。さらに停止中は電流制限を0.2A程度まで落としても、静止トルクは指では回せないくらい大きい状態で、この時の12V電源の全電流は100mA程度になりました。 この静止トルクを維持出来る最低電流は再検討する事にします。

この実験の中で、得られたその他の情報で重要なのが、電源OFF時の停止位置と電源ON時の起動位置の誤差でした。1.8度ステップ以下のステップの途中で停止したモーターは電源をOFFしない限り、停止した位置から起動しますが、一度電源をOFFすると、静止トルクは無くなり、一番近い1.8度の停止角度の位置に移動してしまいます。 次に起動するときは、電源OFF前の位置からずれた角度位置から起動する事になります。 この事は、電源を再投入する毎に機械的位置のイニシャライズが必要であると言う事です。 これは、バリコンの最大容量または最小容量の位置を電源ONする度に何らかの手段で検出し、その位置をゼロ番地として回転ステップ数を刻む必要がある事になります。 さらに、このイニシャライズ動作時は基準ステップ(1.8度)で駆動しないと駄目だという事も判りました。

ATUの電源をONにしたらその後電源を切る事ができませんので、モーターSTOP中の電流を最低レベルに切り替える回路を追加必要です。 さらに、モーターがSTOPする度に、現在位置をEEPROM上に記憶させて置かないと、電源OFF後に前の状態に復帰出来ないという事になります。 さらに、受信中も電源をOFFできないので、この間に発生するノイズも確認しておかねばなりません。 モーター駆動中はPWM電流でドライブしていますので、それ相当のノイズが発生するとは考えられますが、モーターOFF時の電流制限もPWMで行っているので、ノイズは消えません。 いずれにしても、事前確認が必要です。

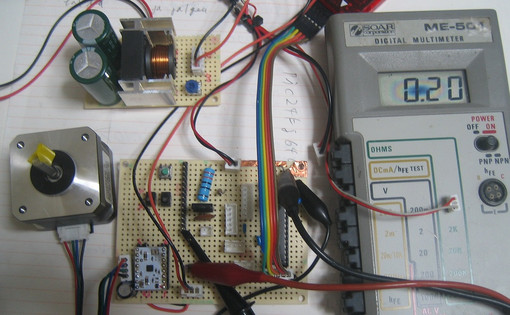

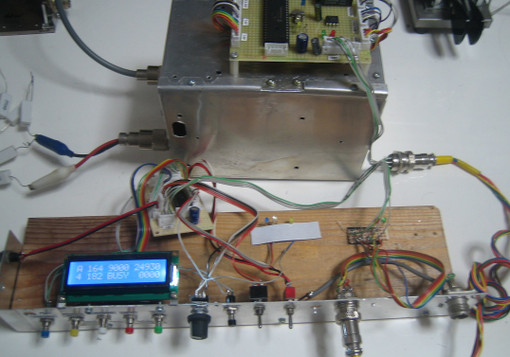

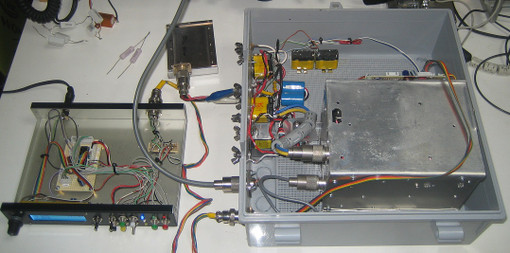

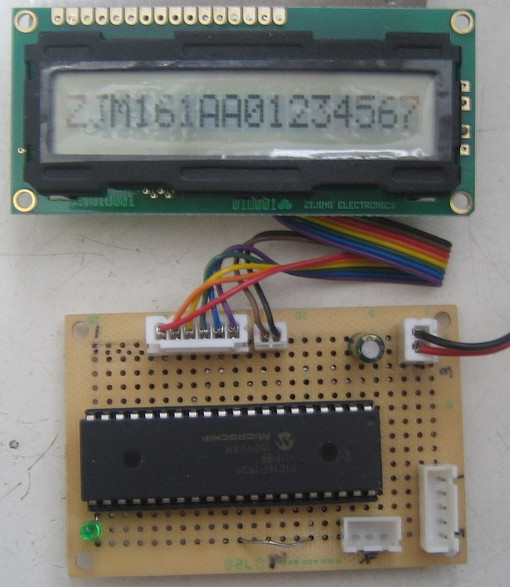

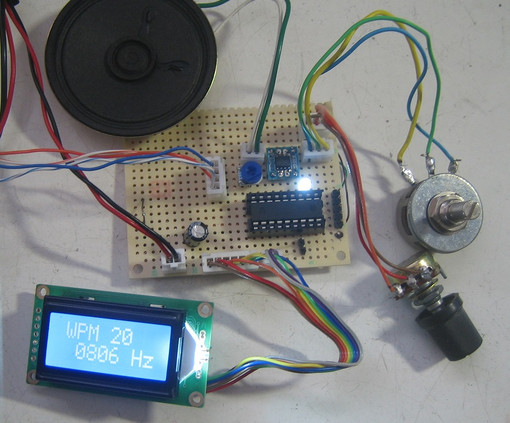

上の写真はテスト用のマイコン基板とモーター、DCDC電源、電流制限値(0.2x5A)を測りながらテストしている状態です。 電流制限は1Aですが、モータードライバーのパッケージを指で触ってもほんのりと温かいですが、ずっと触っていられる状況です。 メーカーの説明によると基板が熱伝導の良い金属製の基板に絶縁膜を作りその上に導体を印刷した構造の物で、基板自身が放熱板になっているとの事。さらにその基板に銅製の放熱板をハンダ付け出来るようにしてありますが、私が使うATUでは、追加の放熱板は不要です。 写真の基板上には配線図にない部品も映っていますが、NB-ATUのコントローラーで使用した部品がそのまま残っています。実際に配線されている部品は配線図通りです。

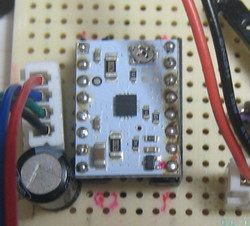

左が、約1000円のモータードライバーですが、最初、この基板の裏表を間違って、ピンを半田付けしてしまい、一度半田付けしたpinを一本づつ引き抜いて再半田する羽目になってしまいましたが、壊れもせずにちゃんと動作しています。

テスト基板に直接ハンダ付けしてしまうと、本番の基板に移すのが大変ですから、ICソケットを用意して、抜き差し出来るようにしましたが、このドライバーに付属していたピンは太くてICソケットに挿す事が出来ませんでした。 秋月で手配した細いヘッダーピンがありましたので、これに交換して、写真のように実装出来ました。

モーター停止時のみ電流制限値を小さくする為、VREF信号が(2)ピンに接続されるよう基板の裏にあるショートパターンをハンダでショートしてあります。

モーター静止状態のロックトルクを確認しました。 制限電流設定で50mAでは手でモーター軸を回す事ができますが、100mAの場合、軸を回す事が出来ません。 設定は余裕を取って150mAとします。 この時の12V電源側の電流は25mAでした。 25mAはリレーを1個ONしている状態に等しく、電源的には全く問題有りません。

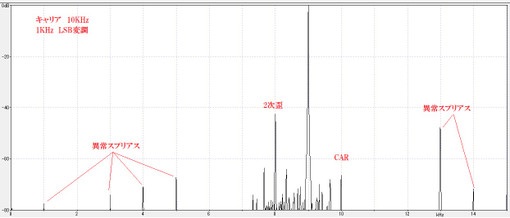

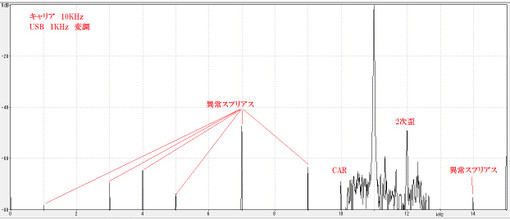

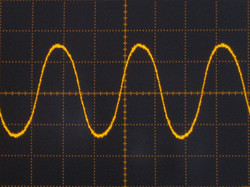

次にノイズの確認です。 受信機のアンテナ端子に接続された同軸ケーブルの先端に50cmくらいのワイヤーを接続し、このワイヤーをモータードライバーのICの上に置いてみました。 すると、モーター停止中、回転中いずれも、SメーターがS8まで触れます。 最大の振れは28MHzでした。 ICとワイヤーの距離を30cmくらい離すとS3くらいまで落ち、1m離すとS1くらいになります。 モータードライバーの回路はシールドした方がよさそうです。モーター電源をOFF するとノイズは無くなりますが、1.8度の基準ステップ以下のマイクロステップモードで使う場合、電源OFFしたとたん、モーターの停止位置が一番近い基準ステップの位置に移動してしまうので、電源をOFF出来ません。

この実験の途中で新たな問題が発見されました。 モーターが回っていないときは電流制限を150mAに設定し、モーターが回り出す150msec前に電流制限を1Aに変更してもモーターが起動しません。 電源投入時点よりずっと電流制限1Aにして置き、一度モーターが回転したあと、停止した後で電流制限を150mAにした場合、次のモーターON前に電流制限を1Aに変更すると正常に動作します。

このイレギュラーの動作を解消する為に、カット&トライを繰り返した結果、以下のシーケンスで完璧に動作するようになりました。ここまで判ったのが10月中旬の最後の金曜日でした。 モーター電圧は7.3V、電流の制限値は250mAです。

①マイコンICのSTEPパルス発生用のタイマーをOFFにする。

②電源投入直後nENをL(active)にして置き、STBYモードで1/4マイクロステップの設定を行う。

③10msec後にSTBYを解除して、さらに10msec待つ。

④以後、モーターを回す前に必ず該当するタイマーをONし、モーターをストップさせた時は必ずタイマーをOFFにする。

⑤1.8度の基本ステップで動作させたい時はMODE1,MODE2をLとして、1.8度ステップの動作が終了したら、設定済みのマイクロステップモードに戻す。

⑥以後、①から③までの処理は行わない。

これで正常に動きだしました。モーター回転中の12V電源の電流は150mA弱、STOP中は25mAです。 そして、このモーターの仕様書を目を凝らして読むと、どうもコネクターの並びが逆ではないかと疑いが生じました。

そこで、コネクターを180度反転してみました。すると、1/2ステップモードでもモーターが回転するようになったのですが、ワンステップ1.8度のノーマルステップでした。その他に、1/8とか1/16を試しましたが、1/8と1/16は同じステップで1/16くさいです。 もしかしたらモーターの構造により、IC屋が意図したドライブタイミングの通り動作しない事もあるのかも知れません。 幸い、1/4ステップは正常に動作していますので、良しとします。

このマイクロステップ駆動に関しては、1/64マイクロステップで動作する赤道儀を実現したプログラムを公開しています。

モーター停止時、電流制限を小さくする手段、nENを制御する手段を追加した回路図とテストプログラムです。

配線図:steping_motor_test_1.pdfをダウンロード

ソフト:STEPPING_MOTOR_Test_1.cをダウンロード

ここに示しました、モータードライブプログラムは、初歩的な動作確認用です。 実際に実用しているプログラムでは有りません。 もし、実用的なプログラム例が必要な場合このページを参照して下さい。

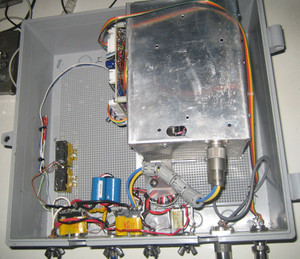

一応ステッピングモーターの動作確認ができましたので、バリコン駆動機構の設計にとりかかります。 このATUは中古のコメットのMTUのケース内に収納する予定なので、機構のサイズを含めて検討開始しました。