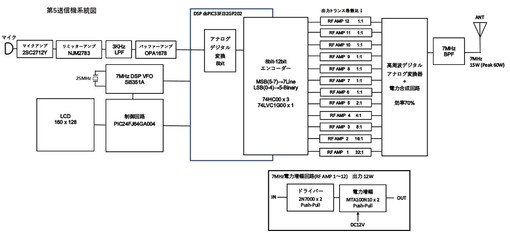

<カテゴリ AM送信機(デジタル方式) > [Si5351A VFO]

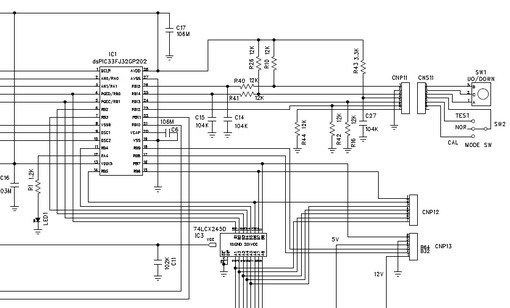

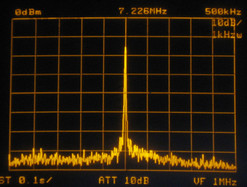

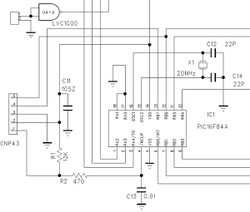

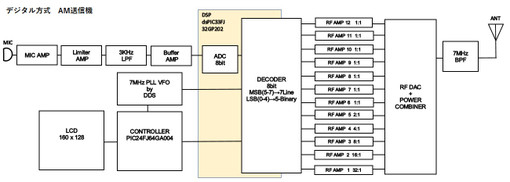

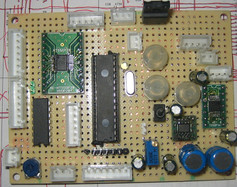

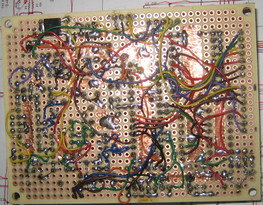

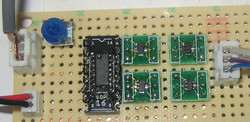

デジタル方式 AM送信機の組み立てを行っている最中に送信周波数がずれるという問題が見つかり、またしても、PLL VFOは頓挫していましたので、PLL VFOをきっぱり諦めてSi5351によるDDSへ作り替える事にします。 SI5351のICは手元に在庫が有ったのですが、10pinの変換基板と25MHzのクリスタルが有りませんでしたので、これをやっと手配して、半日で、基板改造と、ソフト変更を行い、無事完成しました。

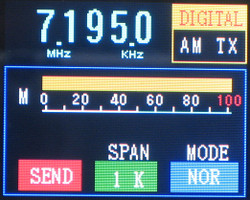

左が、DDS VFO化した時のLCD表示で、このショットはキャリブレーションモードの時です。

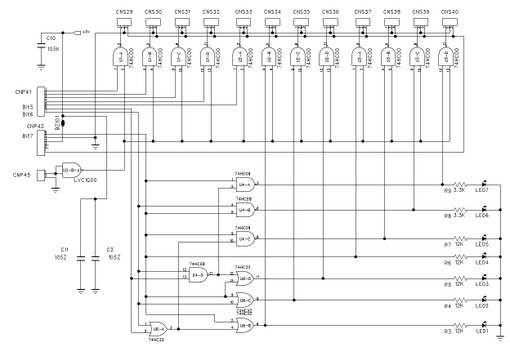

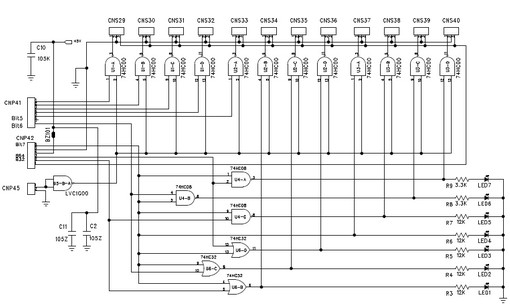

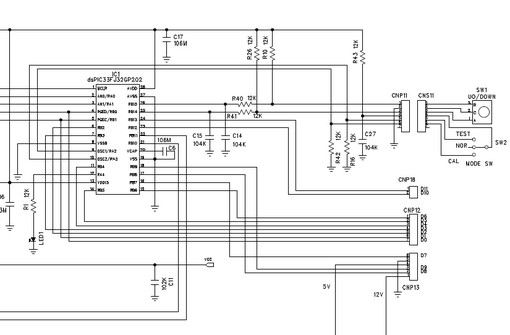

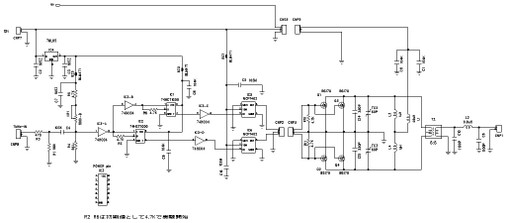

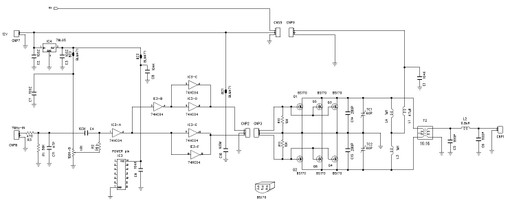

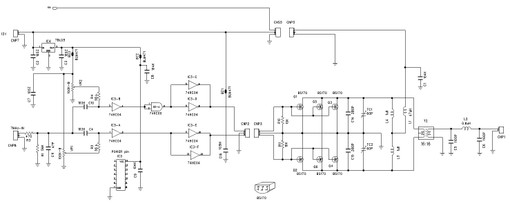

DDS VFOの配線図7MHz_Si5351_VFO.pdfをダウンロード

DDS VFOのソフト AMTX-Si5351-VFO_7MHz.cをダウンロード

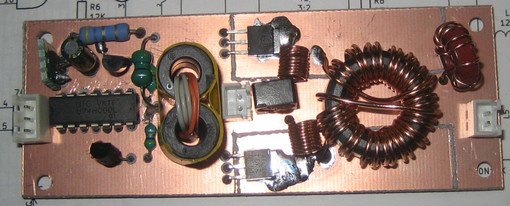

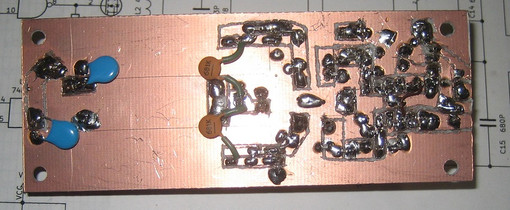

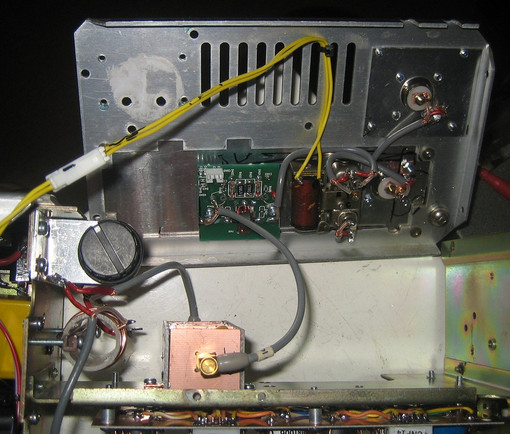

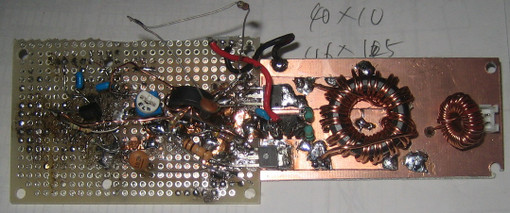

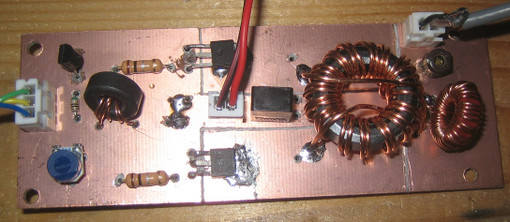

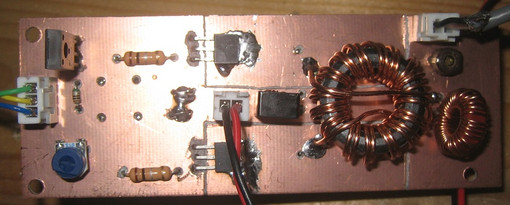

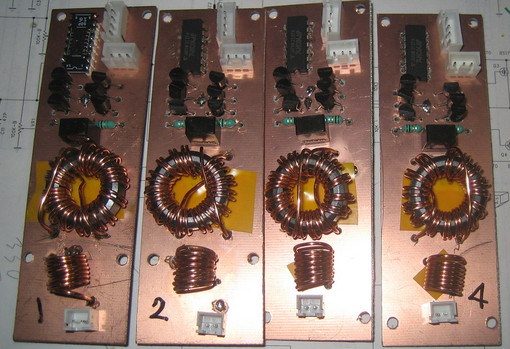

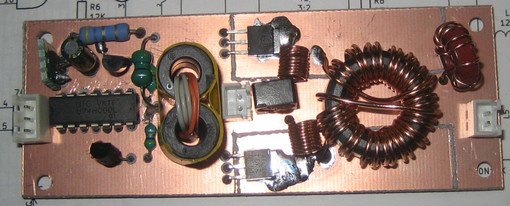

また、再設計を余儀なくされたRFパワーアンプも上の写真のように、ある程度見込みがつき、最大出力16Wくらいで、熱設計も目途が出てきましたので、データを取った後、全12台を作り替える事にします。

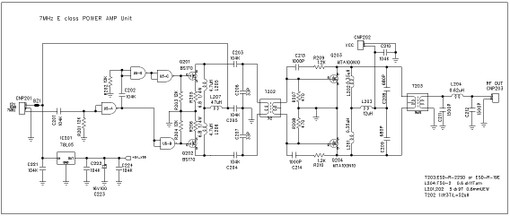

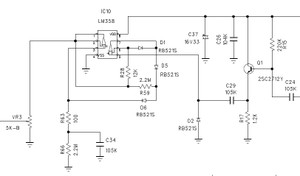

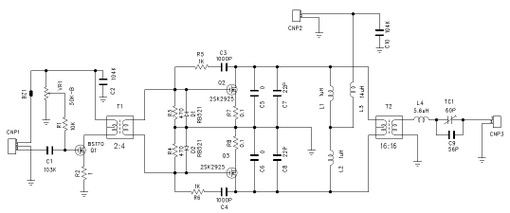

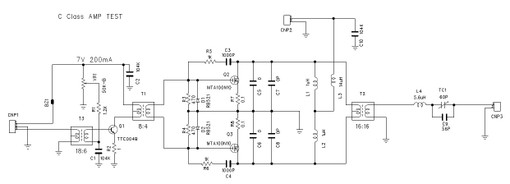

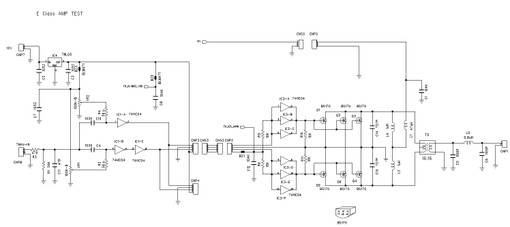

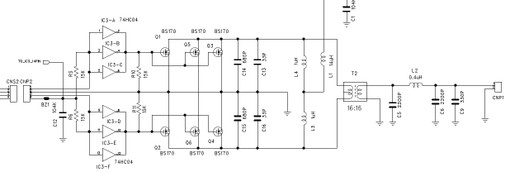

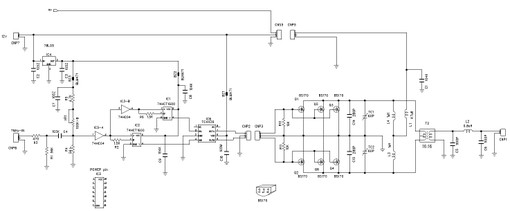

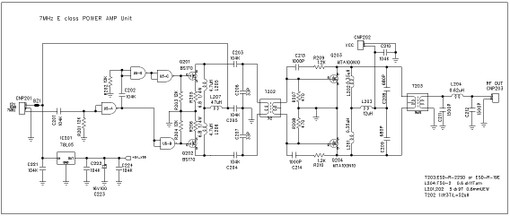

設計変更のメインは、CMOS ICによるゲートドライブの復活です。 CMOSゲートによるドライブは、2N7000クラスのCiss=20PくらいのFETに限られ、出力10W クラスのFETのCiss=400Pくらいのゲートをドライブする事は無理でした。 そこで、このCMOSゲートの出力で、BS170 プッシュプル回路をドライブし、その出力として、1W程度の正弦波に近い出力を得た後、これで、10W クラスのプッシュプルによる終段をドライブするという構想にしました。

結果はVY FBで、12Vの電源電圧で16Wが得られ、試作機では73%の効率でした。 また、BS170プッシュプルによるドライバーもFETを指でつまんでも問題ない程しか発熱しません。 ただし、データシートに書かれたPd max をオーバーしないように、安全の為、ドレインラインに4.7Ωの抵抗を入れました。 この状態で、終段の電源電圧を13.8Vまで上げると、出力は約21Wとなり、電源電圧対出力の関係のリニアリティは確保されており、ドライバーとしての余裕も確認出来ました。 実際の運用では、電源電圧は12Vとし、終段のFETのPdがオーバーしないようにします。

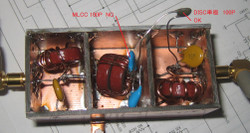

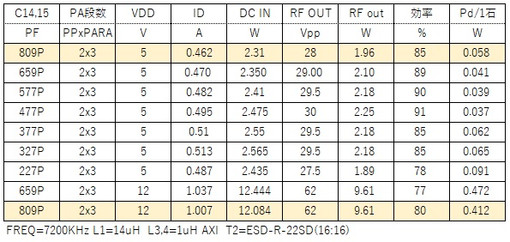

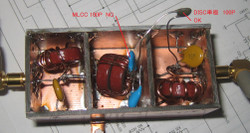

E級アンプを構成する為の、共振回路のコンデンサの値が、計算値と大きく異なる状態が継続していましたが、積層セラミックコンデンサ(MLCC)にDCバイアスを与えた時の容量ダウンが、当初考えていた数値よりかなり大きい事がわかりました。 MLCCの特徴について、詳しい解説がここにあります。 チップタイプのコンデンサはほぼ全てMLCCタイプですので、この問題は避けて通れない事になります。 従い、共振周波数を決めるコンデンサの両端には、DC電圧がかからないように回路変更を実施しました。 また、アキシャルやチップ部品で構成したインダクターのDC抵抗はかなりバラツキ、動作状態により、経時変化も大きい事から、DC直結の出力トランスはコアの磁気飽和が頻繁に発生し、FETを熱破壊する事も判りましたので、自作のUEWによるコイル以外の場合、トランスはDCカットする事にしました。

このAM送信機を組み上げて、パワーアンプの動作テストを行う時、RF出力のGNDをシャーシに接触させて置かないと、おかしなオシロの画面になるのですが、この原因が判るまで、2週間かかり、その間、回路構成まで疑う事になってしまい、ほとほと疲れました。

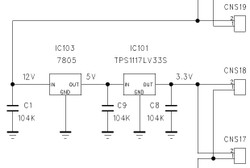

この問題で、電源フィルターのGNDを一部修正し、CNP12のピン番号が逆でしたのでこれも修正しました。 RFADC_AMTX_audio-1.pdfをダウンロード

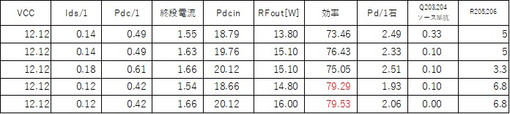

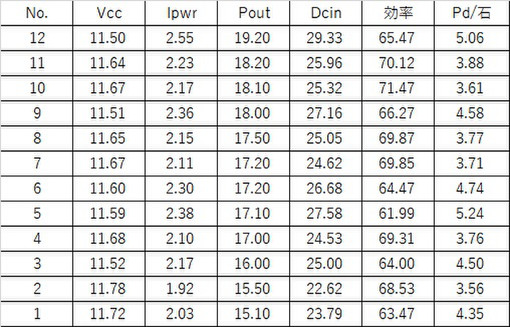

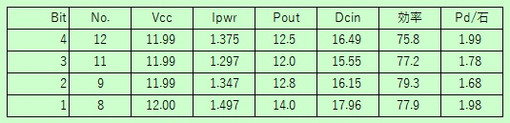

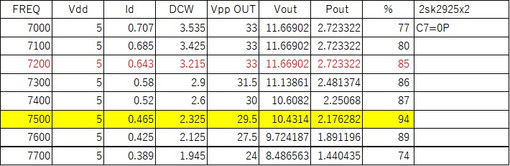

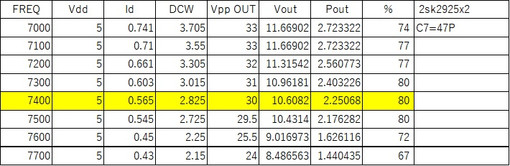

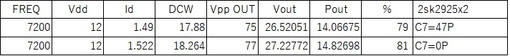

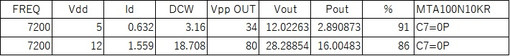

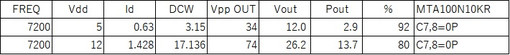

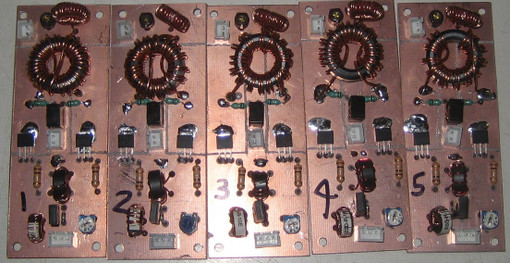

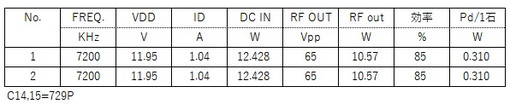

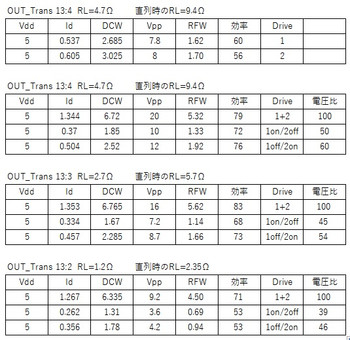

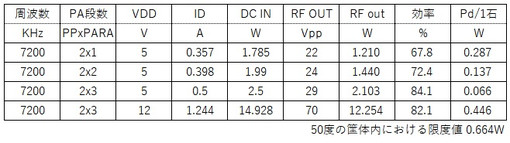

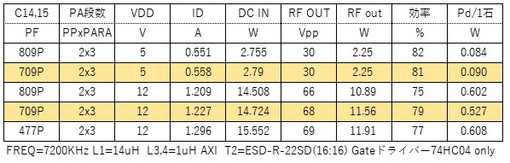

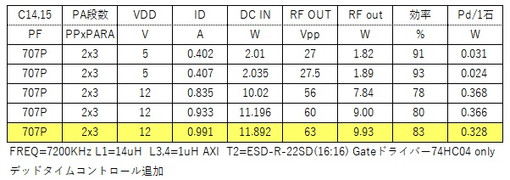

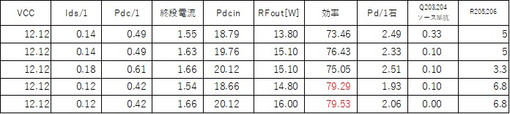

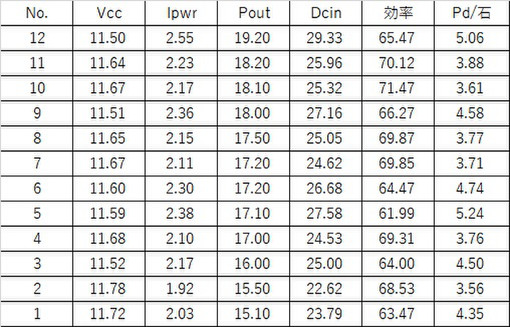

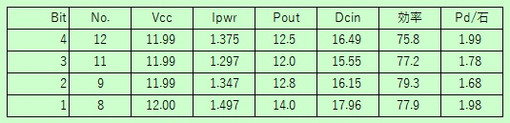

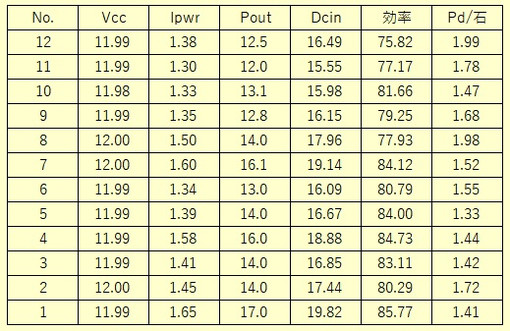

この対策を行った後、取得したパワーアンプのデータは以下のようになりました。 当初、追加してあったドライバー段の電源ラインの4.7Ω抵抗は廃止してあります。

終段の効率が80%を切っていますが、出力が大きくなった分、1石当たりのPdは許容値を超えているかも知れません。 またBS170プッシュプル回路のPdもギリギリ許容値なので、以後、この状態で検討を進めていきます。

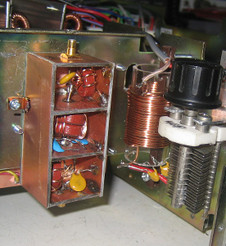

パワーアンプが1台完成したので、この1台のみを半完成状態の送信機に接続し、出力をチェックしました。 送信開始直後は16Wくらい有る出力が、どんどん減少し、約10秒後には5Wくらいになってしまいます。 原因を調べる為に、各ブロックの入出力をひとつづつショートしていくと、BPFの入出力を直結した時この現象が起こらなくなりました。 原因は、直列共振の為に使用したMLCCタイプの100Pでした。 これを40年以上前のDISCタイプの100Pに変更したら、あっさりと直ってしまいました。 最近は100Pの容量でもMLCCになっているので要注意ですね。 本来はシルバードマイカコンデンサでないとダメなのですが、フィルターのケースの中に納まりません。 実験に使ったセラミックコンデンサは公称50V耐圧で実力1000Vくらいありますので、これに交換し、様子をみます。

2023年1月

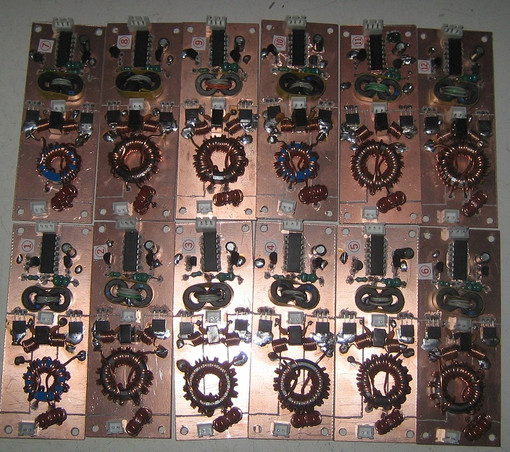

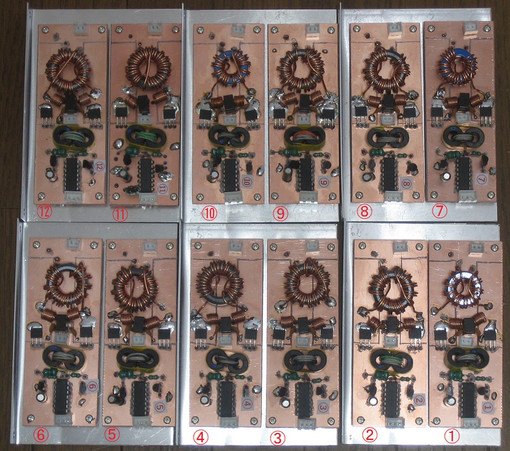

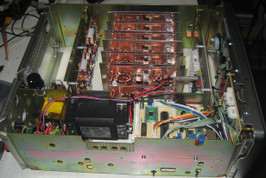

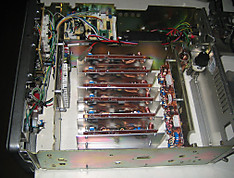

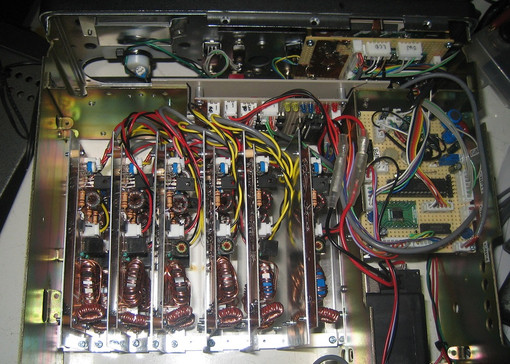

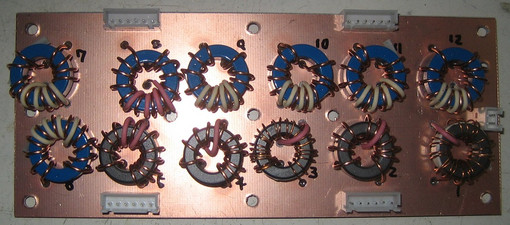

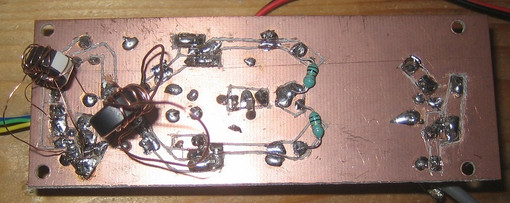

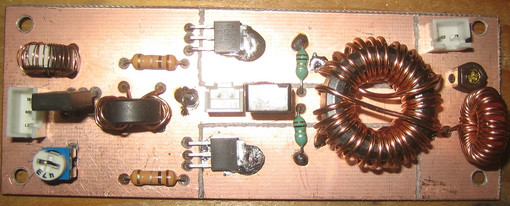

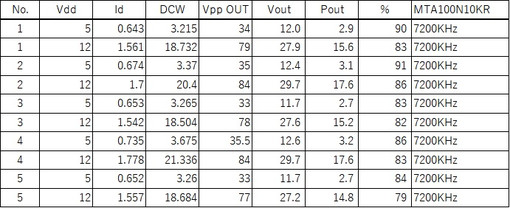

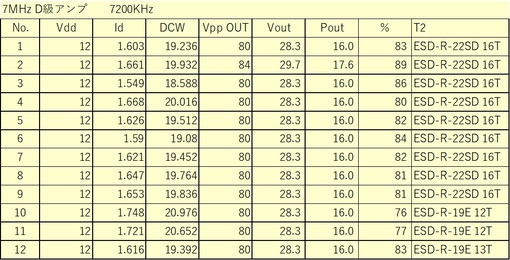

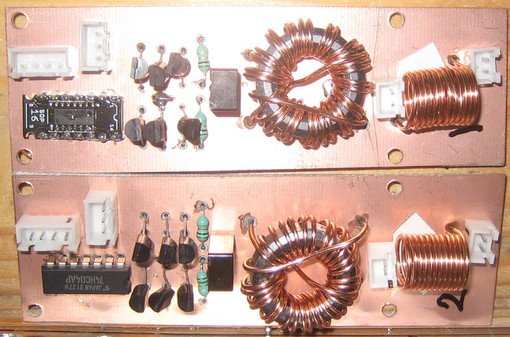

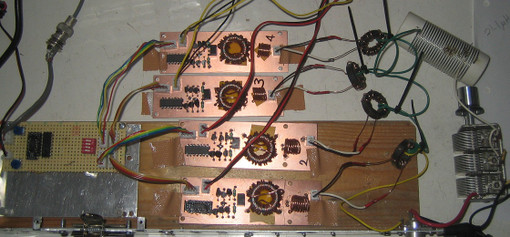

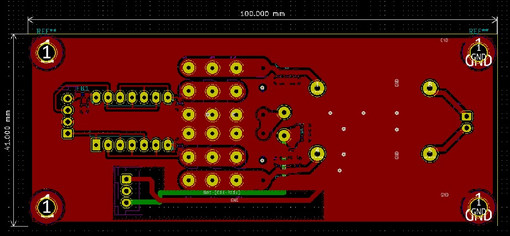

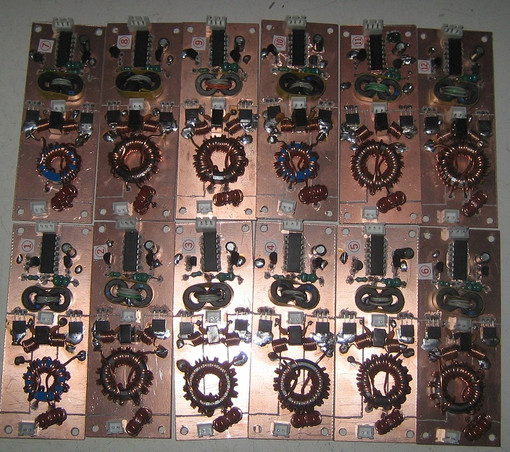

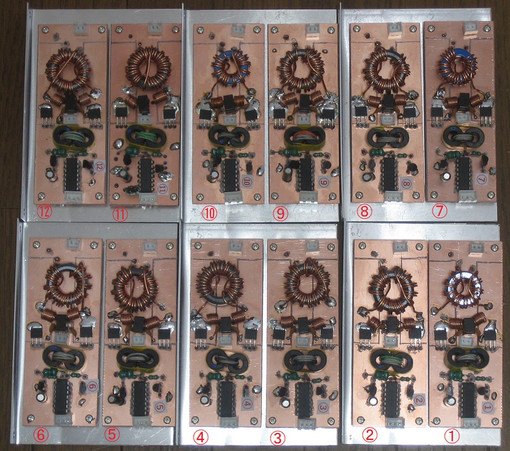

改良型のパワーアンプが12台完成しました。

12台のアンプは、7195KHzにてドライブし、出力最大となるように、出力のパイ型LPFのコイル(L204)を微調整したものです。 12台中1台がコイルの巻き数が10ターンで、残りは全て11ターンにし、コイルのピッチを広げたり、狭めたりしました。 使った電源は実際に使用する回路を使い、測定した電源電圧はラインフィルターを通った後のRFパワーアンプの入力端子間のものです。 すこし、レギュレーションが悪いですが、後々問題になりそうでしたら、検討する事にし、それまではこのまま進行します。

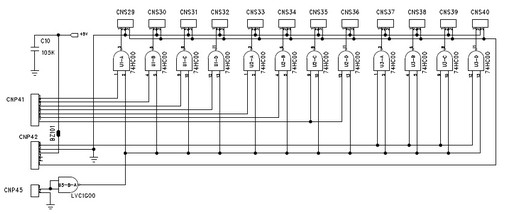

12台のアンプのデータを取り、出力が小さい順に番号を付けました。 この番号が8bitのエンコーダーでLSB側から①、②、③・・・・とMSBまで配列されます。 ただ、心配ごとが。 ちょっとパワーが出すぎです。 Pdも許容値以上かも知れません。

また、出力波形の左側は、トロイダルコアによるトランスの1次側、右が2次側の波形で、極性が反転していますが。レベル差はほとんどありません。 前回NGだったのは出力回路を直列共振回路にしたのが原因であろうと予想し、今回は以前、電力合成が成功したLPF型にしました。

この12台の製作の途中で、秋月のBS170の在庫がなくなり、やむなく2N7000に一部変更しましたが、2N7000でドライバーを構成したアンプはいずれも18W以上を出力していますが、終段の効率は70%を切ってしまいました。

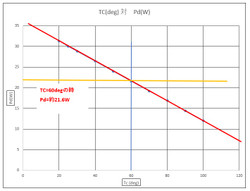

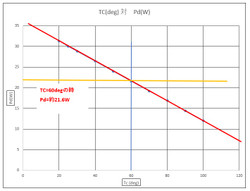

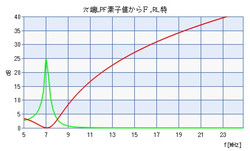

左のグラフは、FET MTA100N10 のケース温度(Tc)対ドレイン損失(Pd)の関係をグラフにしたものです。 これによると、終段FETのケース温度が60度の時でも、Pdは21.6Wありますが、この数値は、放熱板の代わりに用意した、銅箔が均等に60度になった時で、厚さ25ミクロンの銅箔面を均等に暖める訳はなく、エージングで確認するしかないでしょう。

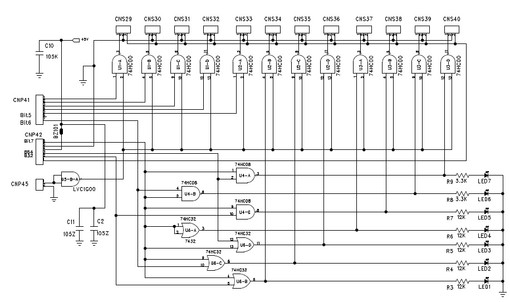

ここまでの、エンコーダー + RFアンプユニットの回路図 RFADC_AMPx12-3.pdfをダウンロード

ここまで出来た所で、出来の良さそうな4台のアンプを使って、電力合成の確認を行いました。 結果は全くダメでした。 出力が足し算されません。 組み合わせによっては減算される事も発生します。

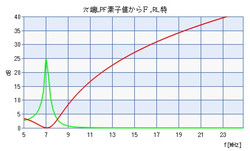

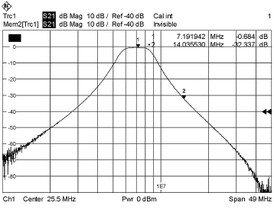

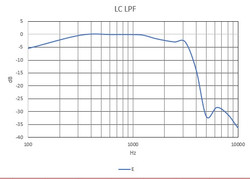

やはり、AMPの出力の位相が完全に揃っていないようです。 左のグラフは終段のLPFの減衰特性ですが、緑色の線は、コイルのインピーダンスと負荷抵抗50Ωの比をdBで表したもののようです。 7MHz付近にピークが有り、ここで、LCによる共振が発生し、きれいな減衰特性を得ていると思われますが、当然、この共振ポイントを境にして、その両側の位相は逆転します。 12台のアンプのLPFの特性がそろっていない事は前述していますが、共振周波数は管理されておりませんので、位相が真逆のAMPが出来て当然のようです。 前回、LCの共振回路が影響して、出力の合成がうまくいかなかったので、初期のころ、LPF付きAMPで電力合成の実験を行い、そこそこのデータが得られていましたので、今回もそれに合わせたのですが、前回はたまたま位相がそろっていた為だったのでしょう。

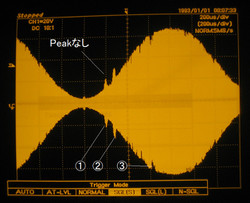

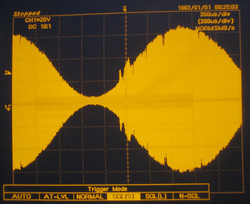

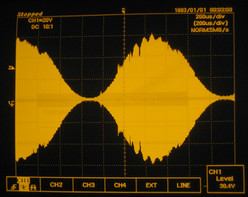

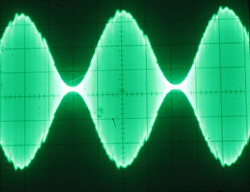

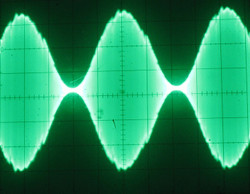

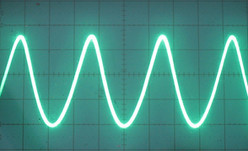

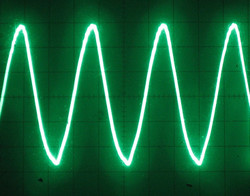

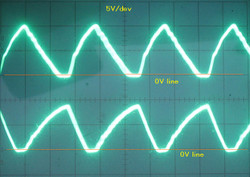

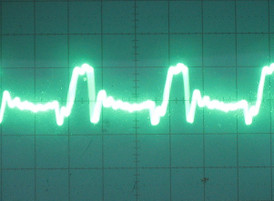

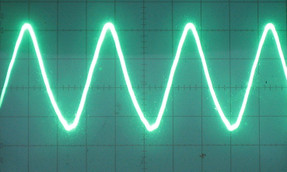

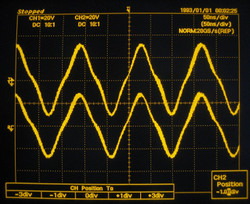

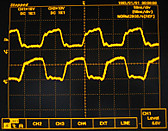

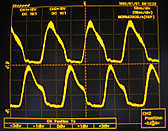

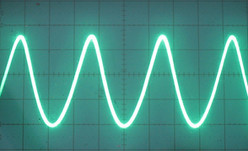

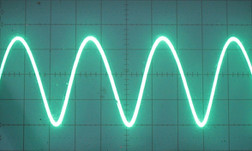

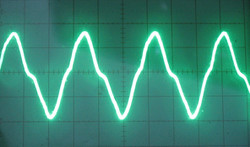

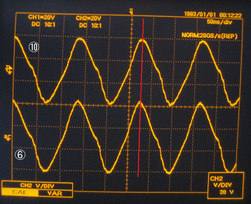

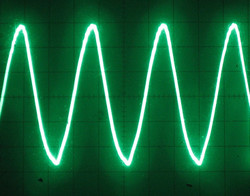

左の波形は、終段のLPFを廃止した時の出力波形です。 クロスオーバーぎみの波形ですが、E級アンプの共振コンデンサにDCがかからないようにした結果、ほぼ計算通りの容量で、きれいなドレイン波形を形成出来ており、トロイダルコアによるトランスを経由しても、歪の変化は有りません。

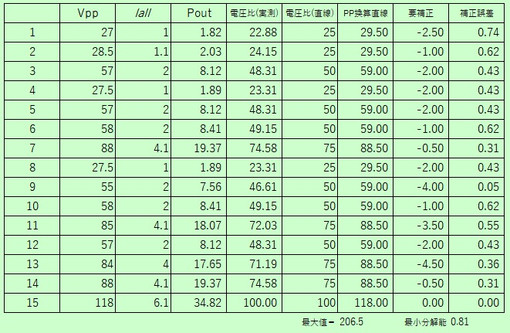

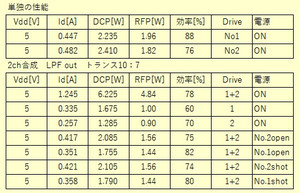

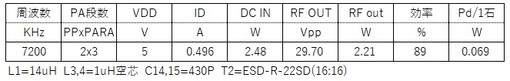

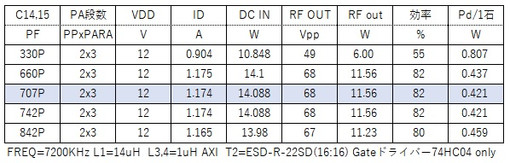

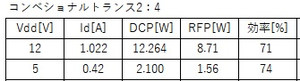

とりあえず、4台のみLPFを廃止したアンプを作り、そのデータを取ってみました。

出力はかなり落ちましたが、効率が全て70%台となり、1石当たりのPdも安心できるレベルまで少なくなりました。

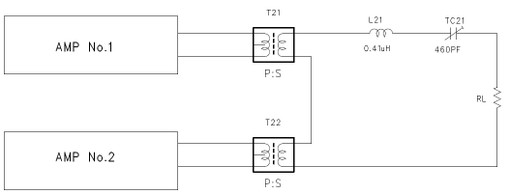

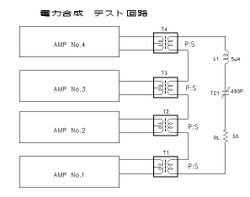

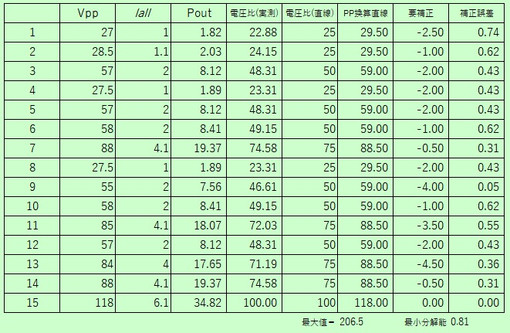

この4台のアンプを下からBit1,2,3,4の順に並べ、合成トランスを50:12.5のインピーダンス比にして、電力合成のデータを取ってみました。

4台のアンプをバイナリーで駆動していますので、データとしては15種類になります。 一番下のデータは4台のアンプを全て合成した時のデータになりますが、計算上では48Wくらいにならないとダメですから、かなりロスが生じている状態です。 ただし、実測データは理想の直線と合致はしていませんが、そこそこの数値を示しています。 仮にこの状態で、プリディストーションを行い、全部補正出来たとすると、各アンプの合成出力はLSB 1bit以内に補正出来る事を示しています。

この4台のデータから、なんとか目途が立ってきました。 12台全部の改造を行い、確認をする事にします。

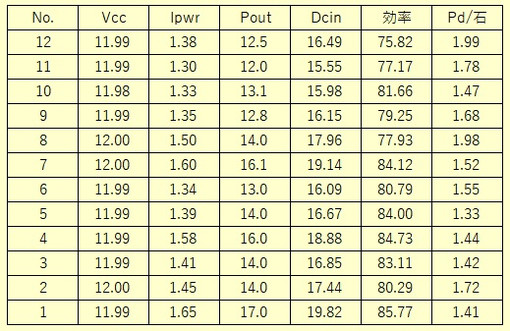

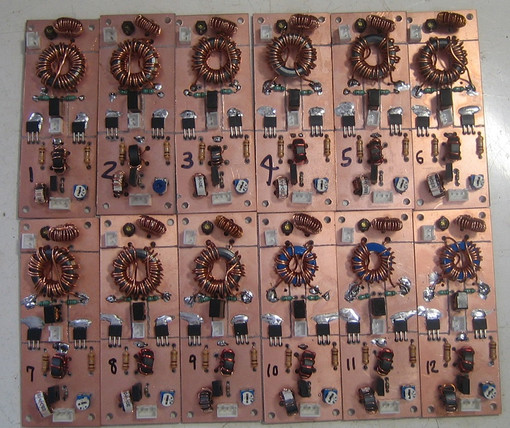

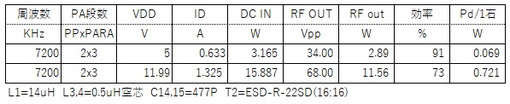

完成した12台のパワーアンプとそのデータです。 番号は、前回のナンバーをそのまま使いましたので、出力順には並んでいません。 LPFを廃止したら、全部ではありませんが、出力レベルの傾向が逆転した感じです。

完成した12台のパワーアンプとそのデータです。 番号は、前回のナンバーをそのまま使いましたので、出力順には並んでいません。 LPFを廃止したら、全部ではありませんが、出力レベルの傾向が逆転した感じです。

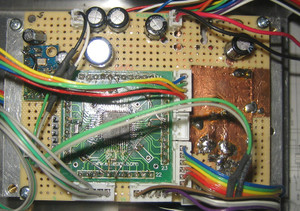

確認を始めたところが、途中で、自作の電源が壊れ、12Vの電圧が38Vまで上昇し、電源用IC,DDS IC、LCDを壊してしまいました。 この事故の為、また、検討がストップする事を避ける為、電源の壊れた原因を突き止める上でも、破壊したICやLCDの交換を行い、中には、発熱で、銅箔パターンが2cmくらいの長さで焼失したりしましたが、なんとか正月休みと次に3連休を使い回復できました。

電源が壊れた原因は12V8Aの負荷に1分間以上耐える事が出来ず、シリーズ制御用のTRがコレクタ・エミッタ間ショートで、約38Vの電圧が12Vラインに加わった為と判りました。 この時のTR 2SA1943のコレクタ損は248W、3石構成ですから、1石当たり均等に流れると83Wの消費になり、ぎりぎりセーフの範疇ですが、3石のバランスが崩れ、特定の1石に損失が集中した結果、壊れたみたいです。 とりあえずはリニアアンプ用に用意したAC/DCコンバーターを使って検討し、時間が出来たら電源の修復を行う事にします。

電力合成を行う上で、各パワーアンプの出力端子での位相を確認してみました。

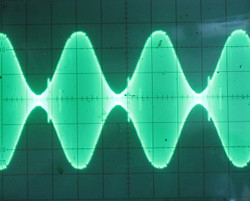

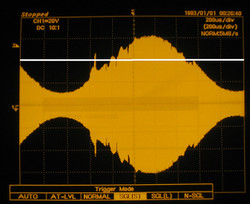

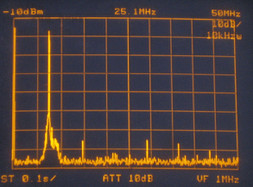

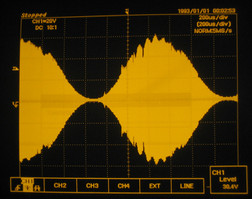

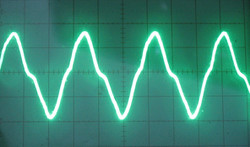

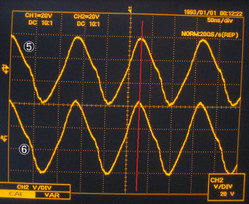

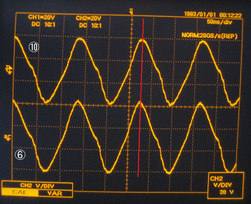

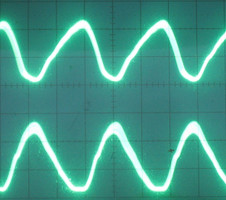

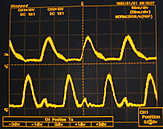

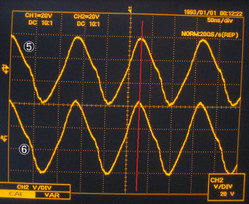

左上がNo.5とNo.6 の比較、右上が、No.10とNo.6の位相比較です。 垂直の赤い線は両方の波形のピークを直線で結んだもので、この線が傾いていれば位相差があると判断できますが、問題はないと言える状態になっていました。

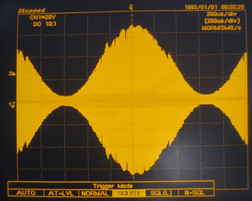

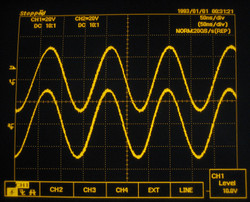

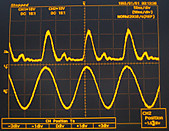

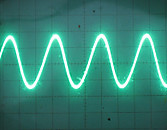

左は、4つのアンプを合成した後の出力波形ですが、大きな歪はなく、実際の送信機では、この後に6次のBPFを通してアンテナに接続されます。

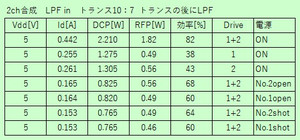

①②③④の合成確認が終われば、次に③④⑤⑥の4台の確認を行い、以後2台ずつずらしながら最後の⑨⑩⑪⑫の組み合わせまで確認した結果、4台合計の最小出力は30W、最大出力は40Wとなり、最大出力時の全消費電流は7Aとなりました。 一応全ユニット合成が出来る事は確認できました。

単体での効率は70%台のアンプでしたが、4台合成時の概略効率は45%くらいまで落ちてしまいました。

放送局の設備でも真空管式より20%以上の効率とのことなので、半導体のPWM機より効率は悪いのでしょう。

つぎは、組み込みを行い、全12台の合成テストをトライします。

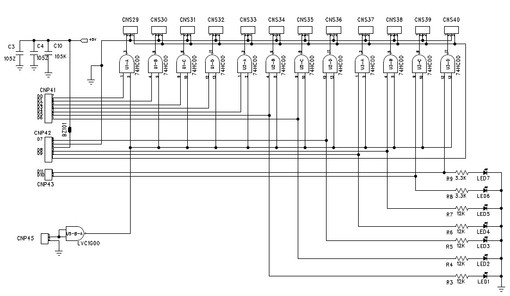

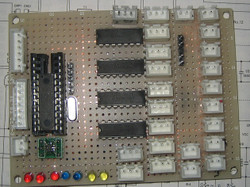

12台のアンプを実装完了し、8bitのデータを1から手動でアップしていきます。 電力合成トランスのインダクタンス分をキャンセルさせる為の直列共振回路がうまく動作しないので、コイルの巻き数を減らし、50Pの固定コンデンサと50Pのバリコンで調整出来る範囲に納めました。 テストモードで、ADのカウント値を上げて行き、63までは順調に増加して、64の時、出力がゼロになりました。 6bit目のラインが動作していないようです。 調査した結果、MSB側の3bit-7のデコーダーが動作していません。 原因はPIC16F84Aが死んでいました。 このマイコンに過電圧が加わり死んだみたいです。 部品箱をひっくり返して、同様なマイコンを探すと、PIC16F1827というマイコンが見つかりました。 18pinでI/Oもコンパチです。 早々、マイコンを差し替え、ソフトを改造して、やっと64カウント以上の確認が出来るようになりました。 127で25W、全電流が7A,128で25Wをわずかに超えますが全電流は5.8A。 出力が増加したのに、電流は減りました。 ふしぎな動作ですね。 効率が悪いのもうなづけます。 手動確認は結構時間がかかりますので、ここまで。 これ以上のカウントは実際に変調をかけて行います。

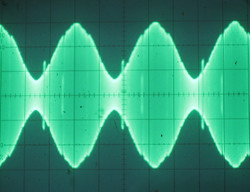

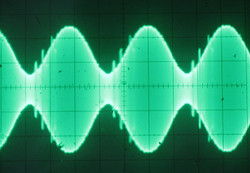

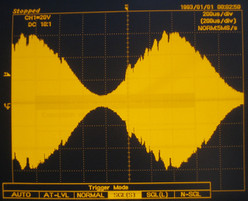

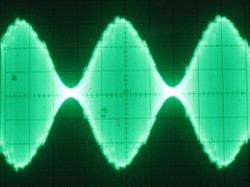

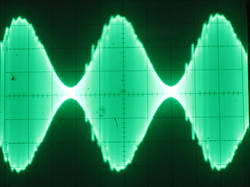

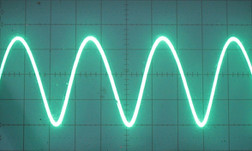

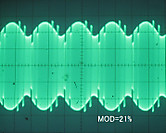

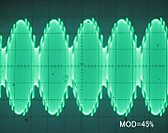

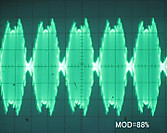

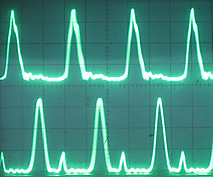

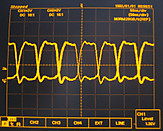

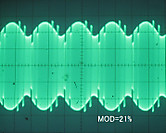

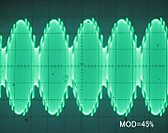

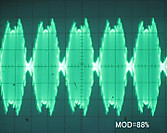

上の波形は1KHzにて変調をかけたもので、見るも無残な波形をしております。 まだ、プリディストーションはかけていません。45%の波形までは、なんとかなるか。と考えますが、88%の変調は、ちょっと難儀しそうですね。 また、変調度に関係なく、周期的に発生しているパルスノイズも気になるところです。

修理完了したデコーダーの回路図 RFADC_AMPx12-4.pdfをダウンロード

デジタル方式 AM送信機 再構築 へ続く

INDEXに戻る