E級高効率RFアンプの実験

<カテゴリ AM送信機(デジタル方式) >

7MHzで10Wくらいの安いアンプを作ろうとしています。 目標は、効率80%以上のE級アンプです。 首尾よく、試作に成功したら、これを十数台作り、電力合成して、AM送信機に仕上げる魂胆です。

参考にしたのは、E級アンプの実践的なレポートのある、JK1LSE OM のブログです。

まずは、効率90%のE級アンプへの挑戦です。 これが意外と難しい。なかなか90%の大台が出ません。 とりあえず、80%台がでましたので、ここで一区切りし、次のstepへ進む事にしますが、以下そこまでの経過です。

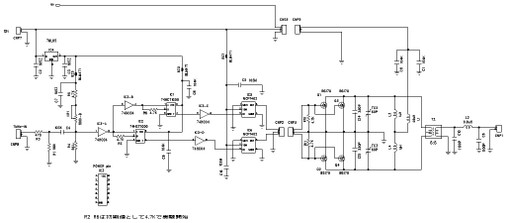

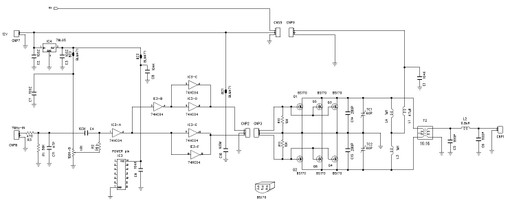

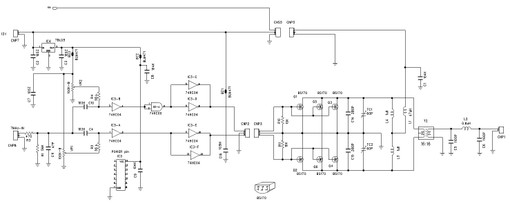

上の回路図が今回検討開始に当たり、設定した配線図になります。 終段はBS170の2石パラレル、プッシュプル(2x2)形式で、E級アンプを構成させます。 そのドライブ回路は、FETゲートドライバーのMCP1402Tで、電源電圧を12Vにして、BS170をフルスィングします。 その前に、CMOSゲートによりデッドタイム生成を行い、ファイナルのプッシュプル回路のFETが同時にON する事を防止します。 さらにその前段にDCバイアスを調整して、7MHzの矩形波のデューティ比を調整できるようにしてあります。 7MHzの源信号は、以前作成したDDSから4.5Vppでドライブします。

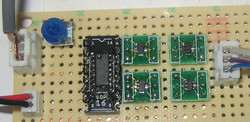

左は、そのゲートどライブ回路を蛇の目基板に実装したところです。 VDD5Vにて、70%台の効率を出せるのですが、このゲートドライバーのMCP1402Tがかなり熱くなります。 コアや巻き数を変更しながら、電源電圧も5V、10V、12Vと変化させているうちにICが壊れてしまいました。 とりあえず、ICは4個購入してありましたので、修理交換して、各定数の最適値を探して、80%台の効率が得られる状態になりましたので、12Vで1分くらい動作させた結果、今度はBS170、4石を道連れにこのゲートドライバーも壊れてしまいました。 データシートを見る限り、電源電圧12Vは全く問題ないはずですが、ファイナルの電源電圧を12Vにすると、たちまち壊れてしまいます。 原因を調べようにも、すでに手持ちのICは全滅。 やむなく、手持ちのTC4426に改造して、再検討開始です。

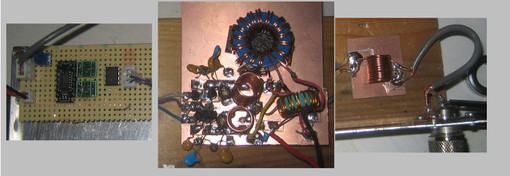

ただし、TC4426を以前RSで買った時は90円でしたが、現在は246円以上していますので、もっと安いICへ置き換えが必要です。 置き換え品は後で探す事にして、実際に組みあがった回路は以下のようになりました。3枚の写真の間はリード線や同軸ケーブルでつながれています。

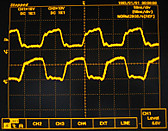

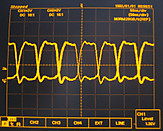

上の波形は左から、ゲート端子の電圧(10V/DIV)、ドレイン電圧(20V/DIV)、ドレンイン電圧とフィルター後の出力波形(20V/DIV)です。

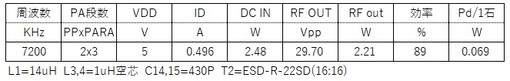

見ての通り、ドレイン電圧が同じ形をしていません。 回路を非対称に作った事が影響しているかもしれません。 このような波形ですが、実測データは下のようになりました。

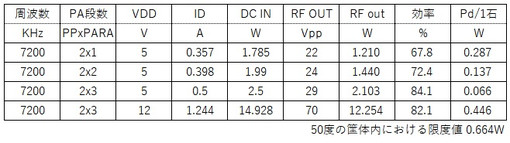

VDD 5V、12Vいずれの状態でも80%台の効率は確保できましたが、12V電源の場合、FET1石にかかるPdは、2x3の場合で、0.446Wとなりました。 これは、データシートから割り出した筐体内温度60度の許容値0.599Wの74%で実用レベルです。 ちなみに、2x2の場合、1石当たり0.669Wとなり、これは許容値ギリギリで、余裕が有りませんので、交信中に壊れる確率が高いです。 2x2の構成で放熱板を追加するより、FETを2石増やして2x3にした方が安くつきそうです。

このアンプを8bitのDAコンバーター用に使うと、最低12台、欲を出して、bit数を10bitまで上げると最低21台作る必要があり、大きなフェライトコアを使った現状アンプでは、フェライトコアの材料代だけで、600円くらいしますので、21台作ろうとしたら、12,000円くらいになってしまいます。 そこで、コストダウンの為に、L1を手持ちのチョークコイル(100個くらい在庫)に変更し、T2のコアも、一回り小さなフェライトコアに変える実験を行いました。 左がその写真です。

出力トランスに使うフェライトコアをESD-R-22SDに変えると、150円くらいで手にいりますので、21台分で、3000円と少しで実現できます。 そして、検討の結果、効率は89%まで向上し、コストダウン出来た上、効率も上げる事ができました。

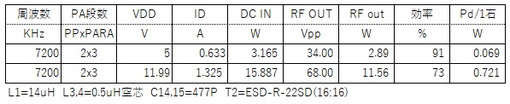

1uHの空芯コイルは基板から10cm以上離れた場所で約1uHでしたが、写真のように基板に密着させた状態では0.89uHしかありませんでした。 そこで、L3とL4を0.5uHにした時のデータを取ってみました。

VDD5Vの時は91%の効率となりましたが、12Vの時は73%まで悪化しています。 やはり、L3,L4は1uH前後でないとダメ見たいです。

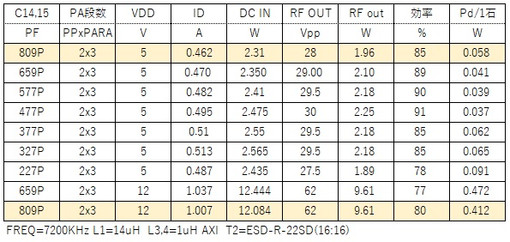

そこで、1uHのアキシャルインダクタに変更してみました。 このインダクタの特徴は小型であることと、そこそこのQが確保できる事です。 秋月で1本7円で販売されていました。

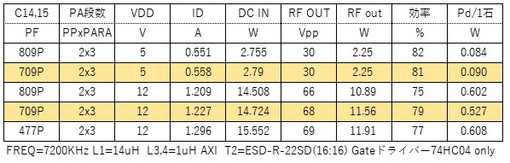

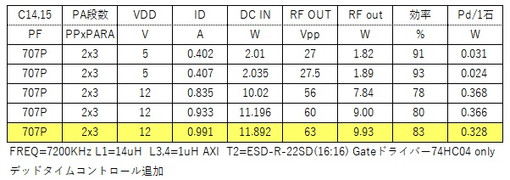

7200KHzに周波数を固定して、C14と15を変化させた時のデータです。 5Vの電源では、91%の効率をあげる条件がありますが、同じ条件で、12Vにすると、70%くらいまで落ちてしまいます。 表の中で、色分けした条件なら、なんとか80%をキープします。 80%でも、Pdは余裕がありますので、あまり欲張らない方が良いかも知れません。

今までの実験経過から、部品のレイアウトを整然と行い、リンギングの発生を抑える事が、安定に高効率を得る条件のようですので、ゲートドライブ用のICが確保できた時点で基板を作り替えてみる事になりそうです。

ゲートドライバーのICと変換基板を手配できましたので、さっそく実装してみました。 ところが、ICの仕様を読み間違えたようで、入力レベルが5V以上必要なICでした。 また、TC4426を使って、Vddを12Vまで上げると、異常信号でAM変調されます。 出力段の信号がTC4426の入力にフィードバックされているような波形で、Vddを下げると、小さくはなりますが、ゼロにはなりません。 そこで、このゲートドライバーは止めて、74HC04のみでFETのゲートをドライブしてみました。 すると、異常信号によるAM成分は消えてきれいになり、かつTC4426の時より出力が出るようになりました。 以降、74HC04のみで進行する事にします。

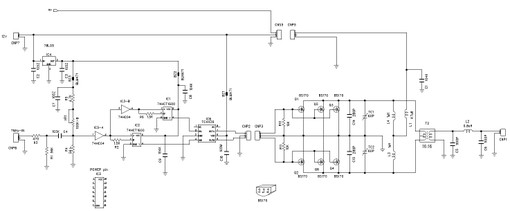

配線図は以下です。

上の表は、74HC04オンリーで、1uHのアキシャルインダクターを使用した時のデータです。

Vdd=12VでC14,15が709PFのとき、79%の効率で11Wを出力し、Vdd=5Vの時の効率が81%です。 12Vと5Vの時の効率があまり変わらないという事は、このアンプを10数台電力合成した時の個々の出力を、Vddを変える事により簡単に直線的に変更できることになりますので、便利です。 左の写真は、アキシャルコイル実装状態で、基板の中がかなりすっきりとなりました。

従来、プリント基板の作図を行う場合、プロ用のソフトを使っていましたが、このプロ用のソフトはWindows XP用で、それ以降のOSでは、ライセンスの関係で動かないという問題がありました。 XPがインストールされたデスクトップのPCとHD仕様のディスプレーは有るのですが、この古いPCを引っ張り出しても、狭い机が、いっそう使いにくくなりますので、最新の無償のソフトを探す事にしました。 そして、見つかったのが、KiCADという、私が以前使っていたプロ用のソフトと似たようなアプリが今、世界中で利用されている事を知りました。

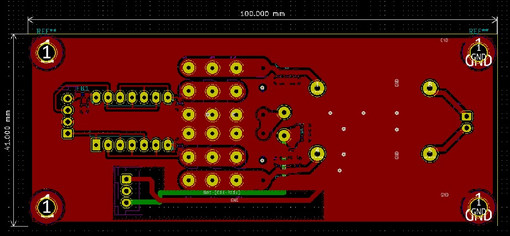

さっそく、このソフトをインストールして、このE級アンプの基板の作図を始めました。 初めてのソフトでも、インターネットで検索すれば、たちまち、操作方法のアドバイスがあり、約5日間で、配線図、基板図用の、オリジナルのシンボルやフットパターンを追加しながら、基板図ができあがりましたので、できた基板図の通りカッターとリューターで銅箔をはがし、1枚だけ基板を試作しました。 下が、KiCADで作図した基板図です。

左は、上の基板図の表面のみカッターで銅箔を削り、手作りした両面基板に部品を実装したところです。 FETとコイルとコネクター以外の抵抗、コンデンサは1608のチップで作りましたので、見た目は、かなりすっきり仕上がりました。

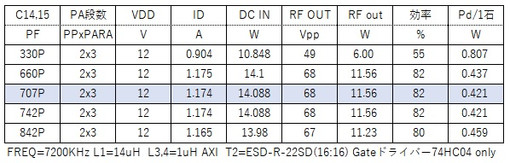

作図した基板には、FETゲートドライバの74HC04のパターンも用意してありましたが、今までの手作り基板と兼用する為、ゲートドライバーは、別基板に実装し、この新作基板は、BS170によるファイナル部分だけを実装しました。 いままでの回路と異なるところは、プッシュプル回路の配置が対称になったことです。 そして、12Vで測定したデータは以下のようになりました。 共振用コンデンサは707Pがよさそうです。 出力は11Wを超え、かつ1石当たりのPdも許容値内ですので、これをベースに量産する事にします。 このコンデンサの容量組み合わせは330P+330P+47Pです。 全てCH特性のチップコンデンサです。

この表の中にある842Pの状態で、エージングをしていると、約10分でFETが3石すべてがオープン状態で壊れてしまいました。 壊れた直後のFETの温度は、触れないくらい熱くなっていました。 1石当たりのPdは許容値内ですが、この数値は6石のFETにPdが均等に割り振られたもので、実際のPdは最小と最大で2倍くらいまでバラツクと想定されます。 この時の最大Pdは0.612Wくらいと予想され、60度の限界値0.599Wを超え、この為、1石がNGとなると、残りの2石で全体のPdをカバーする事になり、次々と壊れたものと思われます。 プッシュプルのもう一方の3石は無傷でした。

そこで、最初実験したデッドタイムコントロール機能を再度追加し、出力と効率を制御する事にしました。

デッドタイムコントロール回路を追加した回路図を下に示します。

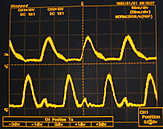

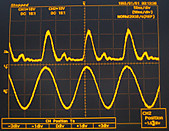

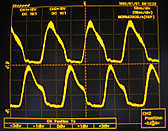

左上から、終段のゲート電圧、終段のドレイン電圧、そして、LPFの出力の波形です。 基板のシンメトリ性が功をはくし、ドレインの波形も大幅に改善しました。 そして、デッドタイムを色々調整した結果、以下のデータとなりました。

黄色の状態でエージングを実施し、1時間OKでした。

今回の回路構成は、10台以上のアンプを直列に接続して、電力合成する必要がある為、出力整合回路と、出力設定機能を兼ねる為に、巻き数の多い絶縁トランスを採用しています。 この構成のE級プッシュプル回路の例が見つからず、製作中のアンプがほんとうに正しいのか判りません。

このE級プッシュプル回路の構成は、この記事の没頭で紹介した、JK1LSE OM のブログや周波数が異なりますが、トラ技の記事とも異なります。 多分、それが影響しているとは思いますが、C14,15とL3,L4の共振周波数の関係がこれらふたつの記事と一致しません。 ちなみに、L3,L4,L1の交点から、0.1uFでGNDへ落すと、C14とL4及びC15とL3の共振周波数は、7.2MHzより少し高い周波数の時、効率最大となりますが、効率そのものは最大でも80%でした。

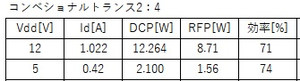

左は、コンベンショナルトランスを使った時の出力データです。 トランスの巻き数は2:4ですので、プッシュプル回路の負荷インピーダンスは12.5Ωになります。 そして、70%台の効率です。 この効率は、LPFの後で計算した場合、だいたい、どのインターネット記事も似たような数値で、一応世間並みの動作はしているようです。 この回路は、今までの回路に比べて出力は小さいですが、結構安定して動作し、出力波形もかなり綺麗です。 ただし、これを採用するかどうかは、電力合成の実験で決める事になりそうです。

今回のAM送信機は大小の出力を電力合成をするのですが、その合成のノウハウは公表されておらず、自分で実験しながら、試行錯誤するしかないようです。

高周波直列電力合成(7.2MHz) へ続く。