カテゴリ<天体写真 ポータブル赤道儀 自作 ステッピングモーター>

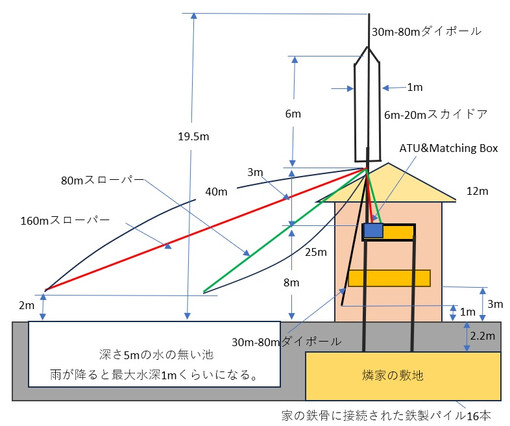

多分、50mmくらいのレンズなら赤道儀につけたファインダー越しに北極星を狙って極軸調整しただけで60秒くらいの撮影は可能ではないかと考えますが、さすがに200mm(デジカメなら300mm相当)のレンズの場合、極軸望遠鏡が無ければ無理だろうという感触は前回の実写でなんとなく判りました。 しかし、ここで諦める訳にもいかず、インターネットでドリフト法に関する情報を読みあさった結果、これなら極軸望遠鏡が無くても星を点にとらえる事が出来るかも知れない。

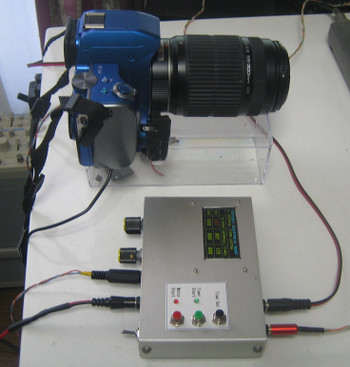

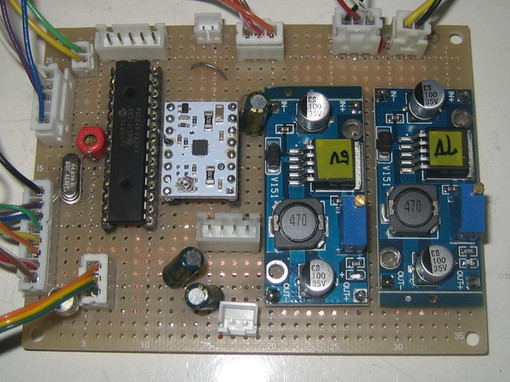

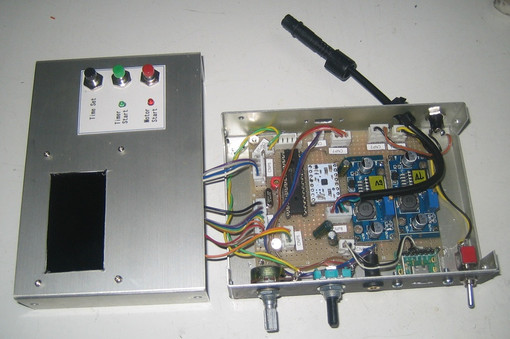

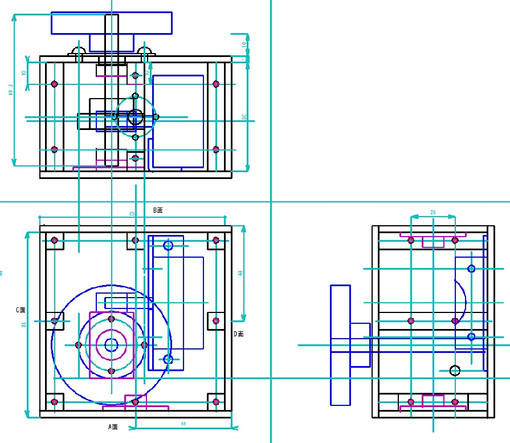

そこで、今回の自作赤道儀のコントロール回路にV字型の線を自動的に取得するためのプログラムを追加する事にしました。 赤道儀の動きとしては、通常の追尾速度で10秒くらい動作させ、次に60秒間だけ通常の回転方向で回転速度を4倍にし、続けて逆方向に60秒間4倍の速度で回転させ、この間、シャッターを開放状態にしておけば、デジタルカメラのなかにVの字の光跡が残るというもの。 撮影後、その場でカメラの中をPCで覗き、Vの字がIの字に変わるまで極軸の調整を行うようにしたい。

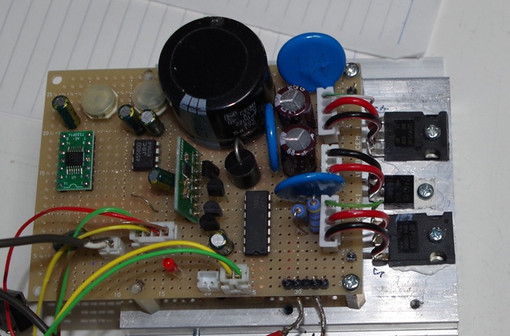

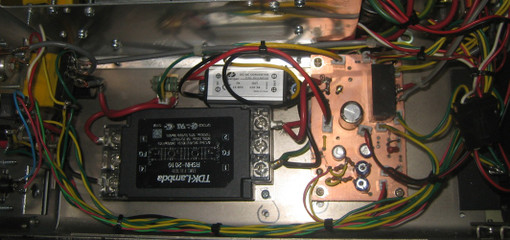

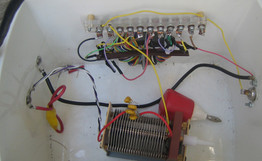

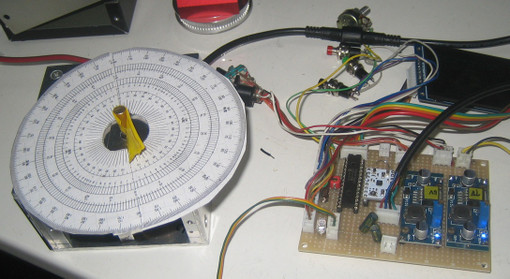

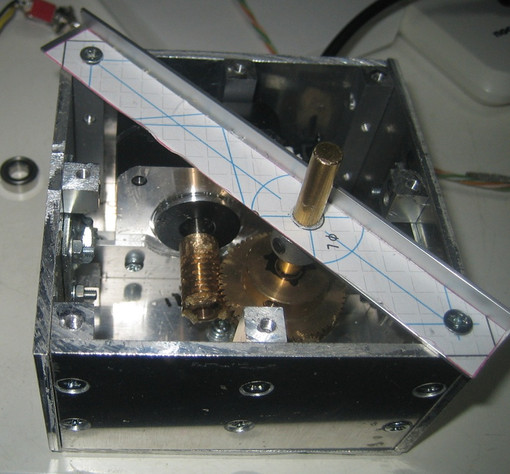

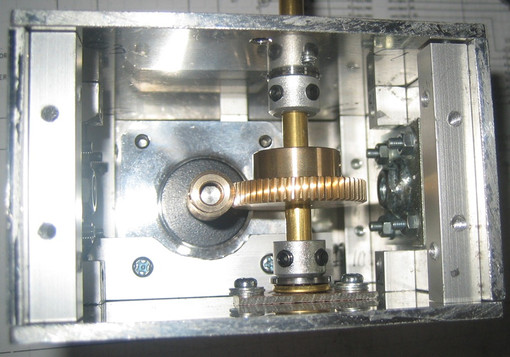

赤道儀の駆動はステッピングモーターで行っているので、簡単にプログラムを追加できます。 1日でプログラムの改造を終え、部屋の中で、赤道儀の動きをチェックする為に、回転速度を60倍にして通常の4倍速でチェックすると、通常の回転方向の場合、15秒で15度ほど回転しますが、逆方向の場合、15秒で30度ほど回転してしまいます。 過去、ステッピングモーターの正転、逆転をランダムに繰り返す必要のあるATU(自動アンテナチューナー)を作成し、速度が変わるような問題は一度もなかったのにと焦りました。 原因は、モーター停止時のタイミングでした。

今回の赤道儀は、ステップ数を数える必要がないので、現在のステップ信号のパルスがH/L関係なくモーターを停止させていました。もしかしたら、このパルスがHの時モーターを停止させると、次の起動時に停止した時の状態と異なることから、マイクロステップのシーケンスがくるってしまうのでは?と気づき、モーターを停止する場合、必ず、ステップパルスがLになるまで待って停止させるプログラムに変更したら、この異常現象は完全に無くなってしまいました。電流制限100mAから500mAまで変化させ確認しましたが、いずれも異常なしでした。最終的に電流制限は250mAに設定しました。

正転、逆転の基本動作が出来るようになりましたので、Vの字パターンを記録するために、全体のシャッター開放時間をマニュアルで設定する手段、通常スピードの何倍で回転するか指定する手段、描かれたVの字の線の始点のマーキング、線が重なってIの字になっていることを容易に判断するために、正転時の光跡の長さより、逆転時の光跡を長くする手段をプログラムで作成しました。

この正転と逆転時の光跡の長さは正転と逆転の時間が同なら、必ず逆転時の長さが長くなるのですが、あまり長くなると始点と終点の距離が離れてしまい、Vの時の開き角度が小さくなります。すなわち、IなのかVなのか判定がむずかしくなる事を避ける為に逆転時の長さを予め計算された値に調整します。 また、これに使用するカメラであるK20Dはシャッター開放状態の撮影では撮影終了後、撮影時と同じ時間をかけて、ノイズリダクション処理があり、通常のカメラの2倍の時間がかかってしまいます。 そこで、一般的には100秒くらいで光跡を取得していますが、これを30秒くらいから初めて、ほぼIの字になったとき60秒以上で再確認するようにするつもりです。

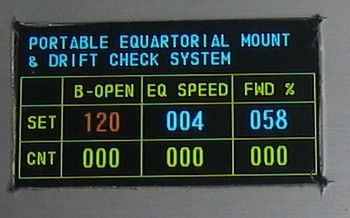

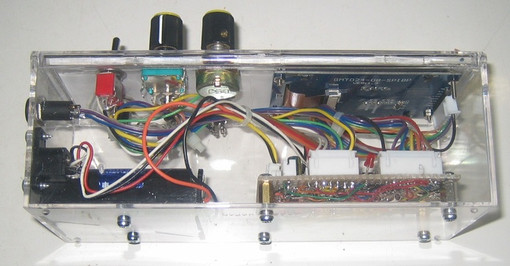

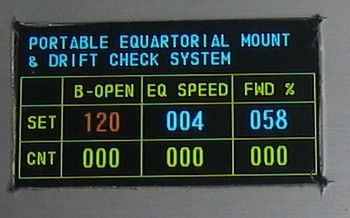

改造したプログラムは、TIME SETキーを押しながら電源SWをONするとドリフトモードになるように設定しました。 左の画像はこのドリフトモードで立ち上げた時のLCD画面です。 一番左のB-OPENの下にある数字は、120秒間シャッターを開放する事を示しています。この数値は1秒から255秒まで可変できます。

真ん中のEQ SPEEDの下にある数値は赤道儀の回転速度を通常の何倍の速さに設定するかを示します。この数値は2倍から10倍まで可変できます。実際に使ってみて範囲が狭いようでしたら、拡大するかも知れません。右側のFWD %の下の数値は順方向に回転させる時間の比率を予め計算し、その結果を表示しています。この表示の例では全シャッター開放時間120秒のうちの58%(69秒間)順方向に送り、逆方向には残りの51秒間送ることになります。この比率は順方向の光跡より、逆方向の光跡が約22%くらい長くなるように計算されています。

TIMER STARTキーを押すと、通常の追尾速度で赤道儀が回転し始め、10秒間シャッターを開放します。これは光跡の始点を作る作業です。10秒経過したらシャッターは開放のままB-OPENで指定された期間、プログラムされた動作を行いトータル130秒後にシャッターは閉じます。

ここまで準備して、いざドリフト法にファーストトライです。

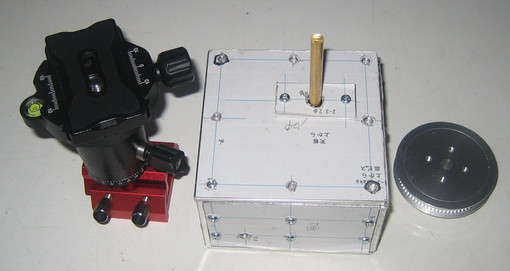

今夜は南向きのベランダから星を撮影しますので、まず三脚を水準器で水平にします。次に、先日北極星を狙ったときの高度角に黄色のテープで印をつけていましたので、それにピタリと合わせて高さ方向はきっちり固定しました。

次に、赤経の南中付近にカメラを向けますが、目で確認できるめぼしい星が光害の為見えません。やむなく適当に水平方向を決めて、30秒間の光跡を確認し、何回も繰り返しながら60秒間の光跡でほぼ正転と逆転の光跡が重なった角度を決めました。 ただ、この60秒の光跡で、とりあえずこれくらいで良いかと諦めるまで2時間かかっていました。 続いて東側の空に見える星を狙って、60秒の光跡を確認したら、1回目で正転、逆転の光跡は重なっていましたので、出来た!と適当な星を1分と2分と3分で追尾撮影をおこないました。 この終了まで2時間20分かかっています。

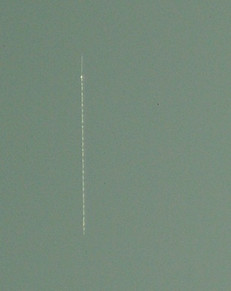

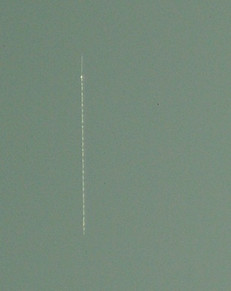

左下が南方向に適当にカメラを固定して最初に撮った30秒間の光跡です。あてずっぽにしても、かなり外れた状態から開始する事になりました。真ん中は60秒の光跡です。暗闇の中で光るPCの画面を見て、光跡が一致したと判定した画像ですが、拡大するとまだずれていました。右側が先日の北極星で上下方向の角度を決めた時のままで撮った東の空10度くらいの高さに上った星の光跡です。 カメラの向きがいずれも水平からずれていましたので、光跡の角度もバラバラです。

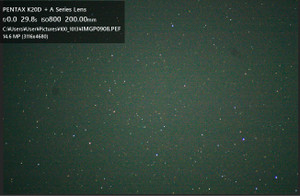

この状態でシャッター開放2分(左)と3分(右)で撮影した星が以下の写真です。

2時間もベランダに立ちっぱなしでトライしたドリフト法でしたが、カメラの近くに置いたノートPCの画面では、正転逆転の光跡は一致していると判定したのですが、機材を撤収して改めて光跡を拡大して確認したら、いまいち追い込み不足があり、結果として2枚の星空の写真は星が点になりませんでした。 また、最初に撮影した1分の画像は3分の画像より星の流れが大きく、この最初の画像だけ、星の流れが大きいのは2回目です。 なにか特別な原因がありそうです。

以上の結果から、まずDriftのプログラムの中の、最初の始点を作る時間を10秒から5秒に変更しました。 撮影完了後、再度シャッター開放時間と同じ時間だけ待つ為にカウント機能を入れました。 このカウント値がLCDに表示されますので、前回よりイライラして待つ事がなくなりました。前回、最初の追尾撮影で追尾に失敗して、星が線状になる原因は、赤道儀の回転軸のあそびが原因でした。一旦追尾を止めて、カメラの向きを変え再度追尾を開始しても軸のあそびの分だけ赤道儀は回転せず、あそびが解消されたら追尾を開始しますが、このあそびの範囲を抜け出すのに1分くらいかかっていました。 対策として、再度モーターの位置調整を行いあそびの部分で赤道儀が回転しない時間を30秒くらいまで縮めましたが、これ以上の改善が出来ないので、ドリフト操作をしない時でも赤道儀は星を追尾したままにする事にしました。

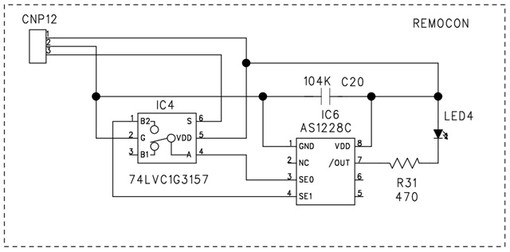

回路図 EQ_Mount_sch_2.pdfをダウンロード

マイコンプログラム PEQ_Mount_201.cをダウンロード

フォントプログラム Font9.hをダウンロード

Font12.hをダウンロード

そして、数日後、まず南中位置付近での水平方向の合わせを行い、次に東方向で垂直方向の合わせを行った結果が以下の画像です。 特に水平方向は光害のため、2等星の星も見えない状況でしたので、目視では見えない暗い星の光跡を見て、判定したのですが、左下の画像のように、改めてPC画面で拡大してみるとまだVの字状態でした。 垂直方向はOKみたいです。撮影時間は左右とも60秒ですが、右側の背景が明るいのはパチンコ屋のネオンの性です。

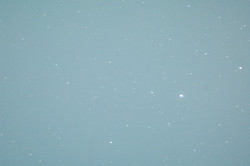

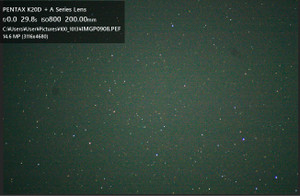

以上の極軸合わせ結果により撮影した星の画像は左から30秒、60秒、下の段の左から90秒、120秒です。

90秒までが限界ですかね。 120秒の星は円弧状に写っていますので、追尾エラーにカメラの回転まで加わった模様です。 雲台の締め付け不足が原因と思われます。

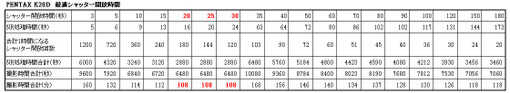

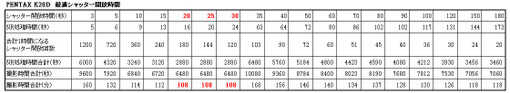

今回使用しているカメラ PENTAX K20Dの場合、星を撮影する場合に致命的な欠陥があります。 シャッター開放時間が0.3秒を超えるとノイズリダクション(NR)機能をOFFできなくなり、例えば10秒間シャッターを開放した後、ほぼ同じ時間をかけてNR処理をする事から、この間、次にシャッターON出来るまで待たねばなりません。 実際NR処理時間にどのくらいかかっているか調べてみました。

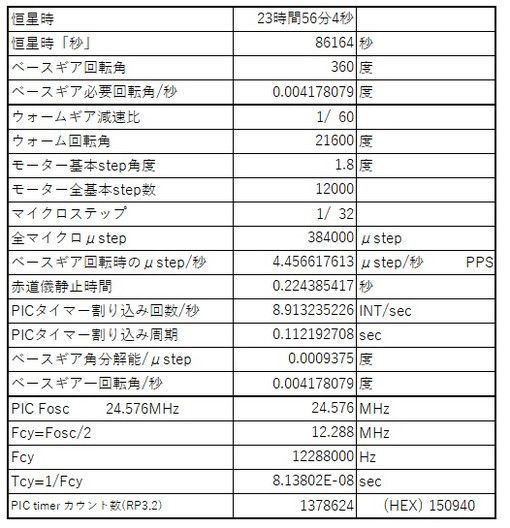

表をクリックすると拡大します。

実際のカメラを使い、3秒から180秒までのNR処理時間の計測結果です。 そして、シャッター開放時間が合計して60分になる時の、NR処理時間とシャッター開放時間の合計を計算したものです。 シャッター開放時間とNR処理時間に比例関係は有りません。 一番効率の良いシャッター開放時間は20,25,30秒でこれ以下も以上もトータル必要時間は多くなります。 特にシャッター開放時間が35秒になると急にNR処理時間が長くなり35秒の時が一番効率が悪くなっています。 30秒と35秒の間にこの効率悪化のしきい値があるので調べてみたら33秒から悪化する事がわかりました。 余裕を見て最長30秒がベターと判断します。 いくら長時間のシャッター開放にトライしても32秒を超えた途端、撮影効率が大幅にダウンする為、レンズの焦点距離に関係なく30秒のシャッター時間で星が点に写れば良いという事になりました。

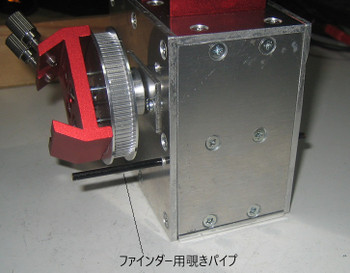

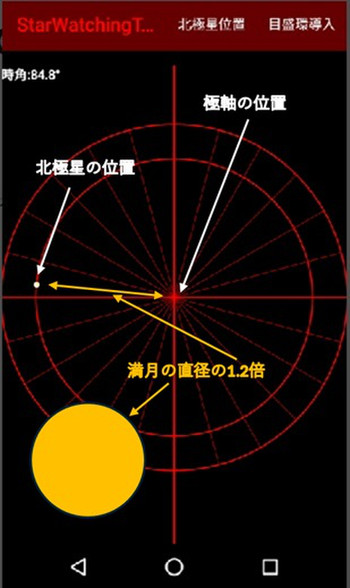

北極星を見ながら極軸合わせをした場合も、ドリフト法で極軸合わせした場合も30秒のシャッター時間なら、極軸合わせに45分もかける必要はなさそうです。 ドリフト法の場合でも垂直方向は、三脚を水平に合わせ、北極星の高度に合わせた角度に固定して水平方向だけ合わせるという手抜きでも問題なさそうです。 この記事の最初の左側にある星の写真はレッドドットファインダーのみで北極星をターゲットに、StarWatchingToolsで確認した北極星の時角を考慮して極軸合わせを行い、ベランダからほぼ天頂の星を赤道儀で追尾しながら30秒間のシャッター開放で撮影し、その時のRAW画像をRawTherapeeとういうアプリで加工したものです。 200mmのレンズでも星は点に写っていました。

以後20秒から30秒の範囲で連続撮影する事にします。

今回の極軸調整時間は、ベランダに機材をセットアップするのに15分、極軸を水平、垂直両方とも合わせ完了まで45分、最後の星空撮影が12分くらいかかりました。 一番時間を食った作業は、ドリフト撮影時、星が見えない為、カメラに映りそうな星を探す時間でした。 私の住む街は大して大きな街でもないのに、家の近辺に大きなパチンコ屋と戸建ての世帯数を上回る世帯数のアパートがあり、建物の数は戸建てとアパートがほぼ同数で、アパートの共同で使う通路や階段は終夜こうこうと照明を点灯する事を法律で義務付けられている関係から、とにかく星は見えません。

ドリフト法によるVの字のCCW(逆転)方向の光跡の長さをCW方向の122%くらいの長さに設定したつもりでしたが、実際はばらついて逆に短くなっているのが多い状況でした。 原因を調べると計算式の間違いと、赤道儀の軸のあそびの性でした。計算式は次回から修正されますが、軸のあそびはそのままです。なるべく赤道儀の軸が反転する場合、あそびが影響しないようにカメラの重心を設定する事にします。

修正したプログラム PEQ_Mount_202.cをダウンロード

追加したヘッダーファイル NRtimeK20D.hをダウンロード

次はいよいよ光害の無い場所に移動して目標を定めての撮影になりますが、いつできることやら。

ラッキー!

昼間、快晴で星の撮影が楽しみな日がありました。 夕方6時半ごろ、レモン彗星が撮れるかも知れないと、北側のベランダから西の空を見ても、彗星どころか恒星も全く見えません。 北極星はかすかに見えていましたので、極軸合わせを行い、恒星追尾を行いながら北西から西の空に80mm望遠レンズを向け、30秒のシャッター時間で位置を変えながら12枚撮影しました。撮影しただけのRAW画像には星は1個も写っていないのですが、RawTherapeeで黒レベルとコントラストを調整して薄暗い星影をあぶりだした結果、1枚だけそれらしき影が映っていました。 最初はゴミかと思ったのですが、翌日、インターネットに紹介された10月24日撮影のレモン彗星の尾の傾きとぴったり合致していましたので、レモン彗星に間違いないと自己満足です。

この撮影の後、北東の空から雲が広がり、8時ごろには空一面曇り空となってしまいました。 天気予報では次に晴れる日は3日後だそうです。

アンドロメダ銀河 撮影準備へ続く。

INDEXに戻る