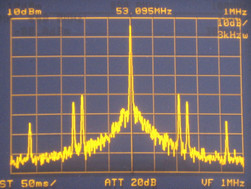

カテゴリー<6m AM >

7MHzの200W AM送信機が完成し、1st QSOも終わりましたので、次のテーマとして6m用PWM AM送信機と決めました。 技術的に目途が有る訳ではありませんが、途中で投げ出す事も可という条件で始める事にします。 ただ、このテーマの最大の問題は、もし首尾よく送信機が完成しても、交信する相手がいないという事ですが。

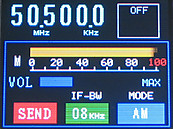

目標は移動運用可能な、電源電圧DC13.8V、キャリア出力10WのAM送信機とします。

以前私が勝手に定義した周波数限界(仕様書上で規定される総遅延時間の逆数)はとても50MHzには及ばず、せいぜい半分くらいしか確保できないようなFETでも50MHzのパワーアンプが可能なのかの実験です。 さらに、FETのゲートの入力容量が小さなFETは、Rdsが比較的大きく、13.8Vの電源では数Wしか出力できないとう現実もありますので、どこかで妥協点を探す必要があります。 これらを加味して素子選択を行います。

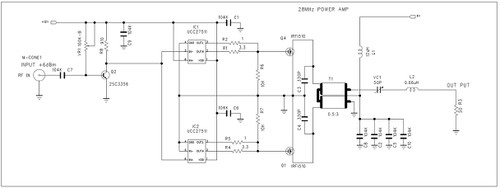

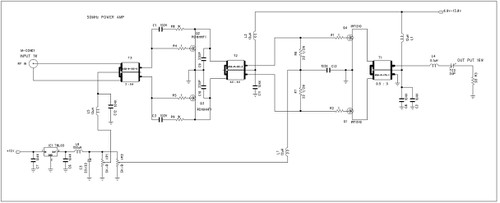

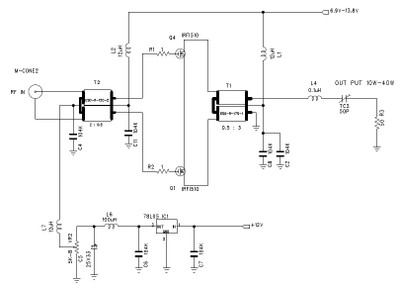

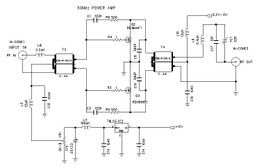

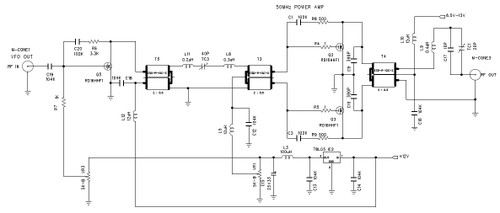

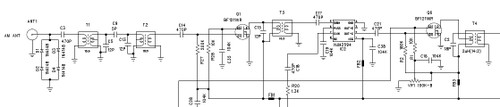

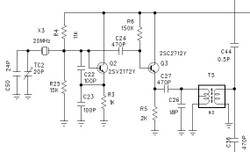

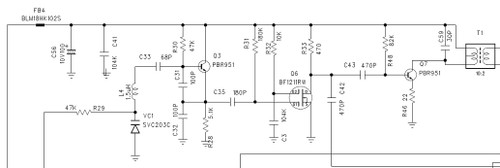

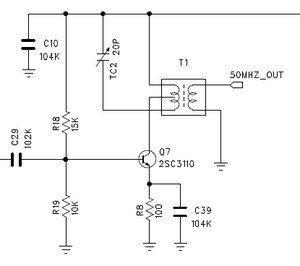

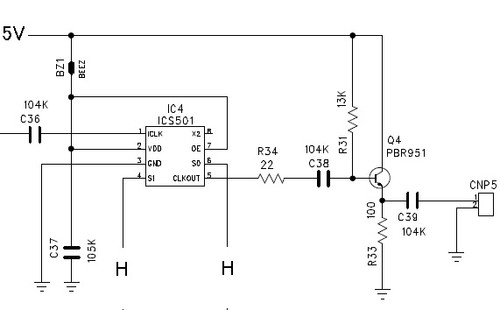

実験用のパワーアンプ回路図でず。AMTX_6m_PAmp.pdfをダウンロード

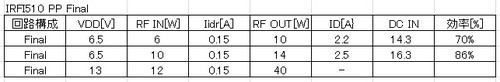

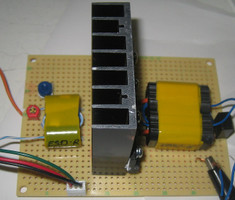

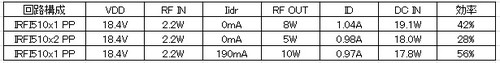

私が手持ちしているFETで、入力容量が小さく、最高の限界周波数、約21MHzのスペックを持つIRFI510(VISHAY製)のプッシュプル(PP)で回路を組みました。

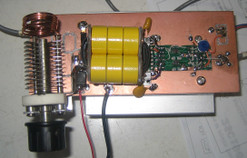

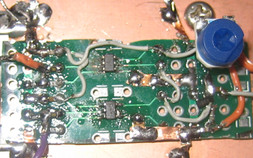

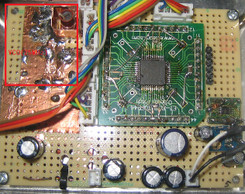

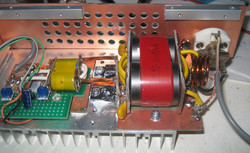

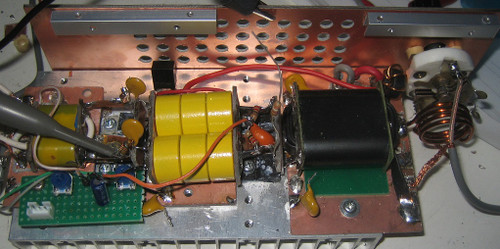

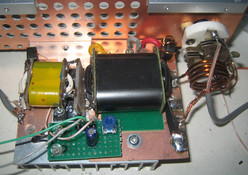

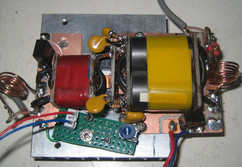

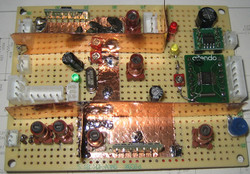

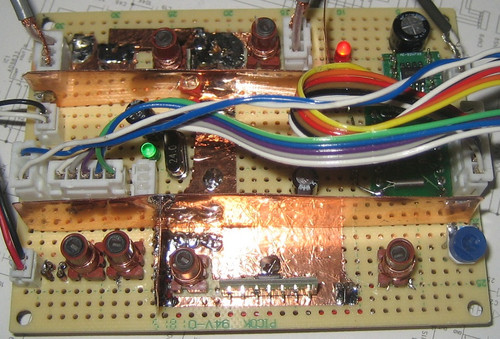

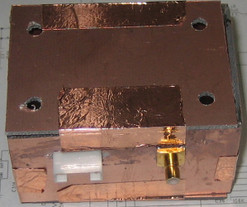

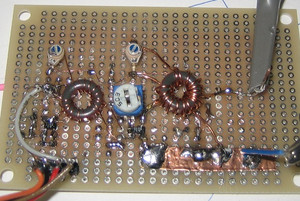

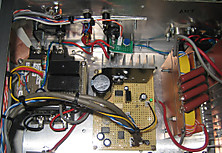

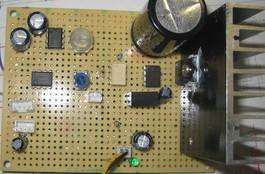

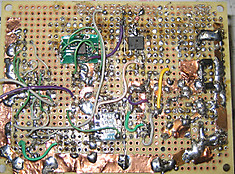

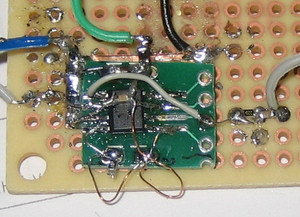

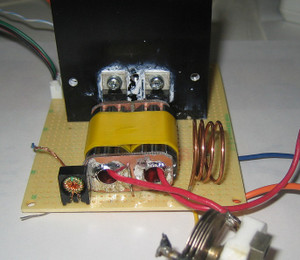

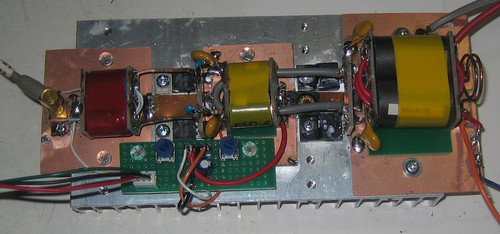

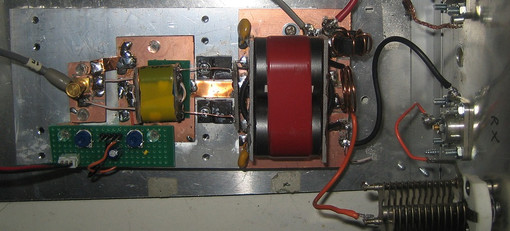

左上がパワーアンプの部品挿入面、右上がそのチップ部品装着面です。部品実装状態は2パラプッシュプルですが、実際はシングルプッシュプルで配線されています。

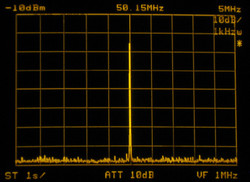

限界周波数が目標50MHzの半分にも満たないFETですが、出力ゼロではなく、なにがしかの出力が得られます。 ただし、E級増幅はおろかC級増幅もできず、かろうじてB級増幅が位相遅延を起こしながら実現できているアンプです。

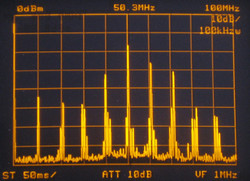

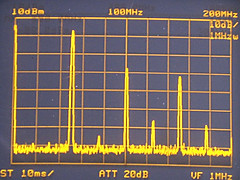

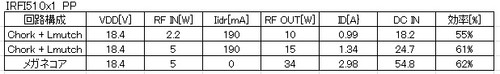

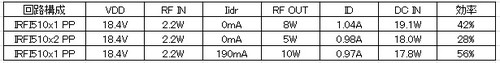

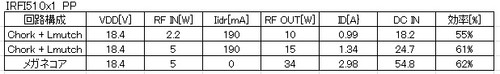

この状態でDC電源が供給可能な最大18.4Vで出力を測定してみました。

入力はFT450からキャリア注入しますが、シングルPPと2パラPPでは入力容量が異なりますので、そこは直列に挿入したトリーマーで調整し、いずれもSWR1.3以下で、2.2Wのドライブです。 ゲートにDCオフセットを加えて、無信号時のドレイン電流がゼロの範囲で、ゲート電圧が少しでも高くなるように半固定抵抗を調整する事にします。

FETシングルのPPドライブで8Wの出力が得られました。 動作モードとしてはB級に近い状態です。 この動作モードのままで、2パラプッシュプルにしたら同じVDDで5Wしか出ません。 多分、入力回路や出力回路の容量が2倍になった事で、ゲートドライブ不足に加え、インピーダンス不整合と最大回路効率の条件のアンマッチから出力不足になった為と考えられます。 ここで、入力レベルを上げても出力は頭打ちでした。

次に、ゲートDCバイアスを調整して、アイドル電流が2石で190mAになるようなAB級動作にすると10Wの出力が得られました。 この動作モードはリニアアンプの世界ですが、目標とする40Wの出力はVDDを37Vくらいまで上げないと実現できません。 出力トランスの2次側巻き数を2ターンから3ターンに増加させると、かえって出力が落ちてしまいました。

1個60円台の安いMOS-FETで50MHzのリニアアンプが出来る事は判りましたが、その時のVDDは車用バッテリーの13,8Vとはかけ離れており、今回のテーマである50MHzアンプは無理と諦める事にしました。 やはりここは移動運用が主になるカーバッテリーで、10WのAM送信機(ピーク40W)の実現に向けて再検討する事にします。

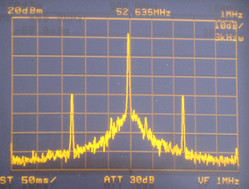

再検討するFETはFT450のドライバー段に使用されている三菱のRD16HHF1というHFパワーアンプ用FETです。

データシートによれば、30MHzに於いて、DC12Vで16Wくらいの出力が得られると書かれており、何よりも現在量産中のFETであるという事です。 それに、価格が370円くらいと、この種のFETにしては、安く売られています。 これを4個ゲットし、今までの基板に実装してみる事にしました。

AMTX_6m_PAmp_RD16HHF1.pdfをダウンロード

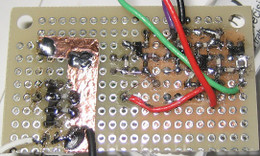

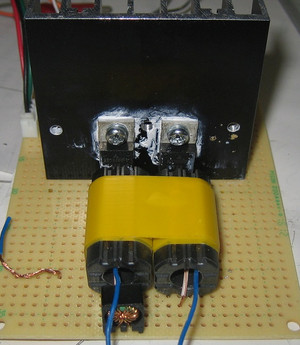

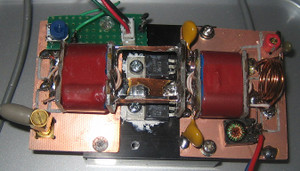

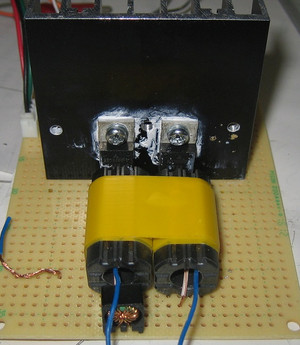

左は、このFETをプッシュプル回路にして、実装した状態です。 このFETのフィンはソースになっており、放熱板に取り付ける時、絶縁の必要が有りません。もちろん、基板上でソースはGNDに接続しますが、3本足のセンターがソースに割り当てられていますので、基板内の配線も楽です。

この実験基板で、VDDを12Vに固定し、50MHzの入力を加えた場合、C級やB級の動作では、出力はほとんど出ません。 データシートでは30MHzの0.6Wの信号でドライブし16W以上出力が出るとなっていますが、その時のIidleは0.5Aとなっています。 ただし、このデータシートの数値はシングル動作でプッシュプル動作ではありません。

これらの事を加味して、50MHzなら多少パワーは下がるだろうが、プッシュプルにしたら、16W以上は出るかも知れないと実験を開始したのでした。

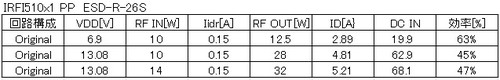

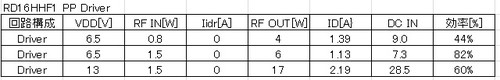

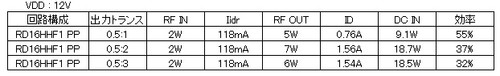

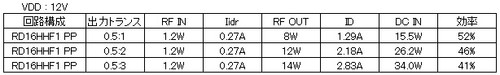

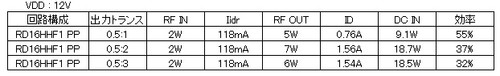

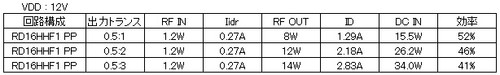

結果は以下のようになりました。

三つのデータが有りますが、変更したパラメーターは出力トランスの巻き数比のみです。 そして、出力は2次側を2ターンの時が一番大きくなっていますが、2次側を1ターンにした時が効率が良いという結果が出ています。 これは、写真でも判るように、終段1次側コイルを通常のAWG24ワイヤーで作ってあり、パワーアンプで良く使うパイプ状のコイルになっていません。 コイルをパイプ状にする理由は表皮効果による高周波抵抗を小さくするのが目的ですので、現在の1次コイルの高周波抵抗はかなり大きく、効率最大と出力最大が大幅にずれてしまっているのでは思われます。

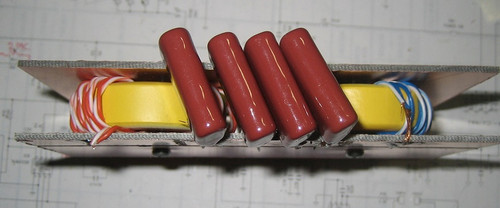

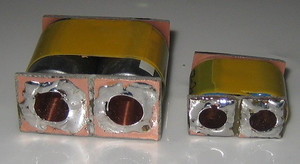

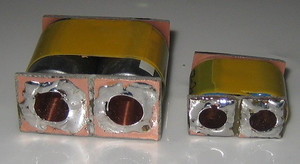

ここで、ひとつヒントが得られましたので、7MHzのパワーアンプで採用したような、パイプ構造のメガネコアを作る事にします。

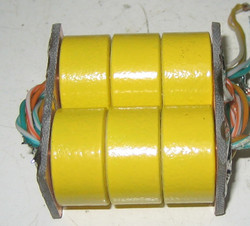

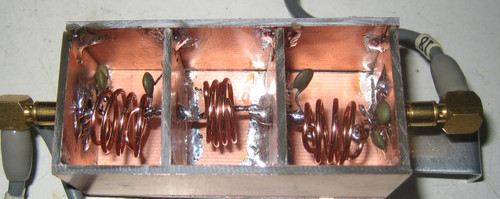

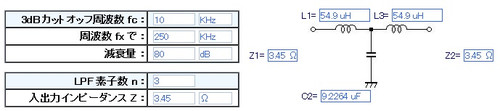

この6m用メガネコアは銅パイプとガラエポ両面基板で作る事にしました。銅パイプも基板もフェライトコアをビニールテープで固めた後、寸法を測り加工しています。 コアは手持ちの分割コアで、プラスチックカバーにはKRFC-6というマーキングが有りましたので、北川工業の10MHz~50MHz用のコアでした。

左はこのメガネコアを基板上に実装した状態です。 出力トランスの2次側に従来直列共振によるタンク回路を挿入していましたが、トランス1次側のインピーダンスが低下した事が影響して、直列共振状態の時のミスマッチが増大し、共振ポイントが判らなくなりましたので、出力はT型インピーダンス変換回路に変更しました。

AMTX_6m_PAmp_RD_PiOut.pdfをダウンロード

また、出力トランスの2次側を1,2,3ターンと変化させますが、都度、最大出力になるようTマッチ回路を調整しました。

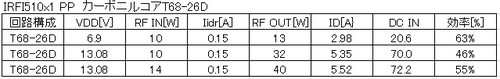

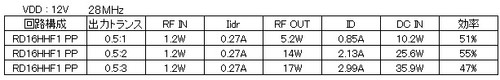

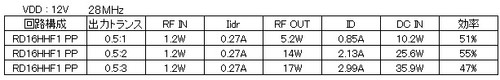

結果は下の表の通りで、パイプによる高周波抵抗の抑制がかなり効いて、やっと、2次側3ターンの時の出力が最大となりました。

この回路構成でRF入力を2Wまで大きくしても出力は変化なしです。 ちなみに、2次側巻線を3ターンとした状態で、VDDを6.9Vまで下げると、出力は6Wとなりました。 AM送信機の場合、VDDの2乗に比例して、出力が変化する必要がありますが、現在の状態では、AM送信機にはなりません。 目標は6.9VのVDDで10W、13.8Vのとき40Wの出力ですから、まだまだ目標には遠いです。

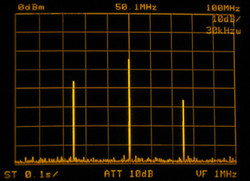

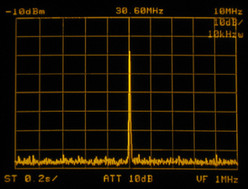

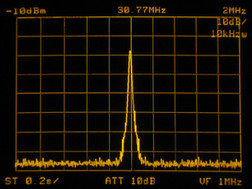

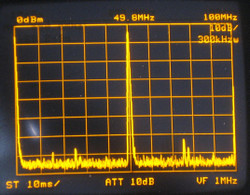

FETそのものの限界なのか? 回路構成が悪いのか? 試に周波数を28MHzして実験してみました。

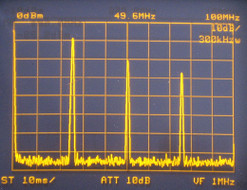

VDD 12Vにて17Wが最高でした。 このFETのデータシートにあるのは、かなり大きなストリップラインを使ったQの高い30MHzオンリーの回路でのテストケースであり、私が手配できる汎用のフェライトコアを使った広帯域アンプでは、やっとこれくらいが最高出力なのかも知れません。 もちろん、VDDを上げて、放熱効果も良くすれば、50W以上の出力も簡単にだせそうですが、12Vではここまでが限界のようです。

VDD 12Vにて17Wが最高でした。 このFETのデータシートにあるのは、かなり大きなストリップラインを使ったQの高い30MHzオンリーの回路でのテストケースであり、私が手配できる汎用のフェライトコアを使った広帯域アンプでは、やっとこれくらいが最高出力なのかも知れません。 もちろん、VDDを上げて、放熱効果も良くすれば、50W以上の出力も簡単にだせそうですが、12Vではここまでが限界のようです。

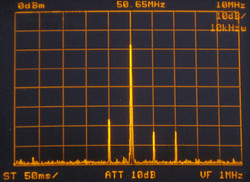

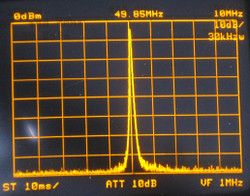

また、50MHzに戻し、出力トランスの2次側を3ターン、ドレインの電圧波形が最適になるように、ドレインソース間に470PFを追加、かつアイドル電流を2石合計にて0.55Aまで増加させたら

6.9V : 8W 8V : 10W 12V : 16W となりましたが、VDDに対するリニアリティは全くダメでした。 三菱が公開しているVd対Poのデータを見ても、これはもう改善の見込みはなさそうです。 結局、この三菱のFETによるAM用パワーアンプは諦める事にします。

この検討を行った時の回路図です。 AMTX_6m_PAmp_RD_180428.pdfをダウンロード

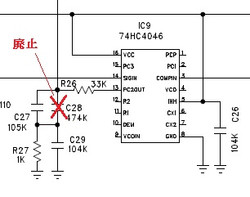

-

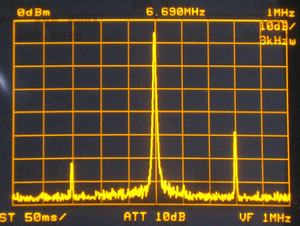

今回の検討で、メガネコアのパイプ状の1次コイルは、かなりロスを改善する事が判りましたので、一度諦めた、IRFI510によるプッシュプルアンプを再検討する事にします。

再検討のIRFI510による回路図AMTX_6m_PAmp_IRFI510_180503.pdfをダウンロード

このFETのゲートに関する制限はVgが+/-20V以下という以外、三菱のFETのような入力パワーの制限は有りませんので、入力のATTは廃止し、入力も出力もパイプ導体のメガネコアとする為、出力側のコアはNECトーキンのESD-R-17S-1、入力側は同じくNECトーキンのESD-R-12C-2(入力側に塗装品を使ったのは手持ちの関係で他意はありません)をそれぞれ2個づつ使用し、0.3mm厚の銅板を丸めてパイプ状にしてあります。 このNECトーキンのコアは10MHz~100MHz用ですので、50MHzでは、最もロスが少なくなる事を期待したいと思います。

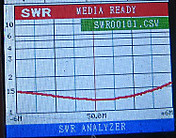

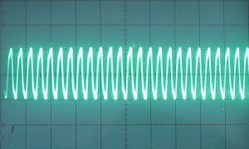

当初、入力側に付いていたトリーマーはショート状態の方が良いので、ショートしてあります。この状態での入力のSWRは1.2以下です。 出力側の2次巻線は2ターンより3ターンの方が良くなりました。 また出力ラインの直列共振コイルは0.1uHくらいまで小さくしました。

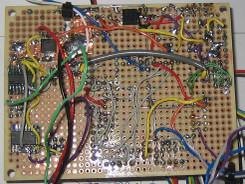

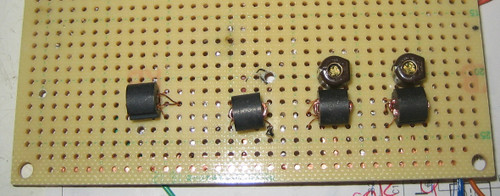

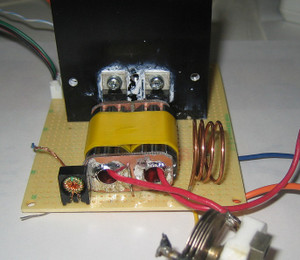

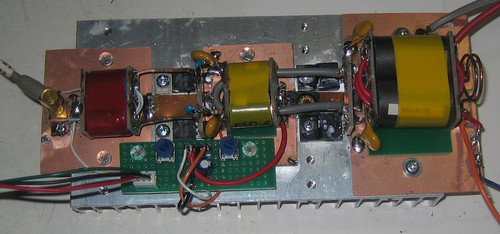

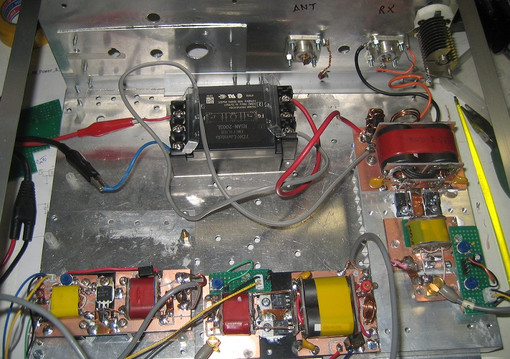

左は、FETとメガネコアを載せ替え、検討を行っている状態です。

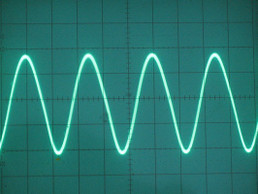

電源電圧対出力のデータを取り始めると、アイドル電流を増やした場合、高いVddの時の電圧対出力の関係が崩れやすくなる事が判りましたので、アイドル電流が流れている状態から、次第にゲートバイアス電圧を下げ、ちょうど流れなくなる電圧に設定してあります。 ゲートバイアスは約2Vで、動作的にはB級アンプとなります。

検討をしていく中で、電源ONした直後は大きな出力になり、次第に出力が下がる現象が起こります。 熱の影響があるかも知れないと扇風機で仰ぎながらデータ取りを行いましたが、得られたデータはこの下がって一定になった時のパワーです。

上のデータの中で、上2段分は、トランスによる損失が有るかも知れないと、出力回路をトランスではなくチョークコイルとして、C結にて出力を取り出した時のものです。 初回の時より大幅に改善していますが、流れているIdの値から、出力インピーダンスがかなり高い状態での動作になっており、FETがもつドライブ能力ぎりぎりを引き出している状態ではなさそうです。

メガネコアと書かれた段が、入力も出力も前述のメガネコアに換えたもので、18.4VのVddで34Wも出ています。 13.8Vで40Wは無理のようですので、最悪、DC/DCコンバーターによる電圧アップで解決する事も視野にいれます。

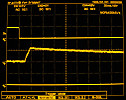

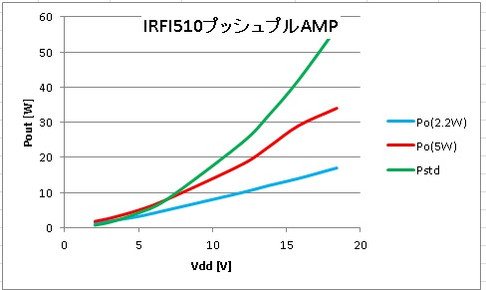

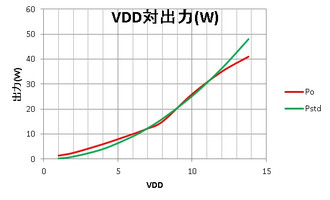

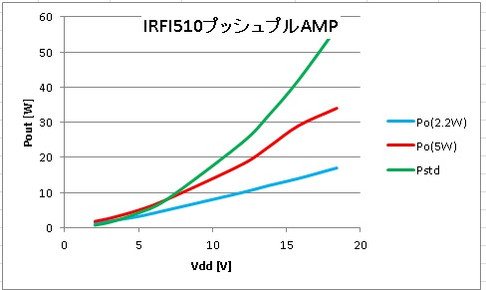

上のグラフは、メガネコアを使った状態で、電源電圧を変化させた時の出力データです。青色が入力2.2W固定、赤色が入力5W固定です。 緑の線は、電源電圧の2乗に比例した出力のカーブです。 本来は赤も青の線も緑の線に重なる必要がありますが、そうなっていません。 ただ、入力レベルを上げると理想カーブに近づくのではないかと思われます。 そこで、入力を10Wまで上げてみました。

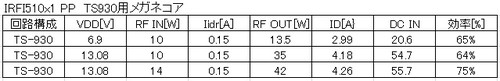

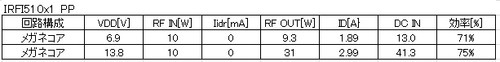

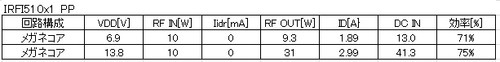

電源の関係でVdd 6.9Vと13.8Vのデータしかありませんが、 13.8Vで31Wの出力があり、かつこの時の効率が75%まで向上しています。 5W入力時のVdd 13.8Vのときの出力は23Wでしたので、かなり理想に近づいて来ました。 現在、シングルプッシュプルですので、2パラプッシュにしたら、もしかしたら?と実験しましたが、13.8Vで30Wしか出ませんでした。 しかも電流は3.5Aくらい流れていましたので、効率も出力もダメと言う事でした。

平均出力10WのAM送信機のファイナル段の入力ドライブ電力を10Wまで上げると安い、10石で615円(61.5円/1石)の、DCDC電源用FETでも50MHzでPWM変調のAM送信機を作るれる可能性が出てきました。 これは面白くなってきました。 終段ドライブ用として10Wのアンプを検討する事にします。

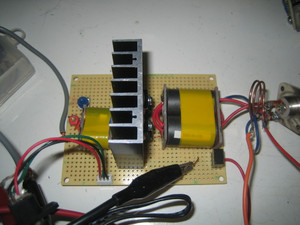

ドライバーとしての10Wアンプは、リニアリティは必要ありませんので、ゲインだけは稼げるRD16HHF1にしました。

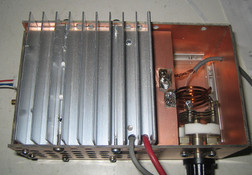

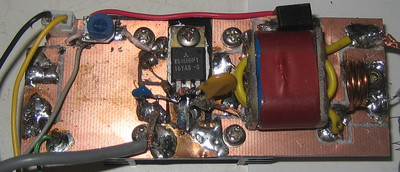

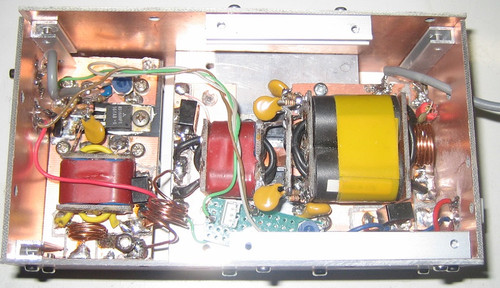

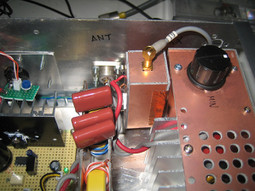

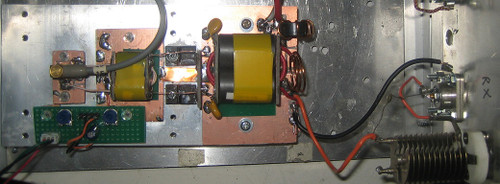

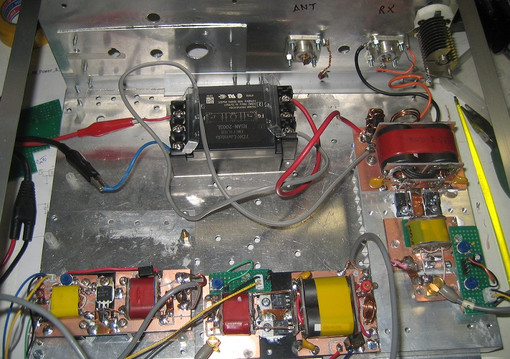

7MHzの時のパワーアンプと同様に放熱板の上に、両面基板を敷いて、その上に立体的に回路を組みました。 この状態で、初段のドライバは12V駆動ですが、電流は1.5Aくらい流れて、終段のゲート電圧の波高値が+/-10Vくらいありますので、終段はほぼ10W近くでドライブされているようです。

終段の電源電圧を6.9Vとした時の出力は10Wで電流は2.72A流れていました。効率は53%くらいです。

当初、ドライバー段に入力を加えた後、入力をOFFとしても、電流が流れ続きます。自己発振を起こしている状態でしたので、ドライバー段のドレインからゲートへCRによる負帰還をかけ、発振防止を施しています。

この状態での配線図です。AMTX_6m_PAmp_IRFI510_180509.pdfをダウンロード

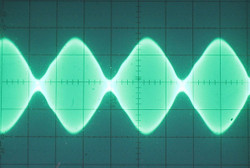

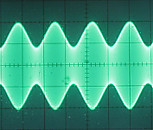

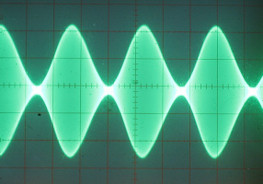

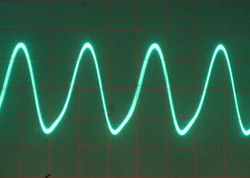

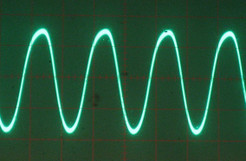

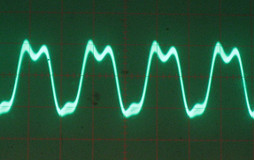

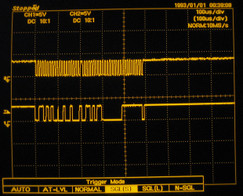

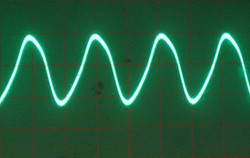

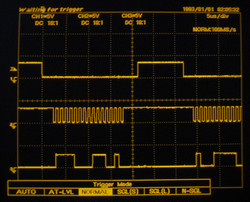

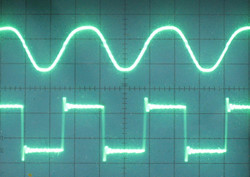

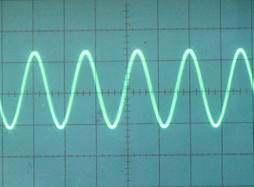

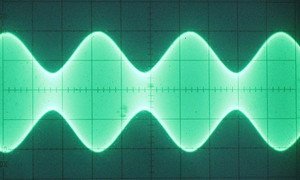

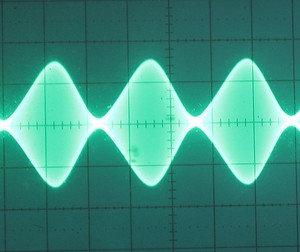

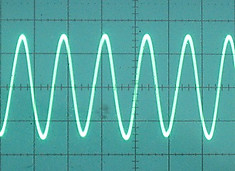

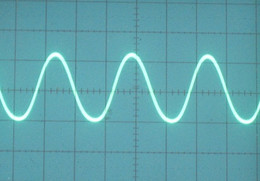

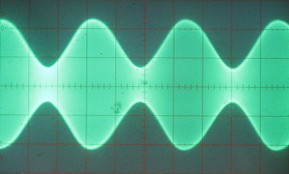

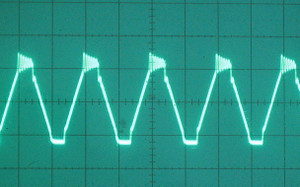

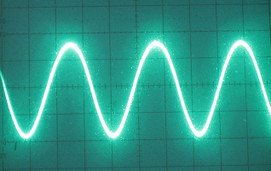

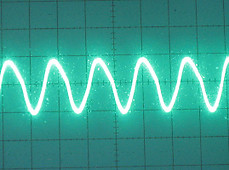

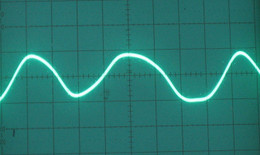

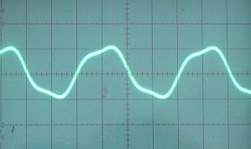

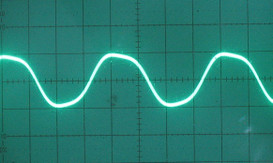

期待しながら、13.8vの電源を確保し、送信ONすると、15Wしか出ません。 オシロでゲートやドレインの波形をチェックすると、もう50MHzの信号はどこへ行ったんだと言わんばかりのリンギング波形です。

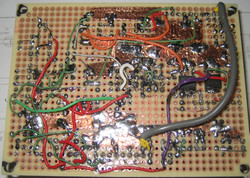

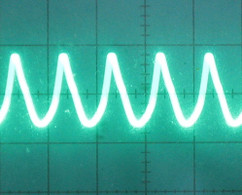

ドライバー単独の場合、きれいな波形を見る事ができますが、終段回路が動作した途端、第2か第3高調波だらけの波形で、完全に増幅動作は麻痺していました。 やはり、50MHzともなると、7MHzのようにはいかないという事が良く判りました。 パワーアンプの構造を最初からやり直す事にします。

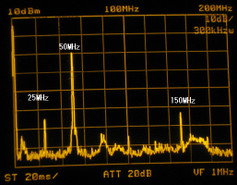

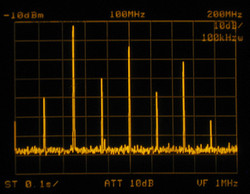

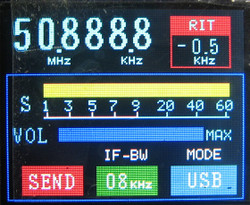

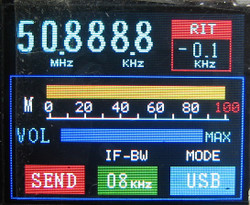

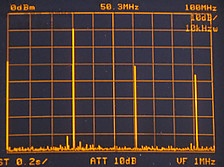

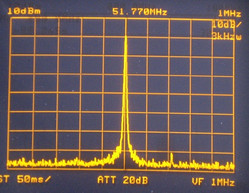

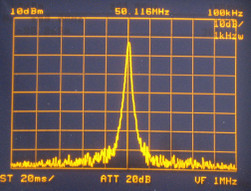

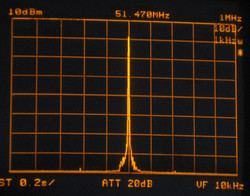

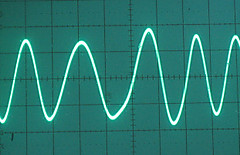

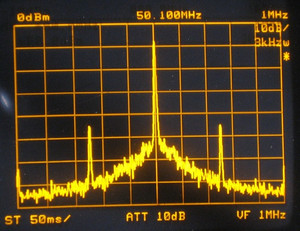

上のアンプが40W出力を狙う終段ステージです。 13.8Vの電源を使い、8W入力で35Wくらいを出力できます。 ただ、出力段の直列共振回路がうまく機能しません。10Wくらいの出力では、バリコンの回転に応じて出力が変化し、それなりの共振ポイントが得られますが、35W出力では、10Wの時の同調ポイントは変わらないのですが、ほとんどピークが判りません。極端にQが下がった状態です。

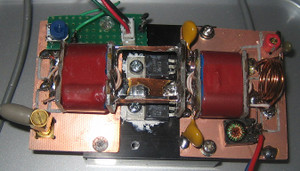

下の写真は、10W出力を狙うドライバーステージです。 最大出力は12V電源で12Wくらい有り、この時の入力は0.5Wくらいです。 ただし、入力のSWRは3くらいでアンマッチですが、実際の回路では、この前にDDSからの信号を8倍する逓倍回路が挿入されますので、問題ないでしょう。 このドライバーも出力が3Wくらいの場合、出力の直列共振回路は正常に機能しますが、12W出力の場合、終段ステージと同様、共振ポイントが見つかりません。

ふたつのアンプで出力の差があるにせよ、フルパワーの時、出力共振回路のQが大幅に落ちるのは、メガネコアの直流重畳による飽和ではないかと思われます。 丸1日かけて、作り直した終段とドライバーのステージですが、再度メガネコアから作り直す事にします。

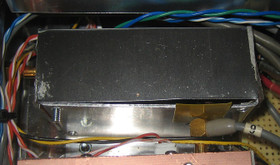

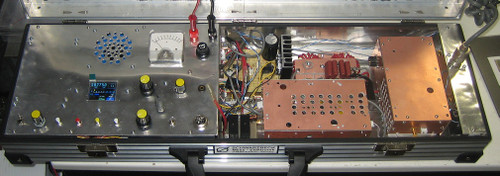

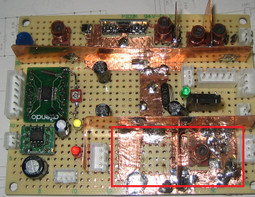

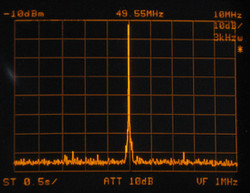

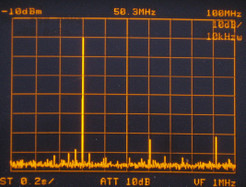

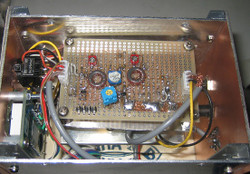

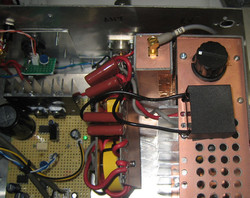

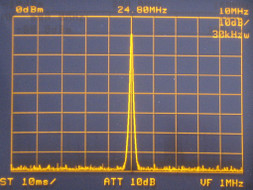

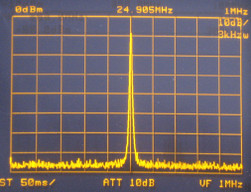

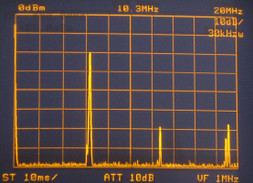

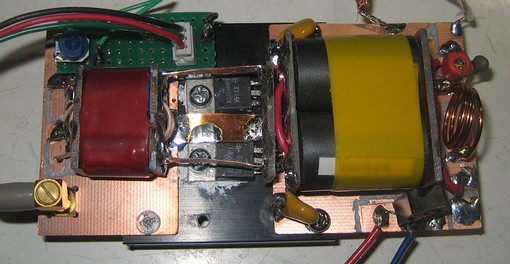

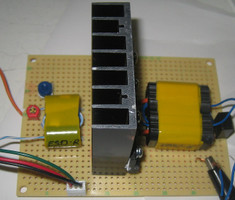

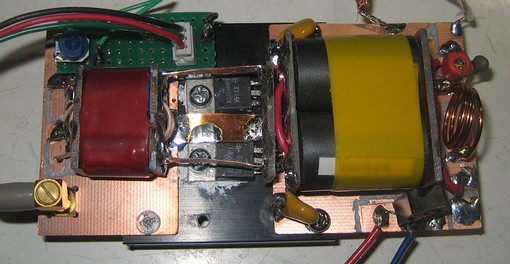

ドライバー段のメガネコアは現在終段に使っているESD-R-17S-1 のコアをドライバー段に移し替え、0.5W入力で12Wの出力を確保しました。 終段には、新たに、ESD-R-26Sというコア2個でメガネコアを作り実装し、40Wの出力を確保しました。 いずれの最大出力の状態でも、50MHzの共振動作が得られます。

上の写真がメガネコアを載せ替えた12Wドライバー。 下の写真が新たにメガネコアを作った40Wファイナルです。 この回路では、電源ON直後に出力が大きく、時間が経つにつれ出力が下がる現象は有りません。 以前、この現象が顕著に生じていましたが、今は反対に電源ON直後数秒間は出力が増加しています。 出力が増加するのは、回路全体の調整ポイントが多少ずれているのが原因と考えられますが、最大の原因であった出力トランスの磁気飽和(DC電流とコアの発熱が最大の原因)は解消されたようです。

回路図6mpd180520.pdfをダウンロード

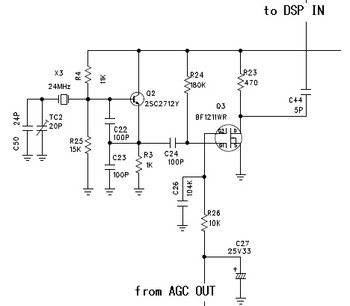

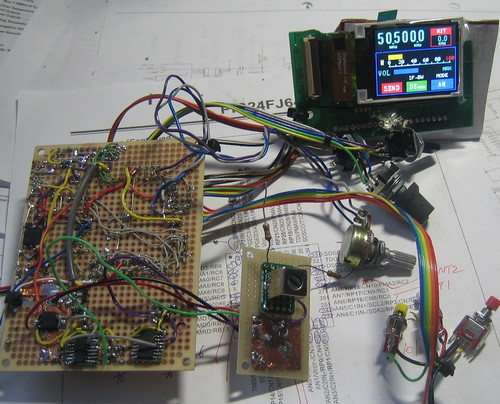

次に、このドライバーをDDS VFOからドライブするプリドライバーの検討です。 DDS VFOの出力は50Ωの出力インピーダンスで40mWしか有りませんので、これを0.5W近くまで増幅する必要があります。 この回路として、Pcが2WクラスのRFトランジスタを探しましたが、いいのが見つかりません。 よって、このプリドライバーもRD16HHF1を使用しますが、シングルアンプとする事にしました。 このアンプで出力0.4Wほど確保するにはA級増幅するしかなく、放熱板が無い状態で、フィンがあっちちになります。 結局このプリドライバーもドライバー段と同じような構造で、下の写真のようになりました。

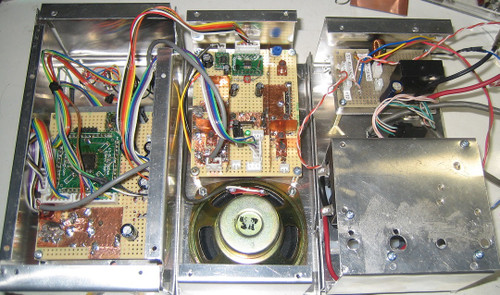

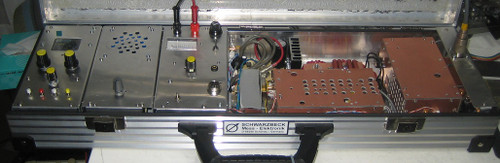

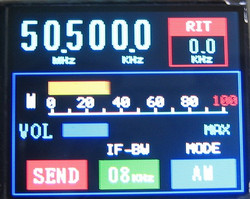

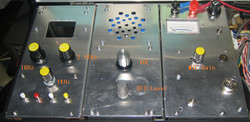

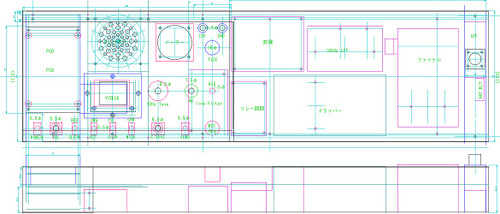

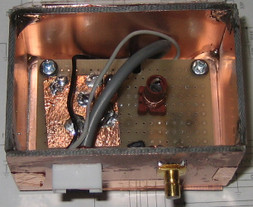

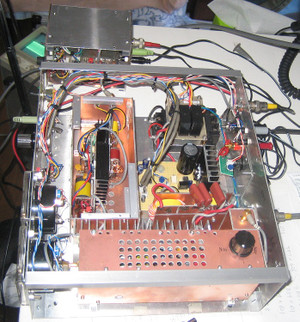

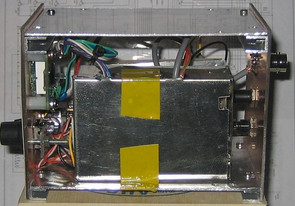

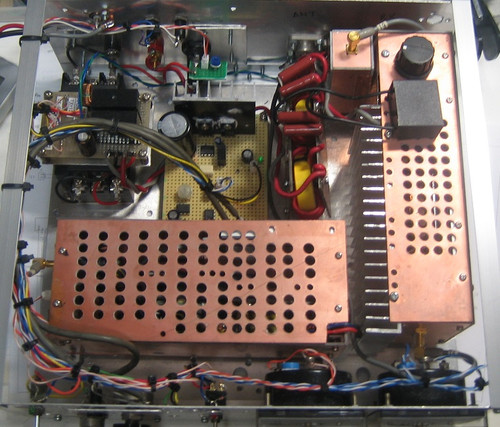

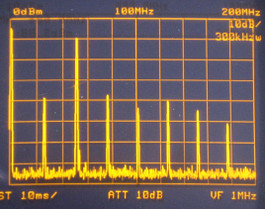

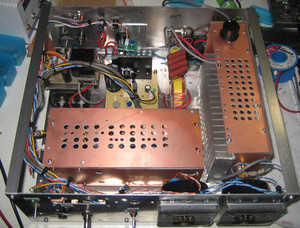

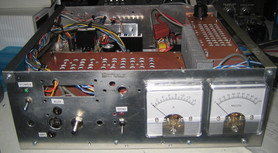

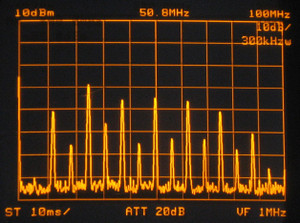

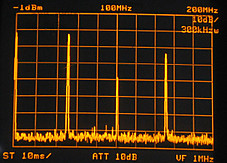

左下の横向き基板がDDS VFOの出力を0.4Wまで増幅するプリドライバー。 真ん中の横向き基板が0.4Wの入力を10Wまで増幅するドライバー。 右側の縦向きの基板がファイナルで10Wを40Wまで増幅します。 この回路が40W出力している時の全体の消費電流は10Aくらいになっています。

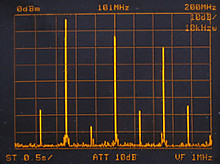

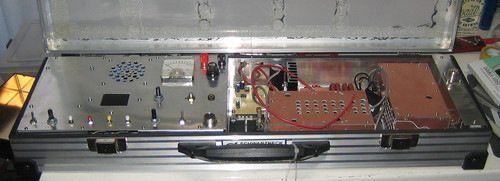

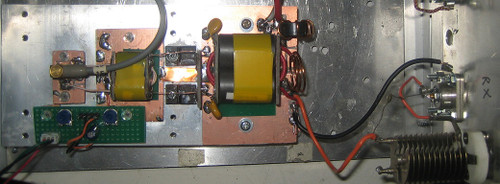

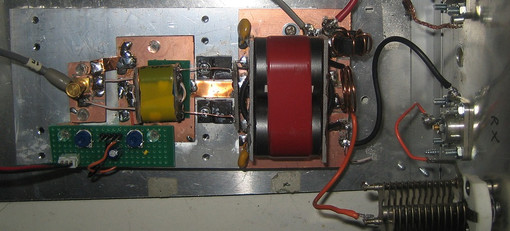

上の写真は、とりあえず、アルミシャーシの上に並べただけで、手を近づけたり、物を動かすと出力レベルや高調波レベルが変わり不安定ですので、これら3つの回路をシールドケースの中に収めるようにします。

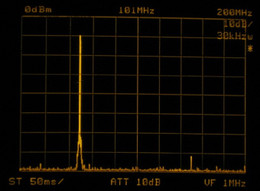

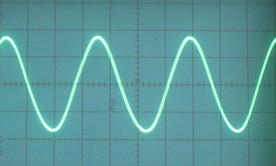

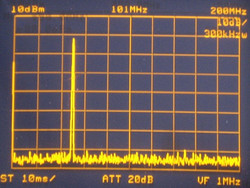

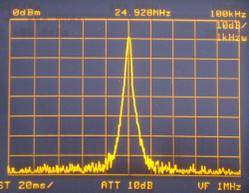

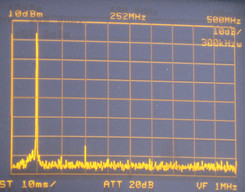

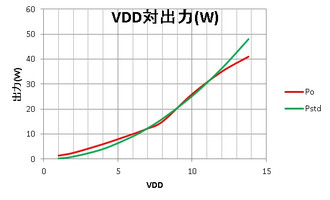

出力はVDD=6.9Vのとき、12W。VDD=13.8Vのとき、41Wとなりました。

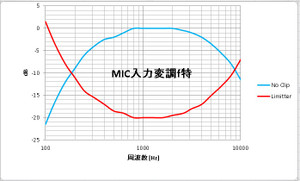

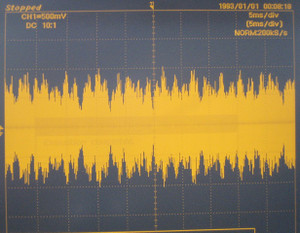

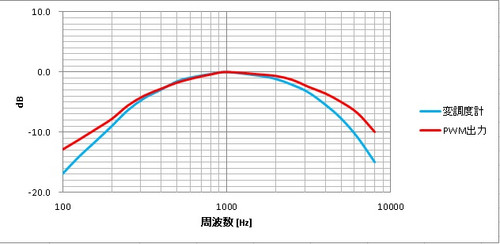

肝心な電源電圧対出力特性ですが、左のグラフのようになりました。 緑の線が、完全なリニアリティ曲線で、赤の曲線がこのアンプの実測値です。 33W出力当たりまでは、ほぼ理想のカーブをしておりますが、それ以上の出力になると、パワーが伸びません。 また、低いVDDの場合、ゲートからドレインへのパワーの漏れが影響して、理想より大きい出力となっています。

この特性のアンプにAM変調を掛けたとき、約85%の変調度までは、ほぼリニアですが、最大変調度は92%程度となり、85%から92%までの波形は次第につぶれるようになります。 また、いくら変調度を上げても、キャリアはゼロにはならないというデータです。 このような特性のRFアンプにAM変調を掛けた場合、どのくらいの音質になるかは、PWM変調器を作ってから確認する事にします。 一応の目標は、80%くらいの変調度で、音楽がちゃんと聴ける程度とします。

RFブロックの回路図AMTX_6m_PAmp_40W180610.pdfをダウンロード

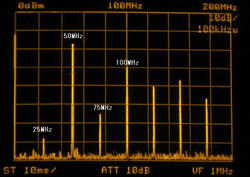

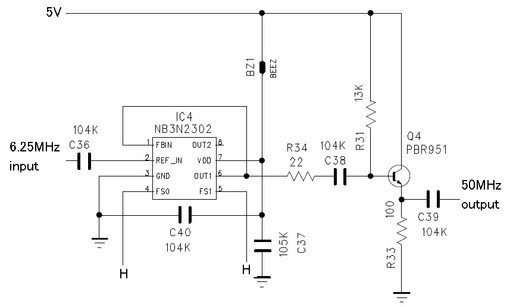

次は、DDS VFOから、このプリドライバーをドライブする8倍逓倍回路の製作にかかります。

6.25MHzのDDS出力を50MHzまで逓倍し、このパワーアンプをドライブする8倍 逓倍回路へ続く。

このアンプを改善の為に再検討した続きはこちらです。

INDEXに戻る

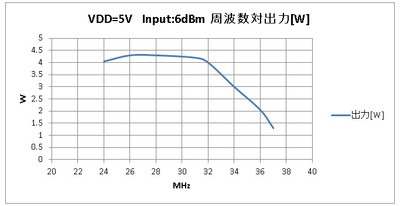

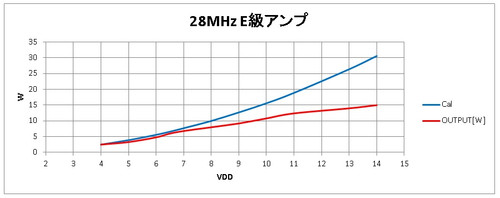

上のグラフは28.5MHz、入力3Vppにて、電源電圧を可変した時の出力データです。青色のカーブはVDD:4Vの時の出力2.5Wを基準にした理想的なデータです。 赤色のカーブが実測値です。 VDD 7Vくらいまでは、なんとか理想に近いカーブをしていますが、それ以上のVDDでは電源電圧と出力の関係は非直線になっており、PWM変調においては、きれいな歪の少ない変調がかけられない事を示しています。

上のグラフは28.5MHz、入力3Vppにて、電源電圧を可変した時の出力データです。青色のカーブはVDD:4Vの時の出力2.5Wを基準にした理想的なデータです。 赤色のカーブが実測値です。 VDD 7Vくらいまでは、なんとか理想に近いカーブをしていますが、それ以上のVDDでは電源電圧と出力の関係は非直線になっており、PWM変調においては、きれいな歪の少ない変調がかけられない事を示しています。