8倍 逓倍回路

カテゴリー<6m AM >

6m AM用の終段ステージはドライバー及びプリドライバーの検討が終わりましたので、次にDDSで作られた6.25MHzの信号を8逓倍して、50MHzを得る回路の検討です。

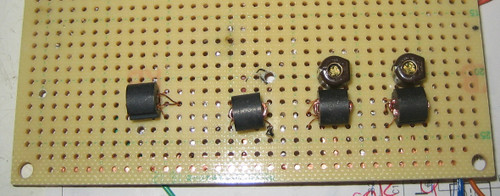

8倍逓倍はダイオードダブラーを3段シリーズに接続して8倍を得るつもりです。 回路は以前作成した、7MHzのVXO出力を14MHzに2逓倍する回路をベースに定数を最適化して実現します。

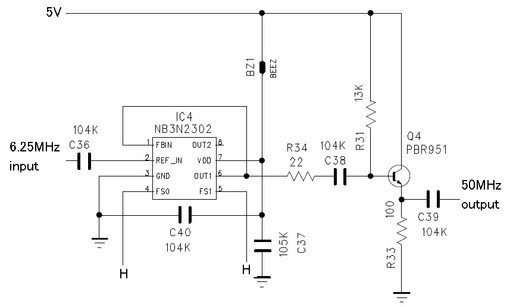

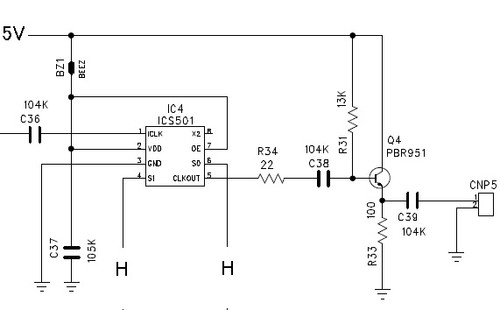

8逓倍回路の回路図 6mTX_multi8.pdfをダウンロード

この回路図の各定数は50MHzを得るQ3までは、実際の値を示します。Q3から後段のプッシュプル回路はまだ実装されていません。

50Mhzで十分なゲインを得ようとすると、低周波用の2SC2712のようなftが80MHzくらいのトランジスターでは、不十分で、ftがGHz台のトラジスターが必要となってきます。 GHz台のftを有する小信号用トランジスタのVCEは12Vかそれ以下の事が多く、後日、入手で困らないように5Vの電圧で動作させ、最後にファイナルステージの必要出力0.5Wを確保するようにします。

実験回路では、12.5MHzまでは、低周波用の2SC2712ですが、25MHz以上はNXP製のftが8GHzのトランジスターを使用しています。 このトランジスタは東芝やルネサスのGHz台のトランジスターに置き換えるのは簡単です。 各逓倍段で、ダイオードの負荷抵抗とエミッタ抵抗を吟味し、ベース抵抗は可変抵抗器で最適値を求め、固定抵抗に置き換えるとい作業で完結します。

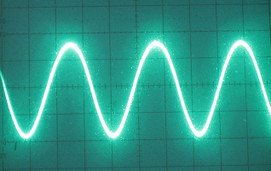

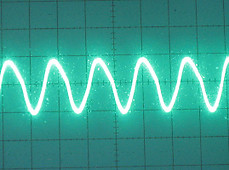

各ステージの波形を以下に示します。

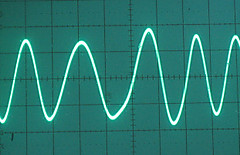

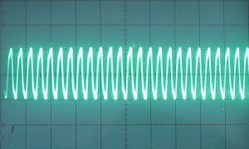

左上がDDSの出力の周波数6.25MHzでQ1のコレクタ波形です。 右上が、2逓倍した12.5MHzのQ4のコレクタ波形です。

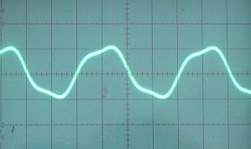

左上がさらに2逓倍して25MHzになったQ2のコレクタ波形、右上が、最後の2逓倍で50MHzになったQ3のコレクタ波形です。

左上がさらに2逓倍して25MHzになったQ2のコレクタ波形、右上が、最後の2逓倍で50MHzになったQ3のコレクタ波形です。

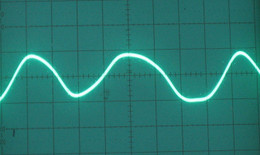

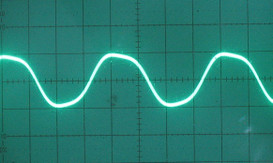

左はこのQ3のコレクタ波形のスイープ時間を10倍にしたもので、周期的に振幅が変化するAM変調がかかっています。 オシロのトリガは、一定のレベルでかかりますので、拡大すると、FM変調がかかっているように見えます。 この50MHzの信号を受信機で聞いた感じはCWやFMを含めた全モードで違和感はありませんでした。

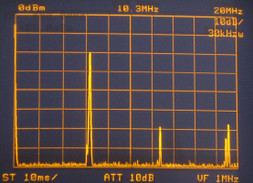

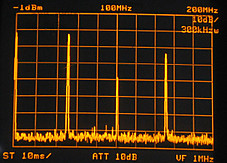

この波形の状態の時の周波数スペクトルを見たのが左の画像です。

この波形の状態の時の周波数スペクトルを見たのが左の画像です。

確かに50MHzの信号は生成されていますが、基本波となる6.25Mhzおきに、きれいにスプリアスが生じています。 これをフィルターで除去するのは、至難の業です。 ダイオードダブラーでは、効率よく逓倍ができますが、その波形をみている限り、2倍1段が実用レベルで、今回みたいに3段もシリーズに接続すると、手の付けようが有りません。

8倍逓倍の方法は、もっとスプリアスの少ない、PLL方式に切り替える事にし、PLL8倍逓倍ICを手配する事にします。

選んだPLL ICは ONセミコン(台湾)のNB3N2302。 RSで入手出来ます。

上が、このPLL ICの回路図です。 4番ピンと5番ピンをH(5V)にすると、8倍の逓倍回路として動作します。

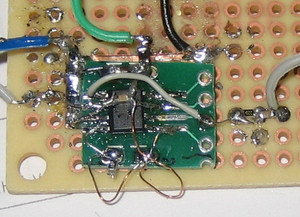

データシートを見ながら、ピッチ変換基板と蛇の目基板上に組み立て、テスト開始。

全く動作しません。 消費電流が60mAくらいになっています。データシートではMax50mA。 異常動作です。配線が間違っているのか、何度もテスターを使いチェックしましたが、異常は有りません。 しかし、入力をゼロにすると消費電流はゼロになります。 出力端子をオシロで見ていると、かなり小さいレベルでRF信号が見え、拡大すると、ロックしていないVCOの発振波形です。 かなり悩んだ末、判った事は、入力レベル不足であったという事です。データシートでは、入力Hレベルは2V以上となっていましたので、オシロで入力レベルをチェックしたのですが、オシロのレンジの読み間違いで、実際は2Vppしかなく、これに気付かなかったのが原因でした。

入力を4Vppまで上げると、PLLの出力レベルが大きくなり、ロックし、消費電流も13mAくらいに下がります。

50MHzのSSB受信機でビート音が綺麗に聞こえます。

上の左も右も50MHzで、オシロのsweepを変えただけです。 この状態でスペアナを接続してみました。

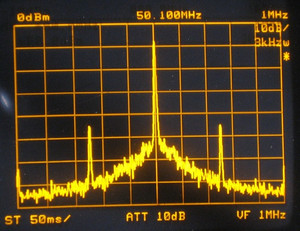

左上が50MHz出力のスペクトルです。右上はこのPLLの入力となるDDSの6.25MHz出力です。

50MHzのスプリアスに問題があります。50MHzのキャリアの両脇に約4MHzくらい離れてスプリアスが出ています。そのレベル差は-40dBくらいで、スプリアス規定でアウトです。 入力の6.25MHzにはこのようなスプリアスは無く、これは、PLLの内部で発生しているものです。

せっかく、ICを手配しましたが、このPLL ICは使えない事が判りました。 RSで入手可能なPLL逓倍ICでMOQが2で1個260円というIDT(USA)製のICS501というのが見つかりました。 海外在庫との事で、日曜日の夜注文して、木曜日に届きました。 今回は緊急という事でこのICのみにしましたので、送料450円により、単価は約2倍になってしまいました。

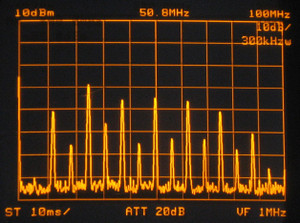

左上がエミフォロの出力波形で50MHzです。 右上は第3高調波まで見えるスペアナ画像です。センターが100MHzですから、左側の1本のスペクトルが50MHzで余計なスプリアスも、低調波も有りません。 第2、第3高調波がかなりのレベルでありますが、これは、終段のLPFで綺麗に除去できますので、全く問題有りません。

やっと8倍逓倍のVFOの目途が立ちましたので、これから、PWM変調回路の作成に移ります。

6m AM用変調回路(PWM方式) に続く。

キャリア周波数+/-500KHzのスプリアスを未確認でした。 これを確認した結果、AD9833を使ったDDS VFOとPLL逓倍ICを使ったVFOは送信機には使えない事が判りました。

左のスペクトルは、改めてDDS VFOの50MHz出力を1MHzスパンで見た状態です。 キャリアから約250KHzの周波数でスプリアスが有り、かつこのレベルが送信機のスプリアス規定を満足しません。 また、キャリア近傍のノイズ状態のスプリアスもスペックが-60dBですから、これもNGです。