DDS VFO 逓倍回路付(1.8MHz - 50MHz)

<カテゴリー:DDS>

PLLを使った逓倍用ICを入手し、そのスプリアス特性も良好でしたので、作成済みのDDS VFOの中に組み込む事にしました。 (その後、後述のごとく、スプリアスは送信機には使えないレベルである事が判りました。)

PLL逓倍IC ICS501は、最少出力周波数が13MHz以上という条件がありますので、今まで10MHzは5MHzから2逓倍としていたのがNGとなりました。 従い、10MHzもDDSから直接出力させる事にし、LPFを作り代えました。

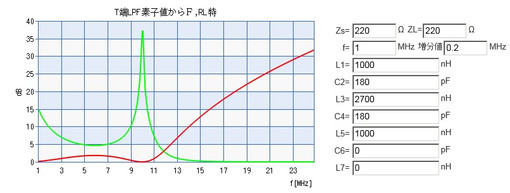

手持ちの部品から、そこそこ使える定数を決めたのが上のLPFグラフとLC定数です。 PLL ICのクロック入力レベルが3.5VPP以上必要なため、アナログ回路のゲインの調整を行い、各定数を見直しました。

回路図 DDS_multi_VFO180709.pdfをダウンロード

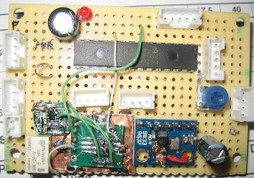

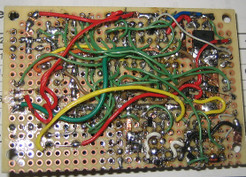

左上がDDS VFO基板にPLL回路を追加し、PLL回路をバイパスしてDDSからのダイレクトに出力する為にリレーで信号の流れを変えています。 右上はその基板の裏側ですが、しばらく時間が経つと、判らなくなるくらい混んできました。

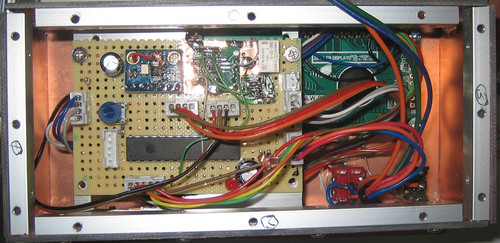

なんとか、シールドBOXの中に全てが収まりました。

PLL ICの逓倍倍率を指定するのは、S0とS1の2本の端子を使用しますが、この端子の入力仕様は少し特殊になっています。通常のH(5V)とL(0V)の他にトライステートモードがあり、HでもLでも無いというポジションがあります。データシートでは、Mという表示がされています。 このモードをPICマイコンで作り出すには、PICマイコンの端子を入力モードにしてやれば実現できます。 このような仕様なので、通常2本のi/oの場合、4モードしか実現できませんが、このICは9モードを実現しています。 使用可能な逓倍倍率は、2倍、3倍、4倍、5倍、6倍、8倍と、ハムが送信機を作るときとても便利です。 今回のDDS VFOには、2倍、3倍、4倍、8倍だけを使いました。

ソースコードDDS_multi_VFO_ICS501.cをダウンロード

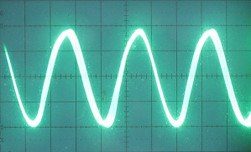

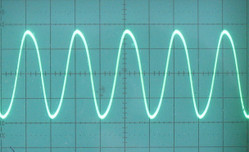

左上が7MHzの出力波形。LPFのカット周波数を10MHzくらいまで上げましたので、線が太く表示されています。 右上は50MHzの出力波形です。 その他のハムバンドの周波数も出力可能ですが、これほど綺麗では有りません。 当初から7MHzと50MHzのAM、CW送信機を想定していますので、他の周波数が必要になった場合、都度検討する事にします。

たちまちは、50MHz AM送信機のVFOとして使用します。 このVFOを使った50MHz用AM送信機の製作はこちらを参照下さい。

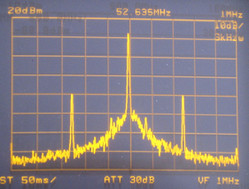

50MHz用AM送信機に使った結果、キャリア+/-240KHz付近のスプリアスと、キャリア近傍のスプリアスが新旧スプリアス規制いずれも不適合となる事が判りました。 結局このDDSとPLL逓倍ICは送信機には使えないという事が判った次第です。

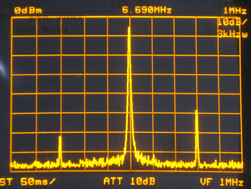

左上はDDS 6.25MHz出力をPLL ICで8逓倍したときのVFO出力。 右上は7MHz付近をDDS単体で出力した時の出力です。いずれも、送信機に要求されるスプリアスは不適合で、これらのスプリアスは後段のフィルターで取り除く事は出来ません。

このDDSの出力に現れる+/-300KHzのスプリアスについて検討を始めました。

DDS VFO AD9833 名誉挽回 に続く。