DDS VFO AD9833 名誉挽回

<カテゴリー:DDS>

今までの記事で、中国製のDDSユニット基板は送信機には使えないという先入観もあり、かなりこき下ろしてきましたが、初心に帰りチェックしていくと、これが、早とちりであったかも知れません。 スプリアスの多い原因は、アナデバのDDSではなく、安物のSPXOではなく、中国製の基板でもなく、 私が作った基板の中に問題があるかも知れません。 では、本当の所はどうなんか?と実験を始めました。

-

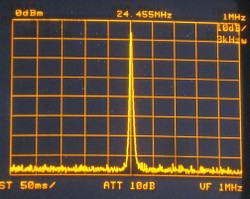

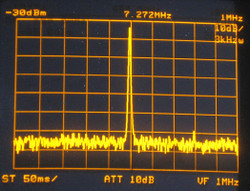

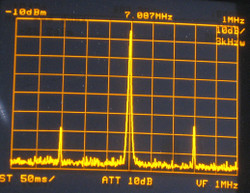

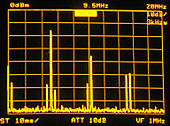

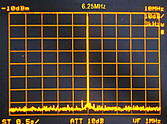

左上がSPXOの25MHz出力です。 余計なスプリアスは全く見えません。 右上がDDSの7MHz付近の出力です。 +300KHzの周波数にかすかにスペクトルが見えますが、そのレベルはスペアナの暗ノイズで良く判りません。 という事は、DDSが発生源かも知れません。

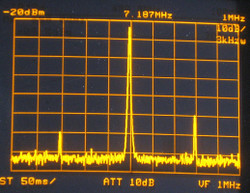

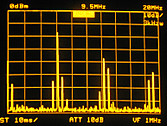

左下はQ1のエミッターのスペクトルで、この部分に+/-300KHzのスプリアスが現れます。 Q1のベースは右上のスペクトルと同じですので、S/Nが良くなって見えるようになったか、Q1の内部で増強されたと思われます。 右下はQ1のコレクタのスペクトルです。 Q1のエミッターにスプリアスが生じているという事は、当然、そのままコレクタ側にも、同じようなスプリアスが生じます。 50MHz DDS VFOでのスプリアスはPLL逓倍ICによるもので、これとは異なりますが、逓倍回路を通さない状態でも生じていたスプリアスはこのQ1のコレクターに現れるスプリアスそのものです。

DDSのキャリアを中心に+/-300KHzのスプリアスが出る問題ですが、これは、簡単に言えば、キャリアを300KHzの信号でAM変調した状態です。 もしそうなら、電源ラインに300KHzのキャリアが漏れているのかもと、スペアナを駆使して調べましたが、それらしき信号は見つかりませんでした。

一方、WEBにアナデバが公開している技術資料が見つかりました。

これは、DDSから発生するスプリアスについての技術資料です。 この中で、DDSの出力周波数を変化させた時、スプリアスのオフセット周波数(キャリアとの差の周波数)が変化する場合、そのスプリアスの発生源はDDSの中にあり、周波数を変化させても、スプリアスのオフセット周波数が変化しない時は外部からのAM変調と判断できる事が記述されていました。

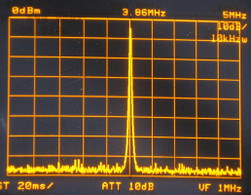

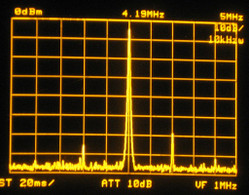

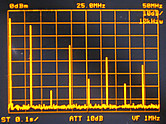

左上はDDSから直接3.86MHzを出力したとき、右上は4.19MHzを出力した時のスペクトルです。 左の周波数ではスプリアスが無いように見えますが、実はスプリアスが7.9MHz付近に有ります。 右の周波数では、キャリア対して1MHzの差でスプリアスが見えます。 要するに、DDSの出力周波数により、スプリアスの周波数も変わるという事ですから、これは、DDSの内部で発生しているスプリアスである事になります。

DDSは基本的にはスプリアス発生器であり、これを送信機の原発振とするには、基準周波数(SPXOの周波数)と出力周波数を適切に選ばないといけないという事のようです。

25MHzのSPXOで3.8MHz付近の出力なら、スプリアスが第2高調波付近の周波数となり、後段のLPFでこれを取り除く事が出来ます。 このような条件が成立する周波数を検討する事にします。

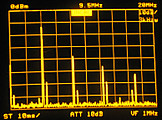

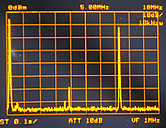

結果は散々たるものでした。左上が約4MHz出力時、上中が約5MHz、右上が約6MHz。 全てUNCAL(アンキャリブレーション)状態で、周波数やレベルの正確さは有りませんが、いずれもスプリアスだらけで、後段のフィルターで取り除く事はほとんど不可能な状態です。 周波数を8MHz以上にすると、本信号とスプリアスの識別が難しくなるようなスプリアスが生じます。10MHzの出力など、もっての他です。 アナデバのAD9833のデータシートに出てくるサンプル周波数におけるスプリアスは3.8MHz付近のデータはぴったし一致しますが、他の周波数では、スプリアスの周波数はともかく、レベルは20~30dB以上の開きがあります。 このレベルの開きは、アナデバの洗練された評価ボードとは違う中国製ですから、ある程度は差が生じる事はしかた有りませんが、少なくとも任意のHF周波数の送信機を作る為の要求には耐えられないというのが実態のようです。

ここで、諦めかけましたが、AD9834は結構良いスプリアス特性を有していますので、それとほとんど同じ構成で、データシート上に出てくるスプリアスデータも大して変わらない理由を確かめる為にも、もう少し実験を継続します。

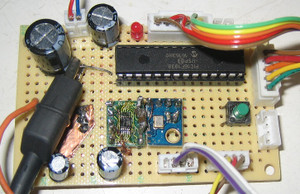

左は、中国製のAD9833ユニットの基板を使わずに、秋月から購入した変換基板にAD9833を実装し、SPXOのみ中国製基板から切り出して構成したDDS回路です。 コントロールマイコンは8bitのPIC16F1983を使用しています。

この基板は、LPFなし、バッファ用に1石のAMPが接続され、そのまま出力しています。 また、SPXOの電源は、DDSの電源とは独立させ、ビート音の濁り対策済みのものです。

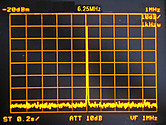

この条件で、50MHzの1/8に当たる6.25MHzのスプリアスと、7.1MHzのスプリアスを見たスペアナの画像は以下です。

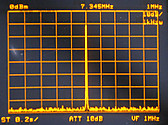

左上が6.25MHzのキャリアを1MHzスパンでみた状態、真ん中が同じく10MHzスパン、右上が50MHzスパンです。 余計なスプリアスは見えません。50MHzスパン時のスプリアスは全て高調波関係のスプリアスですので、LPFで簡単に除去できます。

左の写真は左側は7.1MHzの1MHzスパン、右側が同じく10MHzスパンのスプリアスを見たもので、1MHzスパンではノイズに隠れて見えません。 10MHzスパンの時、3.8MHz付近に-50dBくらいのスプリアスが見えますが、この程度なら、送信機内部のタンク回路で60dB以上に減衰させる事は可能ですので、送信機の原発振器として使う事ができます。

50MHz用 DDS VFOのスプリアスがNGだったのは、デジタル回路に使われるPLL逓倍ICがNGであった事。 DDSからのダイレクト出力に300KHzくらいのオフセットでスプリアスが発生していたのは、中国製の基板の性だった事が判りました。 ただし、アナデバが公表しているデータ通りのスプリアスレベルよりは、かなり高いレベルになりました。 詳細を調べていくと、周波数が10KHz違っただけで、今まで見えなかった-50dBくらいのスプリアスが急に現れます。 HF送信機の源発振器として安心して使う為には、Qの大きなインダクタとバリキャップを使い、きれいな発振を行うVCOを作成し、この周波数を基準発振器をDDSとしたPLL回路でロックするのが一番無難のようです。 VCOは発振可能な周波数範囲がDDSに比べて狭いですが、高調波以外、余計なスプリアスの無い信号を得る事が容易です。

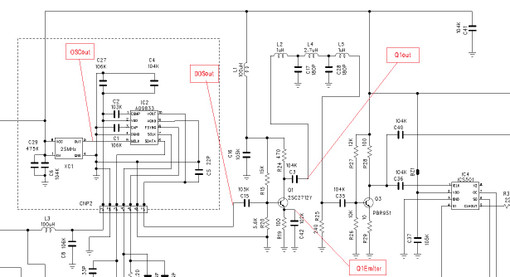

この実験に使ったDDS VFOの回路図 DDS_VFO1983TXCO25MHz.pdfをダウンロード

50MHz AM送信機に必要なVFOはPLL方式を採用する事にしましたので、このVFOは使い道がなくなりました。 そこで、スプリアスは多いですが、分解能10Hzで100KHzから54MHzまでをカバーする発振器に改造し、検討段階での信号として利用する事にしました。

スプリアスはいい加減ですが、周波数だけは正確にする為、このDDSを校正します。 校正は10.000000MHzで標準電波を出している中国のBPMの電波を使います。

まず、TS930をAMモードにして、BPMを受信します。 今日はS9で入感していました。 これにDDSの周波数を重ね、ゼロビートをとります。 DDSは10Hzスパンで可変していますので、ビート周波数が一番低くなる周波数を調べると、10.000.120Hzのとき、約2Hzくらいのビートとなりました。 この2Hzの音は通常は耳に聞こえません。 ビート周波数が100Hz付近以下になるとスピーカーの性能と耳の限界により聞こえなくなりますが、ビート音にハム音や濁りがあり、この濁りの音が震えて聞こえます。その一周期が0.5秒くらいになったので、2Hzくらいという事が判ります。

ここで、DDSの周波数係数を補正します。

現在の周波数係数 kd は 1.073741824 ですので、これを1.000012倍した数値 1.073754709に変更します。 次に、この周波数係数で実際にDDSを動作させると、10.000.000Hzの表示の時に数ヘルツのビートが聞こえます。 今度は、周波数係数の小数点以下6桁目以降を微調整し、ビート周波数が1Hz以下になるようカット&トライします。 この付近の周波数になると、ビート音に同期してSメーターも振れますので、ゼロビートポイントがすぐに判ります。

このようにして決定した新しい周波数係数 kd は 1.073755709 となりました。

こうして校正したDDSは周波数カウンターの校正でその存在価値を維持する事になりました。

安物の発振器SPXOの周波数確度は±50ppm程度の物が多いのですが、常温における年間ドリフトは5ppmなどという数値になり±50Hzくらいにおさまりますので、初期値のみきっちり合わせると結構正確な周波数を維持します。 ちなみに、この中国製SPXOの初期の周波数確度は-12ppmくらいですので、結構良い性能を持っていました。

使用しているPICは+5Vラインに誤って12Vが加わり、i/oポートが壊れた物でしたが、調べてみると、壊れたのは出力ポートのみで、入力ポートは生きていました。 この生きていたRA0,RA1ポートを入力ポートにする事で、このDDS回路も構成できました。

改造後の配線図 DDS_multi_VFO180929.pdfをダウンロード

改造後のソースコード DDS_100k-54M_VFO.cをダウンロード (このコードはファイナルではありません)

スプリアスの再検討を行い、基準発振器をTCXO26MHzに変更した AD9833 スプリアス へ続く。