50MHz PWM変調方式 AM送信機 2 (PLL VFO)

カテゴリー<6m AM >

50MHz AM送信機用のVFOの製作です。

以前、7MHz用に原発振周波数が14MHzのPLL VFOを作りましたが、200Wの出力がPLL回路に回り込み、PLLがロックしないという初歩的なトラブルで採用を諦め、ジャンク箱行となっていたユニットを探し出し、25MHzのVFOに再トライします。 25MHzを2逓倍して50MHzのVFOに仕上げるアイデアです。 25MHzは1KHzスパンで可変できますので、50MHzでは2KHzステップの周波数アップダウンですが、AMですので、不自由はないでしょう。 前回の失敗を繰り返さない為に、今度は送信機とはセパレートしたケースに収納し、シールドを確実にする事にします。

このPLLに使われているICは東芝のTC9256Pで、40MHzまで1KHzスパンで発振できます。 14MHzの周波数を25MHzに変更し、まずは、そのスペクトルを確認する事にしました。

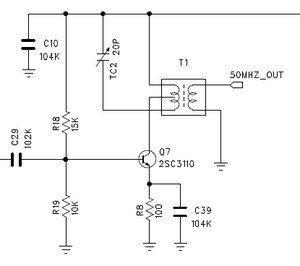

25MHz用の回路図 PLL_VFO_25MHz.pdfをダウンロード

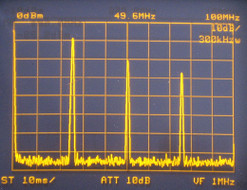

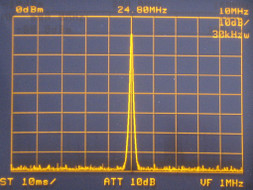

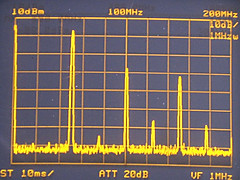

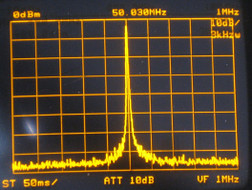

この回路による25MHzの信号スペクトルを確認しました。

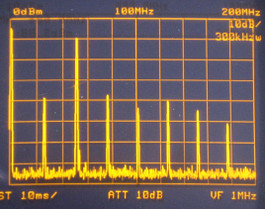

左上が、スパン100MHzのスペクトルで左から25MHz基本波、真ん中が50MHzの第2高調波、右が75MHzの第3高調波です。 この出力の後で、2逓倍しますので、第3高調波はもう少し減衰させて置く必要がありそうです。 右上は10MHzスパンのスペクトルで余計なスプリアスは見えません。

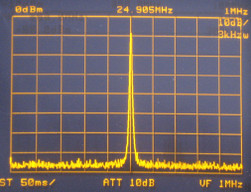

左上が1MHzスパンのスペクトルで、DDSやPLL ICに有ったスプリアスは有りません。 右上は100KHzスパンで、隣接スプリアスも問題有りません。 原発振回路は純粋なクラップ発振回路で有り、チップインダクタのQは35くらい、バリキャップのQも100以上ありますので、余計なスプリアスは全くありません。

PLL VFOの出力には、基本波より約10dB低い50MHzの第2高調波が含まれていますので、次の段でいきなり2逓倍し、50MHzを得る事にします。

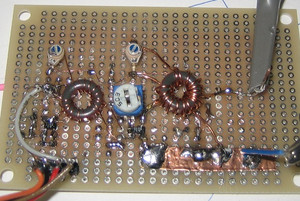

左がこの逓倍回路です。ただし、50MHzのみを選択し、25MHzや75MHzの成分を抑圧する為には、タンク回路のQを確保してやる必要が有ります。

コイルはタップ付のインダクタンス可変式のケースに収まったトランスタイプがベストなのですが、残念ながら入手は無理ですので、カーボニルコア(型番不明)で作る事にしました。50MHzに共振させるLCは1uHと10PFくらいですから、1次側として13ターン巻くと1.02uHとなりましたので、電源側から2ターンのところにタップを出し、これをコレクタに接続しました。この回路の出力インピーダンスは370Ωくらいです。 出力は2ターンのリンクコイルからとりだしますので、出力インピーダンスも370Ωくらいです。

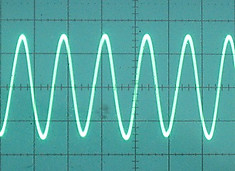

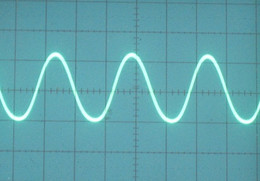

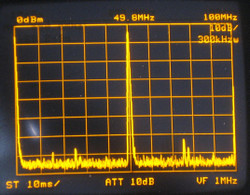

左上がトランスの2次側の50MHz波形。右上がそのスペクトルです。 50MHz以外のスプリアスで、送信機のLPFでは除去が困難な25MHzと75MHzが-30dB程度まで抑制出来ましたが、まだ不十分ですので、この二つの周波数成分だけは、送信機に送り込む前に対策が必要です。

対策として、この逓倍回路の後段に50MHzのみを増幅するバッファアンプを挿入します。

まずは、最高のQが得られる無負荷状態で、このバッファアンプの出力のスペクトルを見てみる事にします。 これがNGなら根本的な再検討が必要です。

左上がVFO出力で少し歪んでいますが、10Vppあります。 右上はそのスペクトルで、25MHzの低調波はノイズに埋もれて見えません。 問題の75MHzは、-58dBくらいまで減衰しました。 この後のアンプでいくつかのタンク回路を通りますので、さらに10dB以上の減衰は容易です。 それ以上の高次のスプリアスは送信機終段に挿入されるLPFで除去されますので、問題なしです。

左の基板はこの逓倍回路の実装状態です。コイルとコイルの間に見える半固定抵抗は50MHzバッファー段の動作バイアスを調整して、75MHzレベルが最少になるように調整するものです。

PLL VFOの全体の回路図 PLL_VFO_50MHz.pdfをダウンロード

一応、PLL VFOとしての基本動作はOKとなりましたので、 これを送信機に接続した時の実負荷をシュミレーションし、かつ送信機が送信状態になっても、回り込みによる障害が起こらないようにシールドケースを検討する事にします。

左上が、25MHz PLL unit、真ん中が2逓倍回路、右上がこれらをケースの中に収納し、最終的には側面をシールド板で囲めるような構造にする予定です。

PLL VFOのフロントパネル部分と木製のキャビネットに収納した状態です。 フロントパネルは基板の銅箔面がむき出しですので、完成した暁には化粧パネルを張り付ける事にします。

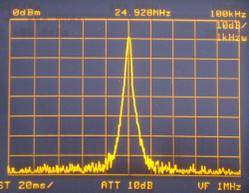

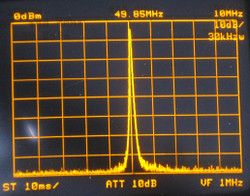

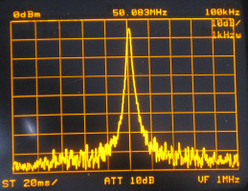

この完成状態での出力は以下のようになりました。 実際の送信機を負荷として接続すると、出力段のQも下がり、出力レベルもダウンしますので、エミフォロのバッファー段を追加し、かつ出力インピーダンスも50Ωとしました。 下はその状態で50Ωの入力インピーダンスであるスペアナに接続した時のスペクトルです。

100KHzスパンの中の+/-15KHz付近が多少騒がしくなっていますが、一応スペック内です。

ここまでの配線図 PLL_VFO_50MHz_2.pdfをダウンロード

ここまでの特性を得る為に、まずトランジスタの変更を行いました。 最初2SC3110というftが4GHzくらいの石を使いましたが、50MHzでのゲインが若干不足しているようで、2逓倍回路や次段の緩衝増幅の安定度がイマイチでした。 そこで、手持ちのNXP製のPBR951(ftが8GHzくらいで50MHzでのゲインは20dB)に変更した上で、緩衝増幅の動作安定の為、エミッタのパスコンを廃止し、かつ抵抗も微調しました。

さらに、この緩衝増幅回路のバイアス電流調整回路に加え、入力レベルも可変できるように1KΩの半固定抵抗を設け、25MHzと75MHz最少状態を調整できるようにしました。

また、アッセンブリ過程で、LCD駆動ノイズがロータリーエンコーダーの入力ラインや基板間のRF信号ラインに乗り、マイコンの誤動作やスペクトルの悪化を引き起こしていましたので、LCDドライブのハーネスは他の回路からなるべく隔離するような線処理を行っています。

PLL VFOのソースファイルPLL_VFO_50MHz.cをダウンロード

機能的には、50MHzから54MHzまでを2KHzスパンでカバーします。受信時に、回路をOFFする事も実験しましたが、送信開始時にタイムラグがどうしても出るので、受信時は表示周波数に200KHzプラスした周波数へシフトする事にしました。 出力が40mWくらいありますので、アンテナが接続されていなくても受信機(FT450)のSメーターはS9まで振ってしまいますので、その対策です。

これから、実際の送信機に接続して微調する事にします。