PLL VFO(7MHz AM用) 失敗でした。

<カテゴリ AM送信機(PWM方式)>

AM/FMラジオのPLLシンセサイザーICを使ったAM送信機用VFOの製作です。

目標は7000KHzから7200KHzまでを1KHzステップで可変できるPLL VFOとします。 使うICは廃番候補のTC9256Pです。 ネット上で7.2MHzのクリスタル付で売られています。

回路図 PLL_OSC_schema0.pdfをダウンロード

PICのクロックが7.2MHzの水晶になっているのは、最初PIC16F84で作り始めたところ、LCDドライブの部分だけでRAM容量オーバーになり、ピンコンパチのPIC16F1827に差し替えた事によります。OSC部分はそのまま使いました。

この回路は東芝の提供するデータシートを理解し、その通り、マイコンソフトを作れば、PLLロックという状態を得る事ができますが、そこに至るまでの工程を以下紹介します。

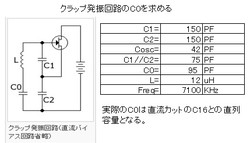

まず、VCOですが、クラップ発振回路の見本みたいな回路です。 手持ちのインダクターで発振コイルに使えそうなコイルは太陽誘電製のLBM2016T120Jしかありませんでしたので、このコイルとONセミコンのバリキャップSVC389で7MHz付近を中心とした発振回路を机上計算して定数を決めます。 PLLのICの代わりに10KΩの可変抵抗でバリキャップ電圧を調整し、約4Vくらいで7.1MHz付近を発振するようにC16を決めてやります。 C0,C1,C2の直列合成容量とLで計算される共振周波数が7100KHzになるように各コンデンサを調整します。 最初、6.6MHzから7.8MHzくらいをカバーするCを求めてテストしましたが、バリキャップ電圧の振動が止まらず、4MHzから12MHzくらいまでのカバー範囲に設定し、実際は7000KHzから7200KHzしか使わない事にしました。 ただし、クラップ発振回路の出力はかなり歪んでいましたので、エミフォロで出力した後、LCのタンク回路で波形整形し、PLLのICに戻したり、トロイダルコイルによるトランスでインピーダンス変換した後、送信機へ出力するよう回路を構成しました。 トロイダルコイルはamidonのT37-2で1次側が10uHになるよう0.3mmのUEWを巻いてあります。

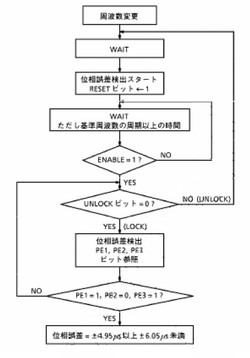

このPLL ICのデータシートの中に、左のような周波数変更を実施してから、PLLロック完了までのフローチャートが示されており、その通りにプログラムを組めれば良いのですが、私の技量では、この入り組んだフローをC言語の関数のみでは、どうしても記述できなく、禁止事項となっている「goto」文で記述する破目になりました。

とりあえず、プログラムが完成し、いざ走らせると、PLLロック検出まではうまくいきますが、最後の位相誤差判定を抜ける事が出来ず、そこで永久ループに陥ってしまいます。 多分ハードの精度が悪くて、要求された一定の位相差を維持できない事が原因と思いますので、とりあえず、この位相誤差判定の行はコメントアウトしたところ、ロータリーエンコーダーを回す毎に周波数が1KHzステップで可変できるようになりました。

その後、LPFの定数設定を吟味し、PE1-PE3が「0」のとき、ループから抜けられる様にフィルターを改善しました。

ネット上でこのICを使った製作例は沢山みつかりますが、東芝が指定したこのフローをフォローしたソースコードは見つかりませんでした。 もしかしたら、プログラムカウンターだけ設定すれば、勝手にPLL LOCKになるのかも知れませんが、確認しておりません。

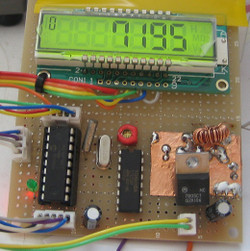

基本動作はOKになりましたが、プログラマブル分周器の分周比を7195に指定しても発振周波数は7196KHzとなります。この問題を調べていくと、7.2MHzの水晶発振周波数が7200KHzではなく7201KHzになっているのが原因でした。 この7.2MHzの水晶はネット通販で10個で150円という格安品ですが、スペックなど有りません。

色々と情報を調べていくとアマゾンで似たような水晶が50個単位で売られており、その商品説明の中に負荷容量20PFと書かれていました。多分同じような値段なので、同一メーカーの同一品だろうと予想し、水晶発振子の両端に接続するコンデンサを計算してみました。

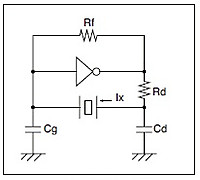

メーカー発表の負荷容量をC0とすると、左の回路のCgとCdはどちらも同じ容量として

Cg = Cd =2 x (C0 - 5) [PF]

と簡易的に計算できますので、実装した後、周波数をトリミングする事にします。

計算結果は30PFと出ました。 一般的な負荷容量は12PFとか9PFですので、15PFくらいを想定したのがいけなかったようです。 コンデンサを33Pと15PF+20Pトリーマーで7200KHzちょうどを発振するようになり、分周比と発振周波数は一致するようになりました。 この発振周波数の確認は受信機で行うのが一番確実です。

PLL IC用クリスタルは正確に7200KHzでなければなりませんが、PICの発振は水晶である必要も7.2MHzである必要もありません。 今回は7.2MHzの水晶が有り余っていたので、使用しただけです。 水晶の両端に付けられたコンデサも最初に見つかった27Pにしただけで他意はありません。

PLL-VCO式の発振器の留意点はピュアな信号が得られるかです。 位相ジッタが原理的に付きまといますので、フィルターや電源、GNDをセオリー通りにやらないと、濁った信号になってしまうと言われております。

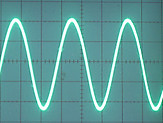

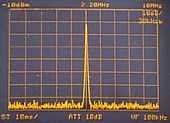

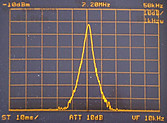

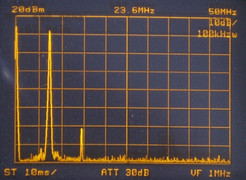

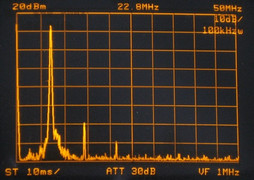

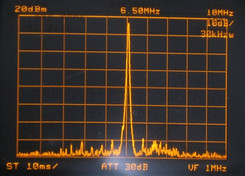

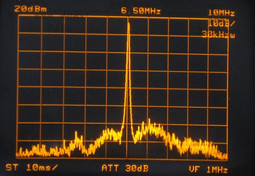

左上が7195KHzのVFO出力波形です。画像はありませんが、第2高調波が-30dBくらいになっています。 これはLPFやBPFで簡単に減衰できます。 真ん中が10MHzスパンで見たスペクトル、右側は50KHzスパンで見たスペクトルです。使用しているスペアナの限界の為、これ以上細かくみられませんが、異常な隣接不要輻射は見えません。 実際にCWモードで受信してみても、濁りのない綺麗なトーンをしています。

今回採用したロータリーエンコーダーはアルプス製の1回転パルス数24のものです。シャフトがFカットでつまみに自由度が無く、パネルにナット止めできないという欠点はありますが、温度による摺動ノイズの問題が全くなく、かつ百数十円で買えるというメリットがあるものです。

このVFOは送信のとき使用しますが、受信の時は使用しません。 受信時はVFOの電源をOFFする事も考えましたが、電源ON時にLCDの待ち時間が影響して、すぐにPLLがロックしません。 そこで、常時VFOは生きていて、受信の時のみ発振周波数を50KHzアップして、受信時の妨害にならないようにする事にしました。 この機能は実際に送信機へ組み込んだとき、検討する事にします。

電源ONした時のデフォルト周波数は7195KHz固定です。 ラスト周波数をEEPROMに記録する事も考えましたが、 AM送信機のメイン周波数固定で問題なさそうです。

ソースコード PLL_VFO.cをダウンロード

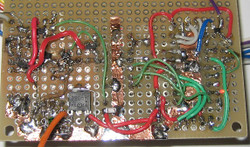

左が7195KHzを発振中のVFO基板。上がその基板の裏側です。 LCDの左上に見えているゼロはPE1-PE3の位相誤差データです。

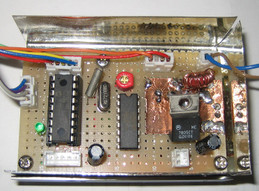

送信機に実装する場合、RFの回り込みが多分発生すると思われますので、シールドケースに入れる事にします。

左上がシールドケース内部の基板、右上はシールドBOXとした状態です。 このように厳重にRFのまわり込みを対策したにも関わらず、わずか10Wの出力にて、ロータリーエンコーダーを回しても周波数は変わらなく、VCOの発振周波数はあさっての方に飛んで行っているという状態で全く使い物になりません。 周波数が変わらないのはマイコンの外部割込み端子にRFが混入して、マイコンが暴走している為。 周波数があさっての方向に行ってしまうのは、終段のRFの漏れがPLL入力端子に混入し、位相が狂ってしまっている為。 これらの問題を丸一日かかり対策し、40W出力でもVFOが安定して発振するようになりました。

これらの対策済み回路図です。 PLL_OSC_schema1.pdfをダウンロード

この状態で出力10W時の不要輻射をチェックしてみました。

左上が水晶発振(VXO)の不要輻射データ、右上がPLL VFOの不要輻射データです。PLL VFOの方はキャリアを中心に隣接周波数の不要輻射が10dB程多くなっています。 この原因を調べていましたら、送信周波数とVFOの発振周波数が同じなら、例え、厳重にシールドしたとしても、送信波の回り込みは阻止できず、このような状態になる事が判りました。 市販されているトランシーバーのVFO周波数を調べたところ、送信周波数とPLL VFO周波数は重ならないように設定し、なおかつ、厳重シールドしてありました。

下のスペクトルは40W出力時の10MHzスパンのもので、左がVXO 右がPLLです。 やはり、このPLLの状態で送信はダメでしょう。

今回のVFOはAM送信機に組み込むのが目的でしたので、PLL VFOは無理と諦める事にしました。 送信周波数と原発信周波数を同じに出来るのはDDSの場合のみのようです。 もちろん、DDS制御のPLLもNGでしょう。

SSBトランシーバーのように送信周波数と無関係な周波数、例えば9MHz台で発振させ、16MHzの水晶発振周波数とMIXし、7MHzを得るとかすればOKと思われますが、それも面倒です。

7195KHz以外の周波数を使える手段として、別のアイデアを練る事にします。

VXO再検討 に続く

7MHz用では失敗しましたが、50MHz用として再検討したPLL VFOは成功でした。