デジタル方式 AM送信機の構想と製作

<カテゴリ AM送信機(デジタル方式) >

RF電力合成器によるDAコンバーターの目途が立ち、必要な12台のRFアンプも完成しましたので、 今回製作するデジタル方式AM送信機の構想を紹介します。 まだ、構想レベルで具体的な製作にはかかれませんが、回路を少しづつ製作する上で、その機能の確認を行う為、まずは、PICマイコンによる制御回路の製作です。

RF電力合成器によるDAコンバーターの目途が立ち、必要な12台のRFアンプも完成しましたので、 今回製作するデジタル方式AM送信機の構想を紹介します。 まだ、構想レベルで具体的な製作にはかかれませんが、回路を少しづつ製作する上で、その機能の確認を行う為、まずは、PICマイコンによる制御回路の製作です。

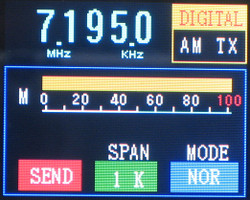

左は、このAM送信機のLCD表示です。 送信機の機能を検討する上で、イメージを得る為に、表示のみ先に作成しました。 オリジナルは、以前作成した50MHz用AMトランシーバーのLCDですが、すでに本体は解体済みですので、この送信機で再利用する事にしました。 送信機の機能が固まるにつれ、表示も変更されますので、最終的には、異なった表示になると思われます。

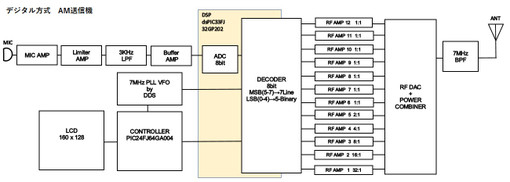

以下にこの送信機の全体のブロックダイアグラムを示します。

WEB上で入手した情報によれば、短波帯のRF DACのリニアリティは、MW帯より悪化するとの事で、そのリニアリティの改善が肝になりそうです。 そこで、この送信機では、RF復調信号による負帰還(NFB)、または、プリディストーション機能などを検討する事にしており、その実現の手段が、今回の開発のメインになります。

まずは、7MHzのPLL VFOです。 このVFOも、以前の50MHz用VFOをそのまま周波数変更して実現しましたので、簡単に出来上がりました。 このPLL VFOは以前、7MHzのPWM送信機用に作り、パワーアンプの出力がPLL回路にフィードバックして、PLLがアンロックになった失敗作がベースになっており、再度、これを7MHzで使うには不安がありますが、シールドの強化や電源の分離などで、乗り越えようと考えております。 これに使用していますPICから、dsPICを制御する為のI/O設定がまだ、最終では有りませんが、一応、配線図も完成しました。

PLL VFO配線図 7MHz_PLL_VFO.pdfをダウンロード

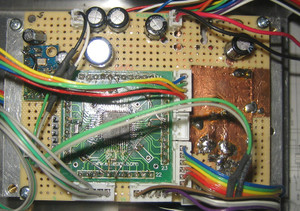

左の写真が、7MHz帯に改造したPLL VFOの基板です。 VFOのアナログ発振回路の周波数をオリジナルの25MHzから7MHzに変更したことと、DDSのAD9833の発振周波数を700KHz帯に変えただけで、ちゃんと、7MHzのPLL VFOとして動作しております。

周波数の可変スパンは100Hzと1KHzです。 AMオンリーですから、これで支障は無いと判断します。

出力は5Vppありますので、そのままRFパワーアンプへ供給可能です。

一方、音声信号をAD変換し、8bitのバイナリコードに変換した後、RFパワーアンプをドライブする為のデコーダー機能を別のPICマイコンで実現し、このdsPICの中でプリディストーションも実行する予定ですが、その具体的な手段はまだ有りません。 まずは、このdsPIC周辺のハード回路を組み上げ、信号を通しながら検討して行く事にします。

基板に回路を実装するにも、回路図が必要ですので、動作するかどうかも確認していませんが、とりあえず、回路図通り、基板を製作する事にします。

ADコンバーター周辺の回路図 RFADC_AMTX_audio.pdfをダウンロード

当初、テストやプリディトーションモードの設定を、VFO側のマイコンで行うと考えていましたが、DSP側とVFO側の通信がSPIを使って出来る見込みが立ちましたので、DSP側にモード設定機能を移し、VFO側は表示の為の結果をもらうだけにします。

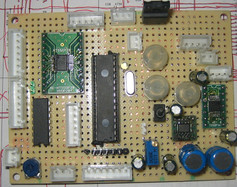

dsPICのオーディオADCとDAC基板が出来ました。 まだ、作っただけで、動作チェックはしておりません。 これから、じっくり時間をかけて、ハードとソフトの検討を開始します。

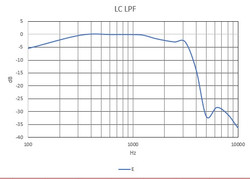

ADコンバーターの前で、3KHzのLPFをTX-88Dを真似て作ったのが左の特性です。 オーディオ帯域を3KHzまでほぼフラットにして、3KHz以上は急激に落とす特性ですが、やはりメーカー設計にはかないません。 メーカー設計と個人の趣味による設計の大きな差は、試作にどれだけお金をかけられるかの差でありまして、決して技術力の差ではありません。 アナログ回路のLPFはこの特性で一旦手を打ち、dsPICの中で余裕があればFIRフィルターで最終仕上げする事にします。

9月のシルバーウィークを利用して、ソフト開発に取り組んだところ、7MHz PLL VFOとdsPICによるAD変換した10bitのデジタル信号を8bitのRF DACをドライブする為の信号に変換するデコーダーができあがりました。

このデコーダーには、AM送信機のキャリアレベル調整機能、RFDACの非直線性(歪)を補正する為の、自動キャリブレーション機能などを組み込みました。

左が、その機能を実装したLCD表示の一部です。 自動キャリブレーションした結果はフラッシュメモリーにセーブされ、電源ON時に読み出してプリディストーション機能が動作します。 このプリディストーション機能の精度は、入力されたアナログ信号の8bitデータに対して、RFアンプの出力誤差は、今のところ、+/-2カウントまでとしてありますが、実際にRFアンプをつなぎ、ダミー抵抗を負荷とした時の精度を+/-1カウントにすべく、12台の各出力レベルを調整する予定です。

これらを盛り込んだ、ふたつのソースが以下になります。

AMTX-ADC-DAC_decorder.cをダウンロード

dsPICのクロック部分を以前の記事で紹介したdsPIC33CHの設定にすると、発振回路は発振しているのに、Foscが生成されませんでした。 代わりに、dsPIC33FJの設定にすると、うまく動作しました。 dsPIC33FJとdsPIC33CHの生まれ故郷となる会社が異なるのが原因でしょうか?

通常の送信モードの時は、ADCが500KHzでサンプリングし、同じ500KHzのクロックでDA変換しますが、テストモードやオートキャリブレーションモードの時は、随時AD変換を行い、500KHzのサンプリイングを停止し、PICが計算を間違うのを防いでいます。

ここまで出来ると、次はいよいよ12台のパワーアンプとこのデコーダーの結合作業となります。

このAM送信機について、一番の心配毎は、高周波電力合成回路を、500KHzくらいのクロックでDAコンバーターを構成させる訳ですが、このクロック信号がどのくらいのスプリアスレベルになるか判らない事です。 結局このレベルは、AM送信機が完成しないと測定出来ませんので、最後の土壇場で、NGとならないように祈っています。

RF DA変換回路(高周波デジタルアナログ変換)& 出力合成回路 へ続く