カテゴリ<SDR>

HDSDRの送信機能が動作するようになりましたので、つぎは、直交変調回路の作成です。 HDSDRで処理したI,Q信号はサウンドカードのLINE OUT端子から出力されますので、この信号と、7MHzのキャリアをMIXして、いきなり7MHz帯のLSB信号を作り出します。

と、軽く考えていましたが、調べていくほど、直交変調回路というのは、以外と難しい技術のようで、全てデジタルで処理して、早々と中間周波数を得た方が完成度は高くなるとい言う事だけは判りました。 しかし、テーマがダイレクトコンバージョンですから、先人のノウハウを学習しながら製作を進めて行く事にします。

手本にしております、Softrockは、N7VEのTayloeサンプリングミキサーをベースとしたQSEという回路構成で、この直交変調を実現していますが、その回路に使用されている抵抗は全て1%誤差のものです。 私が現在ストックしているのは、全て5%誤差の抵抗であり、1%誤差品なら、必要品種を全て新たに手配する必要があります。しかし、そのMOQ(最少オーダー数量)の為に、かなりの出費(1万円くらい)が必要です。 やむなく、私の回路は全て手持ちの5%誤差で進める事にしました。

デジタルの計算と等価になるようにアナログ回路を組むのは、かなり困難な状況なので、せめて、回路構成や使用するICは可能な限りSoftrockに合わせるということで、2G66によるスイッチング回路はオリジナルと同じく、FST3253に変更し、74LS08によるおかしな7MHzの波形は74HC74の出力波形がそのままスイッチング回路に加わるように変更します。 これは、いままでの回路を全てやり代える事を意味し、受信回路からやり直しです。

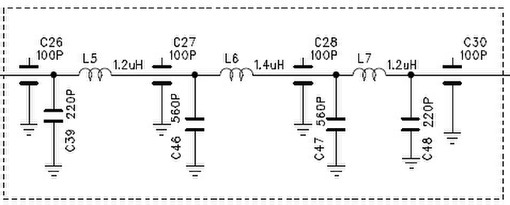

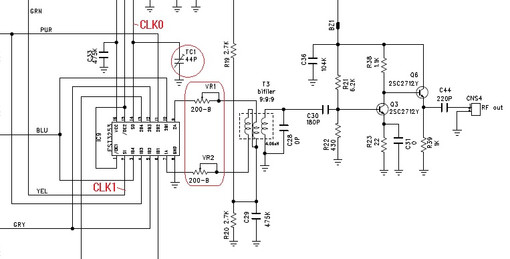

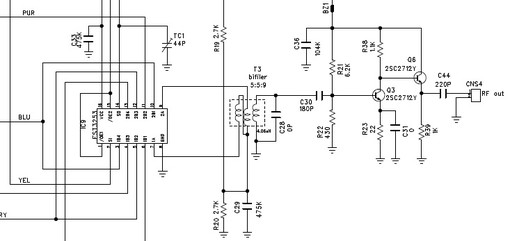

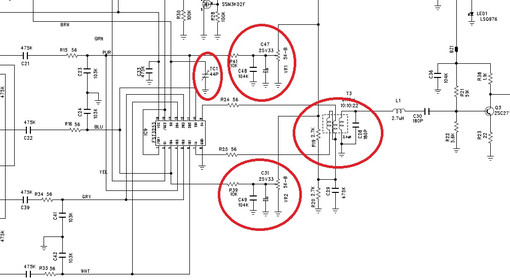

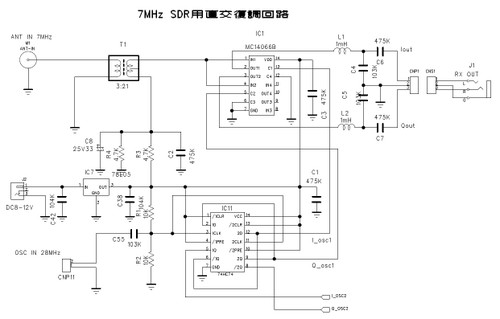

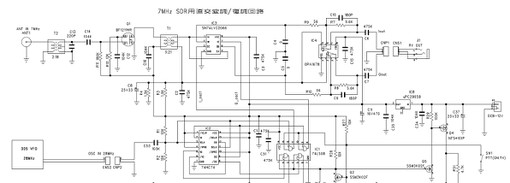

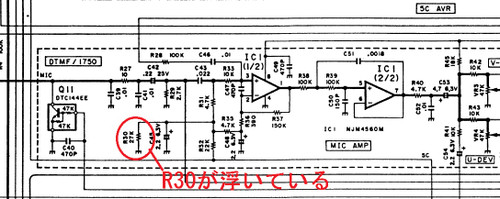

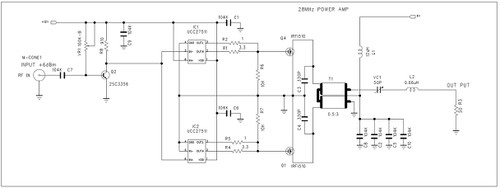

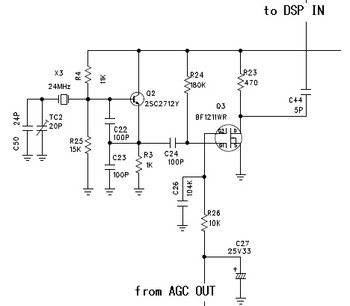

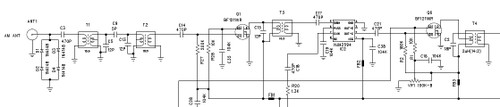

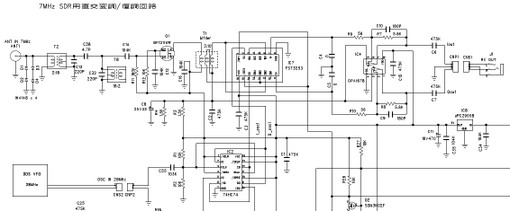

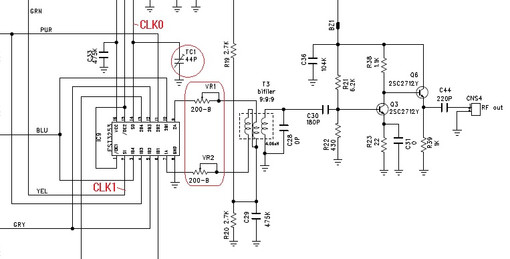

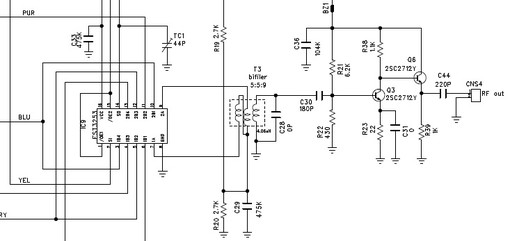

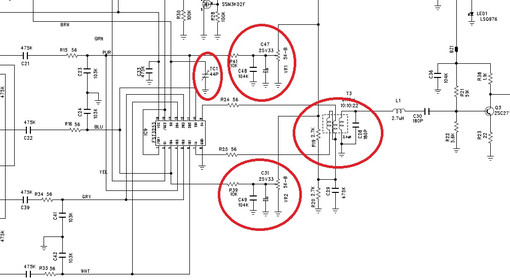

下の回路がアナログSW 2G66をFST3253に置き換えた、チューナーです。

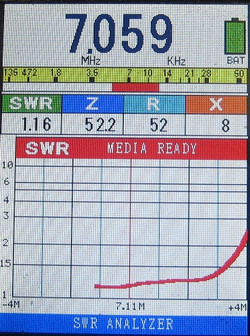

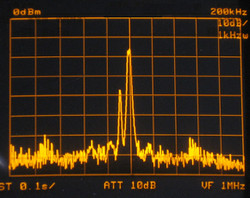

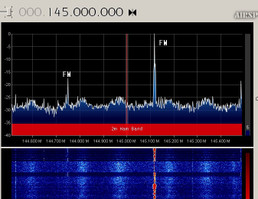

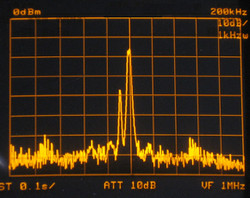

チューナー部分のみ配線完了したので、受信テストをしてみました。

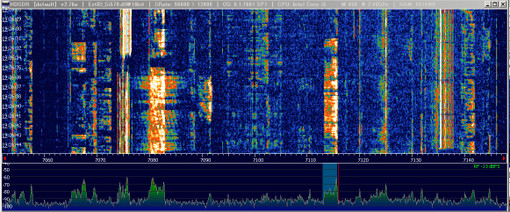

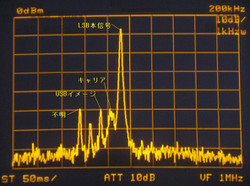

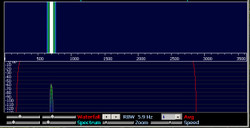

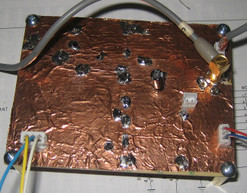

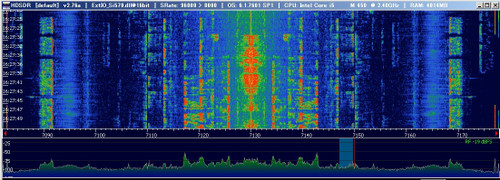

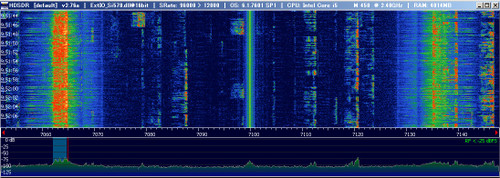

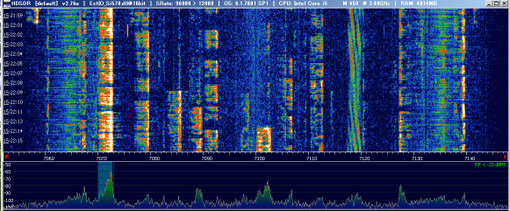

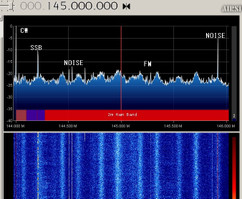

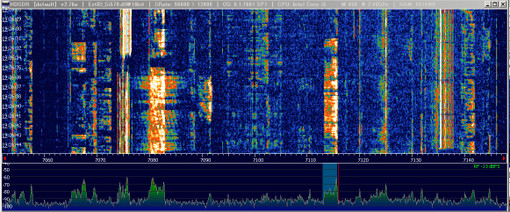

この直交復調器は、単なるスイッチングではなく、QSDと言われる回路構成で実現出来ており、HDSDR内にあるレベルと位相の補正機能をRESETした状態でも、イメージ(ミラー信号)がほとんど見えない状態です。 HDSDR内蔵の受信用IQバランス調整を根気良く行うと、USBイメージを-50dB以下に抑え込むことができます。 ここまで調整すると、サイドバンドスプラッタをまき散らしている局は簡単に判ります。 自分が送信するときは気を付けないといけません。

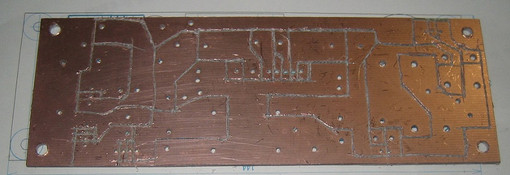

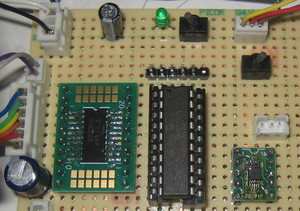

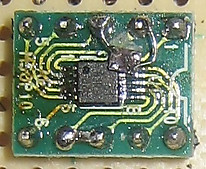

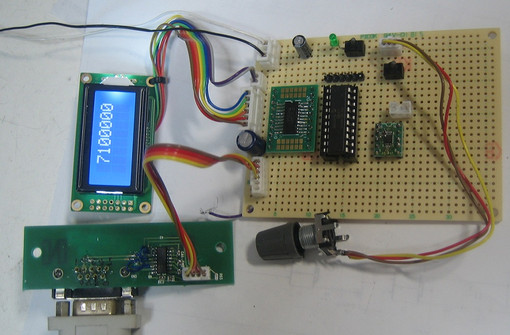

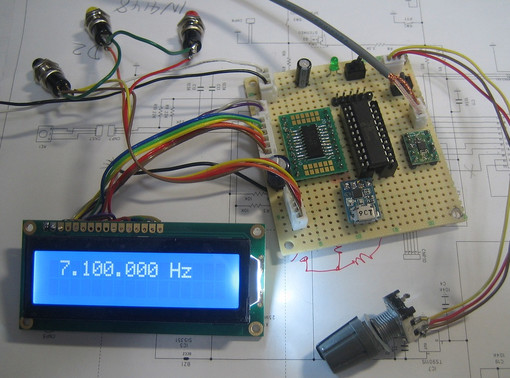

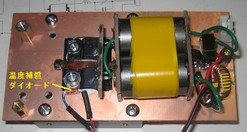

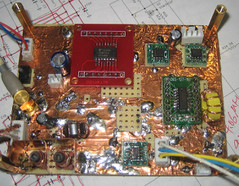

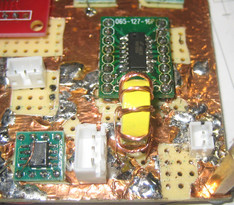

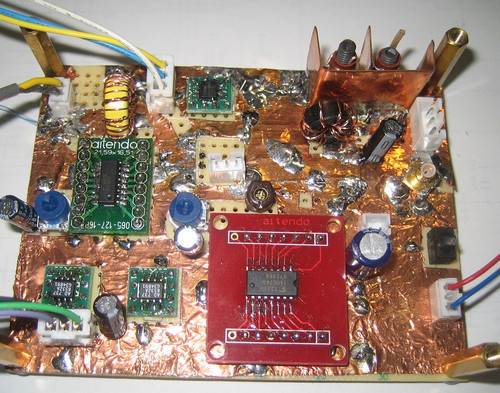

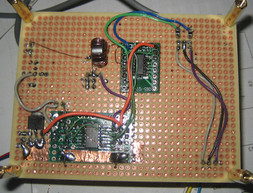

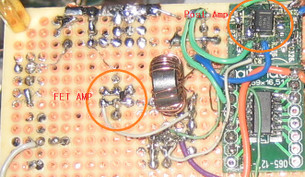

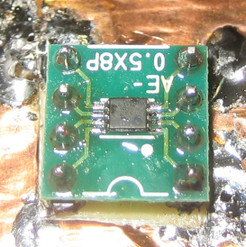

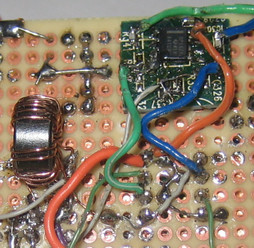

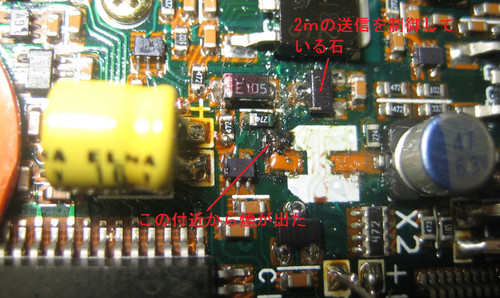

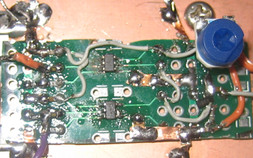

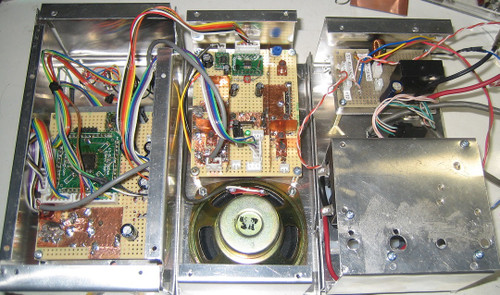

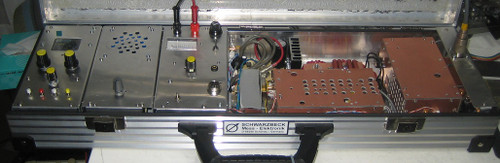

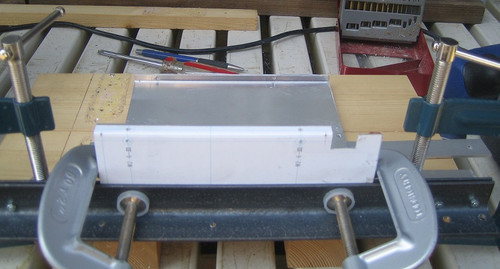

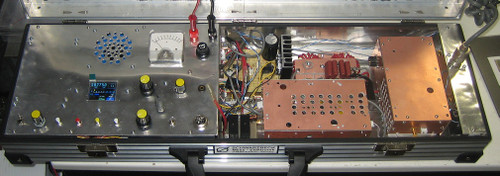

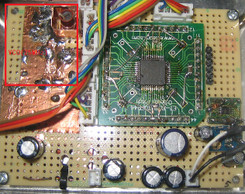

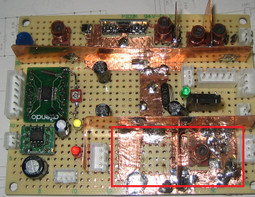

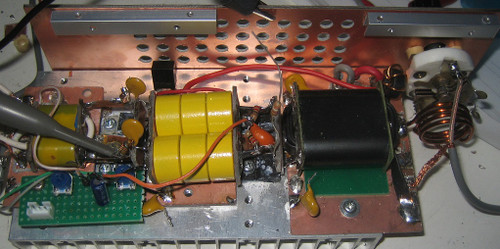

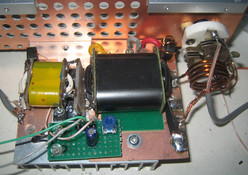

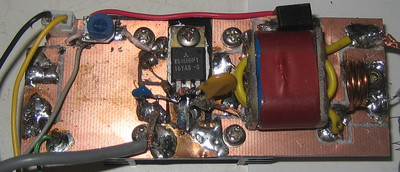

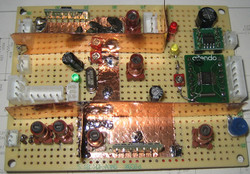

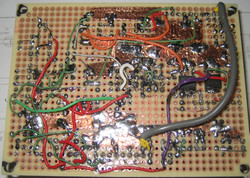

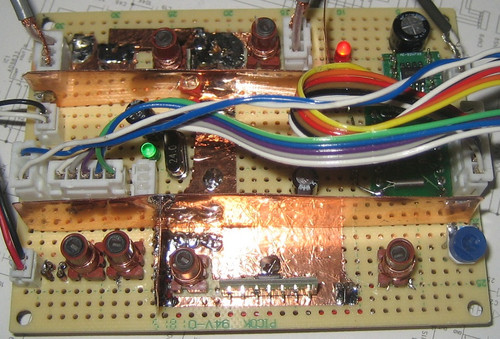

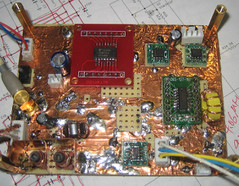

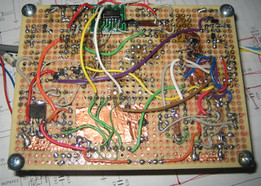

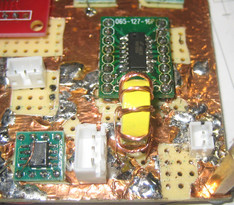

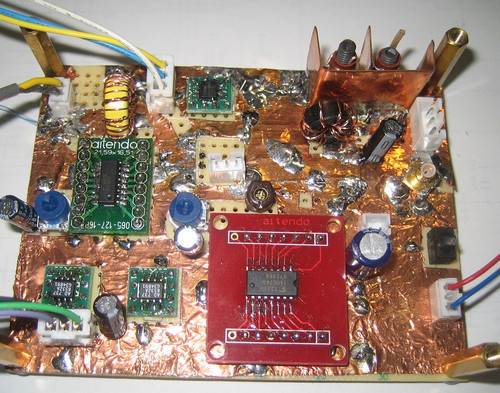

左上が直交変調回路まで実装した部品挿入面、右上は、そのチップ装着面です。 74HC74は赤色の変換基板に載せていますが、載せる前に2回もICを交換しました。原因は、ICの足を折り曲げて、2.54ピッチの基板に直付けしたのですが、折り曲げのストレスで、足が折れてしまい、やや大きすぎますが、これしか変換基板が無かったので、やむなくこの状態での実装となりました。 直交変調回路はSoftrockのQSE回路を実装しています。

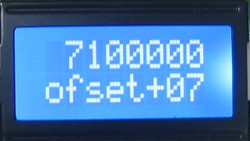

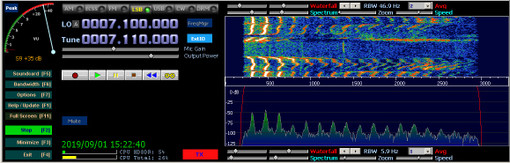

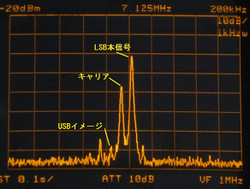

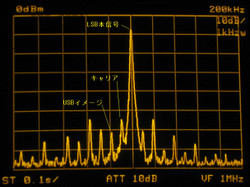

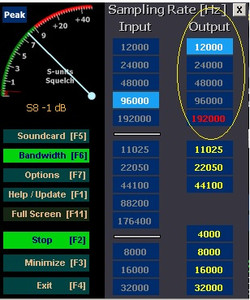

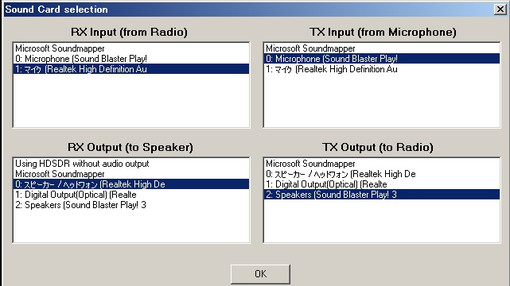

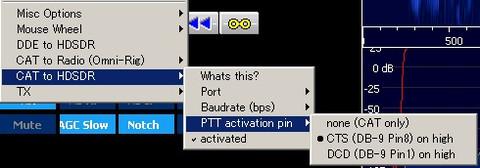

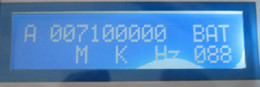

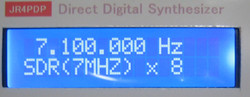

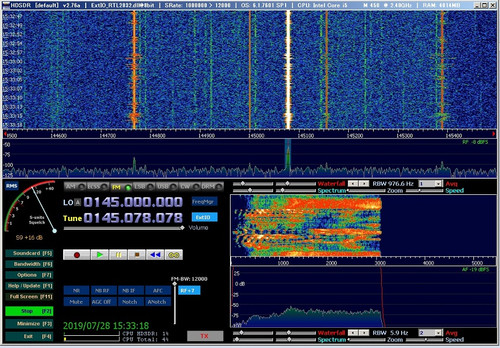

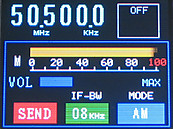

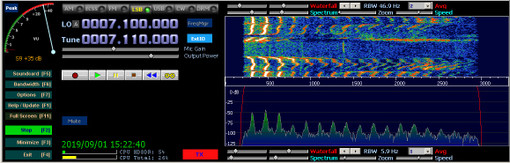

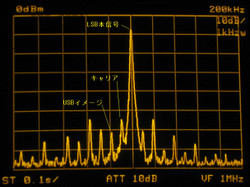

とりあえず、受信は快適に動いていますので、いよいよ送信モードの検討に入ります。 いくつかの配線ミスや端子間ショートがあり、7MHzのキャリアがQSEに供給されない状態を解消し、動作確認するまで、数時間かかりましたが、なんとか、LSBの信号をTS-930にて聞く事ができるようになりました。 その状態のHDSDRのショットが下です。

MICボリュームは半分よりやや下、Outputは75%くらいですが、MICに向かってしゃべると、右側のオーディオスペクトルが現れ、TS930の周波数表示が7110付近で0.3秒くらい遅れたLSBによる音声を聞く事ができました。SメーターはS9です。 ただし、ダイヤルをぐるぐる回すと、関係ない周波数でも、S9の言葉にならない信号が聞こえます。 多分イメージです。 TS930のモードをUSBにすると、はっきりと聞き取れます。 PCのサウンドカードの出力はIQ両信号とも出ていますが、QSEのICの入力にはQ信号のみが加わっています。 原因は、コンデンサの両電極間及び、IC端子間のショートでした。 また、拡大鏡を駆使してこれらの異常個所を修理し、QSE ICへI,Q信号両方が加わる事を確かめた後、再度TS930で受信すると、LSBの音声はS9までSメーターが振れますが、イメージ周波数のUSBの信号はS1しか振れません。 ただし音声は聞こえます。 ここは、完成度が上がった時点で送信時のI-Qバランス調整を行う事にします。

スペアナを多用していますが、スペアナが無くても、問題となる周波数は簡単に推測できますので、LSBの本信号を受信機で受信したとき、S9+40dBとか、+60dBをSメーターが指すようにATTや受信機のアンテナ入力への結合を調整して置けば、受信機のS メーターのみで、おおまかなレベル差を知る事ができます。 S9 から +何十dBの目盛は結構正確ですが、S ひとメモリのレベル差は言われる6dBである事は少なく4dBくらいであると思っておれば、ほぼ間違いありません。 なお、HDSDRの説明では、もう一台SDR受信機を用意して、バンドスコープを見ながら調整せよと書かれています。

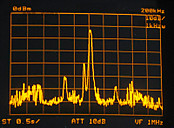

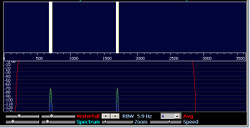

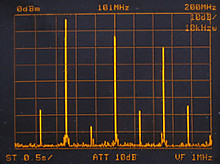

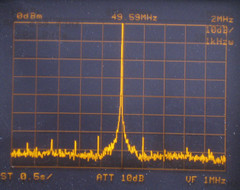

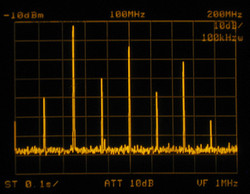

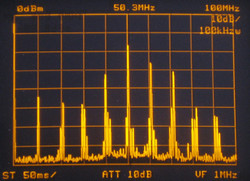

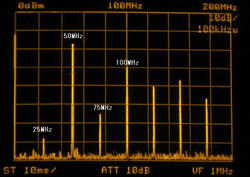

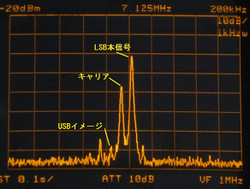

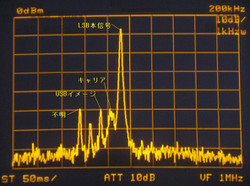

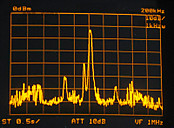

左は、7110KHzのキャリアを1KHzの正弦波で変調し、RF outにスペアナをつないだ状態でのスペクトルです。 ピークは7109KHz(スペアナの表示周波数は校正なし)のLSBで、左脇にあるのはレベルの高い方がQSEのキャリアである7100KHzの漏れ、その隣がUSBの漏れです。さらに外側に何かありますが、今の所なにが原因なのかは判りませんが、最終的にはこれもスプリアス規制以下に抑え込まないと送信は出来ません。 現在、ラフなIQバランス調整のみを行った状態ですが、回路定数を変える都度、このバランスが崩れますので、調整は最後にやらねばなりません。 キャリア漏れは、HDSDRを受信状態にしても出ていますので、これはIQ信号のバランスではなく、基板内の浮遊容量や誘導を受けるレベル差により、T3のバイファイラートランスで、キャンセル出来ていないと思われます。 現在の基板内配列はIQ信号路がシンメトリィになっていませんので、これが誘導を受ける差になっているのかも知れません。 予想したような展開になってきました。

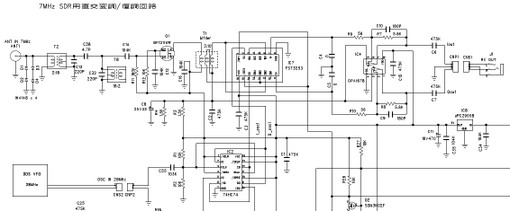

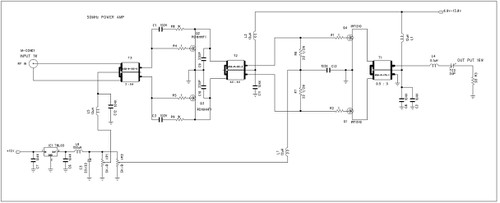

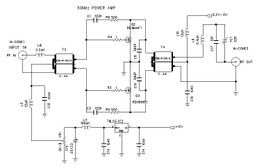

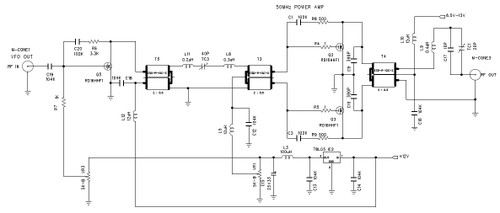

ここまでの回路図 SDR-TRX1.pdfをダウンロード

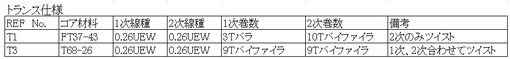

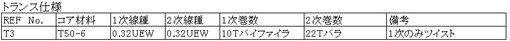

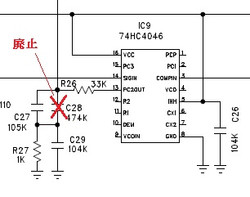

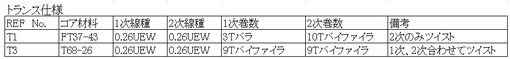

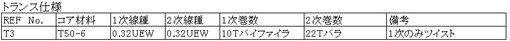

回路図の中に出てくるT1とT3のトランス緒元です。 手持ちのコアで適当に作りました。 特にT3は7MHzに共振するようなインダクタンスにしましたが、共振用のC28はゼロピコの時が最大のレベルとなっています。

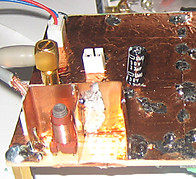

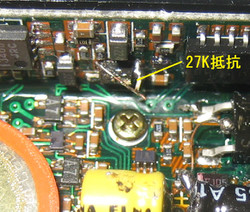

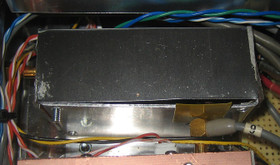

キャリア(7100KHz)漏れの検討です。 T3の配置がIQシンメトリィに配置されていなかった事、バッファのRF outアンプのコレクタ負荷となるコイルはオープンタイプで、外部から誘導を受けやすい事、などから、T3以降の回路を大幅に変更しました。

まず、QSEの出力にシリーズに挿入された56Ωの抵抗は200Ωの半固定抵抗に変更しました。T3のバッファアンプは2石構成のアンプとし、出力はエミフォロで取り出します。 (後日、エミフォロは廃止しました)

まず、QSEの出力にシリーズに挿入された56Ωの抵抗は200Ωの半固定抵抗に変更しました。T3のバッファアンプは2石構成のアンプとし、出力はエミフォロで取り出します。 (後日、エミフォロは廃止しました)

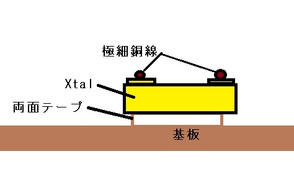

今まで、QSE ICの横に有ったT3はICと同一列のセンターに配置し、IC出力からT3の各巻線にシリーズに200Ωの半固定抵抗を追加しました。この半固定抵抗はチップタイプの極小品で、過去使い道が無かったのですが、やっと日の目を見ました。マイナスの時計ドライバーで回す事が出来ます。 バッファ回路の総面積も従来の1/3くらいに縮小し、他の回路から影響を受けにくくしました。

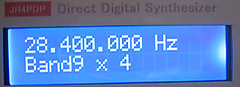

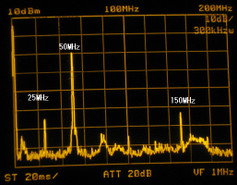

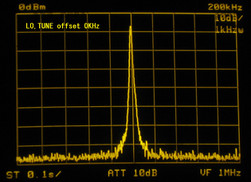

この状態で、キャリアもれが最少になるように、半固定を調整した場合、LSBに対して-18dBくらいしか減衰していなかったものが-28dBくらいまで改善しました。 まだ不足です。 IQキャリアの位相をいじってみる為、IC9の14番ピンとGND間にバリコンを接続し、キャリア減衰が最大となるよう調整すると、44PFの時、最大となり-42dBを確保できました。 その時のスペクトルが左の状態です。 この時、USBイメージは-42dBくらいになっていますが、これはHDSDRのバランス調整でノイズレベルまで下げられる事は確認しています。 バリコンは臨時に追加したものなので、バリコンの代わりにトリーマーを追加する事にします。

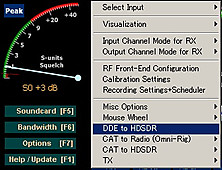

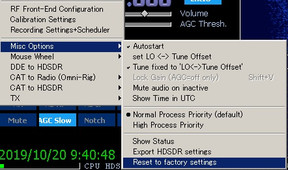

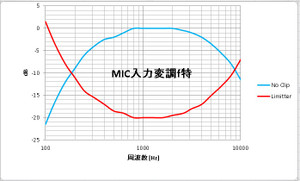

50W以下の送信機に課せられたスプリアス規制値は、LSBの3KHz帯域の中心を基準に、1.5KHzの信号で変調した、定格出力の80%の出力を基準として、±7.5KHzの範囲が、-40dB、+/-7.5KHz以上離れた領域は-50dBです。 HDSDRの解説ページでは10KHzのオフセットをデフォルトに設定しており、米国やEUの規格は全スプリアス領域で-40dBですから、このままでも使う事ができます。 日本では、HDSDRのFOとTUNEのオフセットを8KHz以下にすれば、キャリア周波数が、±7.5KHz以内に収まりますので、ここは-40dBが適用されますが、不明と書かれたスプリアスは ±7.5KHzを超えますので、-50dB以下にしないと送信できません。 詳細を調べたところ、一番左に現れるスプリアスは、変調のレベルが高すぎて、歪が生じたものである事がわかりました。 変調信号のレベルを適正値以内に押さえれば、出なくなるようです。 しかし、同時にLSBの本信号もさがりますので、今度はキャリア漏れとのレベル差を確保できなくなります。

ここまでの回路図 SDR-TRX2.pdfをダウンロード

キャリア漏れの再検討です。 Softrockのトランス情報によれば、T3の2次側は約2.4uHのインダクタに設定し、1次側は、2次の巻数の1/2のコイルをバイファイラー巻で直列に接続してあります。 その時の2次側の巻き数は30Tです。 私の手持ちのカーボニルコアの場合、9Tのとき、2.3uHのインダクタを得る事が出来ます。 巻き数比を同等にすると、1次は5Tのバイファイラ巻となりますので、このT3を下記の緒元で作り直す事にしました。

このトランスを実装してテストすると、キャリア漏れは若干改善しましたが、どうも不安定です。 不安定の原因はトランス入力にシリーズに入っている半固定みたいで、この超小型半固定抵抗が接触不良を起こしているみたいですので、これを廃止しました。

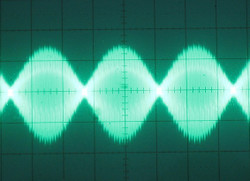

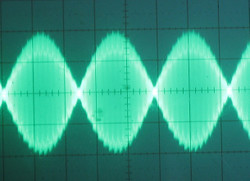

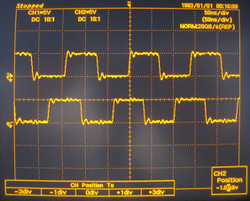

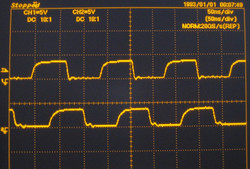

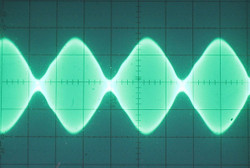

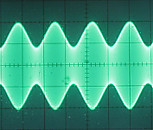

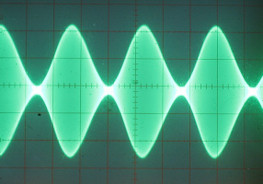

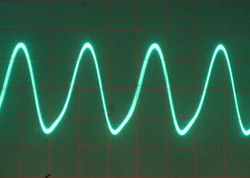

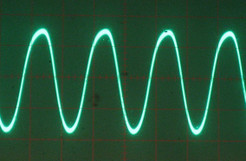

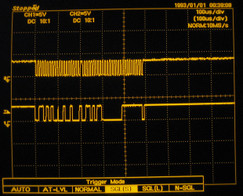

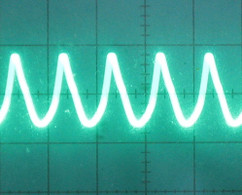

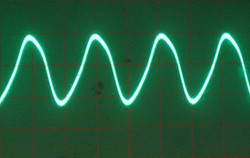

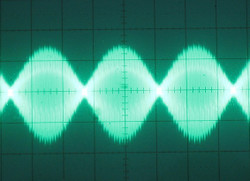

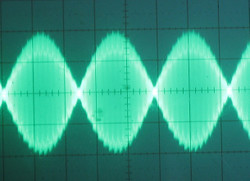

その状態が上の回路です。 この回路で、44PFのトリマーを回すと最大で-30dBくらいまでキャリアが減衰し、安定しています。 そして、今まで見る事が出来なかった2信号変調時の見慣れたSSB波形を、やっと見る事が出来ました。

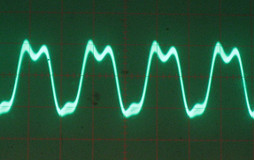

ただし、この波形も良く見ると上下非対称です。DSPの処理の問題か? OPアンプを含めたハードの問題か?

このレベルからアップすると、目に見えて上側の先頭値がつぶれます。

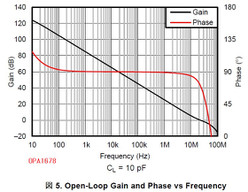

インターネットで調べていくと、この歪は、OPアンプの出力ドライブ能力が原因で、決まって片方向の波形からつぶれていくものらしいという事が判りました。 要は負荷インピーダンスが小さすぎて、OPアンプの出力電流制限機能が働いて、歪んでしまうのだそうです。

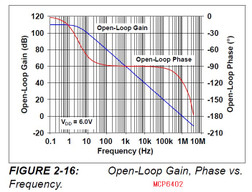

よくよく考えると、T3の2次側のインダクタンス2.3uHの7MHzにおけるインピーダンスは、約100Ωで、1次側はこの半分の巻き数ですから、約25Ωくらいしかありません。 これをMCP6402という最少出力インピーダンスが200ΩくらいのICでドライブしている関係から歪んで当然でした。

じゃあ、なぜSoftrockはこんな低いインピーダンスのトランスを使ったのか、不思議でなりません。 QSE ICの前段に使われているOP AMPは、TLV2462CDという、聞きなれない品番です。 これを調べてみたら、ドライブ能力が非常に高い、高電流出力用のOP AMPでした。

その後、調べてみました。 直交ミキサーと言われるIC化されたIQ変調回路は、ギルバートセル・ミキサーと呼ばれる回路を基本として、ふたつの周波数成分を乗算するのだそうですが、この時の乗算は電圧ではなく電流で実現されているのだそうです。 今回のミキサーはICで構成されている訳ではありませんが、ミキサーとしての乗算は、低インピーダンスにしてやらないと、うまくいかないみたいです。 受信時のミキサーに於いて、OPアンプを反転入力にして、低インピーダンスで受けるのも、この理由によるもののようです。

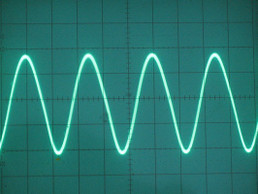

私が、今製作中の、TRXは7MHzオンリーですので、広帯域性は要求されません。 キャリア漏れやIQバランスが理由なら、NGですが、単純に共振モードを使わないトランス(広帯域トランス)の場合、歪やキャリア漏れがどのようになるのか試してみる事にします。 これは、Softrockで使っているカーボニルコアやICが日本では簡単に手に入らない事も理由のひとつです。 左の波形は、T3を、この高インピーダンストランス(コア材はFT37-43)に変更した時のSSB2トーン変調波形で、上下ともほぼ対称で、振幅も2Vppあります。

これから、キャリア漏れやスプリアスの状況を確認しながら、見ていきます。 下は、その時のT3のトランス緒元です。

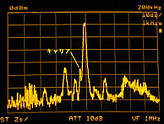

このトランスの場合、2次側が135uHくらいのインダクタンスとなり、7MHzでのインピーダンスは5KΩを超えます。 この状態では、トランスの後のトランジスターアンプのベース抵抗430ΩがそのままT3の1次側へ影響しますので、1次側のI,Qそれぞれの負荷インピーダンスは約300Ωです。 まだ、過負荷に近いので、ベース抵抗を5KΩくらいまで上げたいところです。 これを確かめるため、R22を430Ωから5.6KΩに変更し、R21も68KΩに設定した上で、T3の2次側に51Ωの抵抗をGND間に追加し、実質の負荷抵抗を小さくしてみました。 その時のキャリア漏れが一番左のデータです。

負荷インピーダンスが下がって、キャリアのピーク値は-40dBくらいに」なりましたが、同時にLSBレベルも-14dBくらいとなり、その差は26dBです。 真ん中のデータは51Ωの負荷抵抗を無しにしたものです。当然キャリア漏れは-46dBくらいまで増えましたが、LSBの信号も-10dBまで上昇し、結果として、キャリア差は36dBまで改善しました。 さらに、真ん中の状態のままで、74HC74からFST3253までのキャリア接続ラインをねじりかつ長さ20mmのフェライトコアを入れたのが一番右側です。キャリア漏れは-46dBくらいですが、LSB信号が2dBくらいアップした為38dbまで改善しています。 しかし、一応Softrockが提示する低インピーダンストランスに比べて、あきらかにスプリアスは増加しています。(最初のスペアナデータ参照)

直交変調回路が低インピーダンスで構成されるのは、このミキサーが電流で動作している事によるものだそうです。 ICデバイスメーカーがこの直交変調回路をIC化していますが、それらのICは決まって放熱設計を重要視しています。大きな電流を必要とするみたいで、ICの消費電力が数Wというものも存在します。 上のデータで2次側の負荷抵抗を51Ωにして比較したのは、間違いで、1次側の負荷コイルに沢山の電流が流れるようにしなければなりません。 その為には、ミキサーICの出力に直接コイルをつなげば良いのですが、そうすると、負荷が余りに小さすぎてOPアンプが歪ますので、ICとコイルの間に49.9Ωを入れてあるのが、Softrockの回路となります。 当初私もSoftrockにならって56Ωのシリーズ抵抗を入れたのですが、使用しているOPアンプのドライブ能力不足(出力インピーダンス200Ω)により、歪が発生し、余計なスプリアスやキャリア漏れを招いたようです。

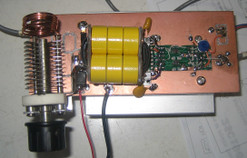

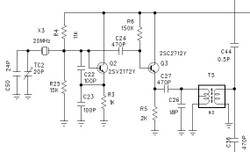

そんな訳で、SoftRockの回路の設計方針に戻り改善策を検討する為、部材探しを行い、まずベースバンドのバッファーアンプとしているOP AMP MCP6402をドライブ電流250mAというAD8532ARに変更しました。 さらに、T3もトロイダルコア T50-6に変更し、以下の緒元としました。

このトランスの2次側インダクタンスは2.4uHです。

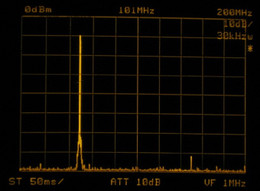

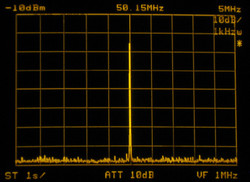

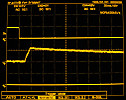

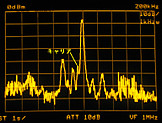

そして、送信状態でのスプリアスデータが左の画像です。

センターは1KHzのLSB信号でその左がLOのキャリア漏れです。-20dBくらいしか減衰していません。 しかし、今までその左にあったUSBのイメージや、不明としてきたスプリアスもかなり小さくなり、ノイズに埋もれるまで改善しました。

やはり、OP AMPの歪がかなり影響していた模様です。 キャリア漏れを対策して、±70KHz付近のノイズをベースバンドのフィルターで対策出来れば、後は、キャリア漏れのみとなります。 誤差5%の抵抗と、蛇の目基板に組んだ回路構成では、無理が有るのは承知していますが、なにか改善アイデアを考える事にします。

アナデバの技術解説のなかで「笑い飛ばせないゼロIFの課題」という記事を見つけました。 この主題はIQミキサに於いて、LO(ローカルオシレター)の漏れについて解説した記事です。 この記事は、ICの中で構成されるIQ変調回路のLOの漏れを、別に設けたIQミキサーによる復調回路を使って検出し、レベルと位相の差分に相当する直流信号を、IQ変調回路のDCバイアスとして加え、自動的にLO漏れを-81dBくらい確保できるようにする技術の説明です。 LOキャンセルを自動で行う回路を蛇の目基板上にディスクリートで作る事は、まず不可能ですので、半固定抵抗で、DCバイアスを可変し、最低-40dBくらいのキャリア抑制ができないか、実験してみる事にしました。

DCバイアスを可変する為に、VR1,VR2 5K-Bの半固定抵抗を追加し、そのセンター端子から10KΩの抵抗を介して、IC5の出力に相当するラインの2か所に接続します。 ふたつのVRと、44Pのトリーマー(実際は60Pのトリーマー)を交互に調整し、キャリアリークが最少となるようにします。

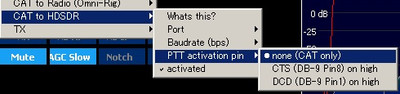

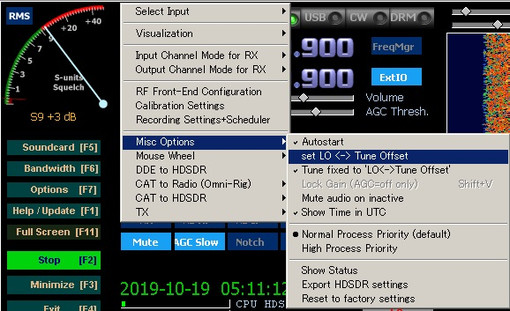

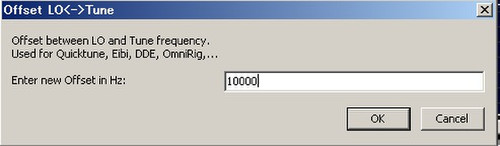

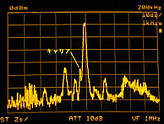

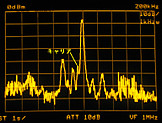

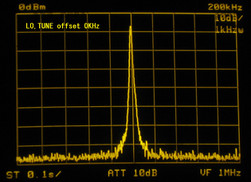

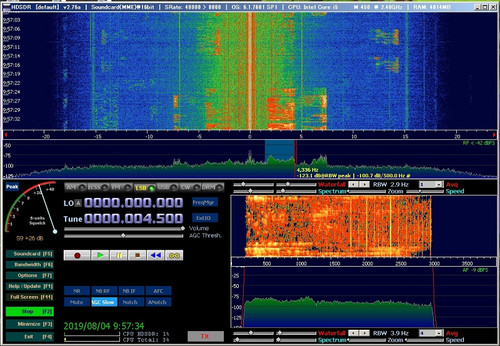

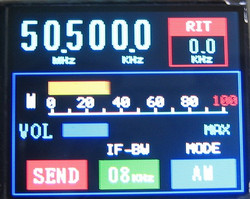

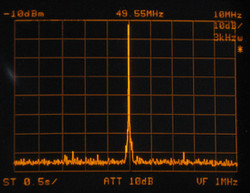

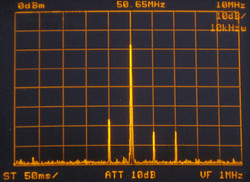

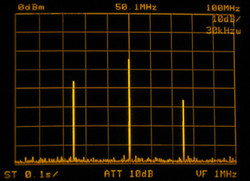

左上のスペクトルは、ラフ調整ですが、LSBに対して-47dBくらいまで、キャリアを減衰できました。USBのイメージもHDSDRのキャンセル機能で、-50dB以下に抑える事ができます。 それ以外にスプリアスが見えます。 このスプリアスはHDSDRのLOとTUNEの周波数を一致させると、右上のスペクトルのように、ぴたりとなくなります。 HDSDRの解説によれば、スプリアスが無くなるのでは無く、全てのスプリアスが狭い帯域に閉じ込められるとの事。 その為、変調音に歪や周波数特性の異常が生じる可能性があるけど、スプリアス対策としては有効みたいです。 ただし、AMではセロoffsetは使えないと記述されています。

ここまでの配線図 SDR-TRX4.pdfをダウンロード

RF outのQ6エミフォロは時々発振しますので、廃止しました。

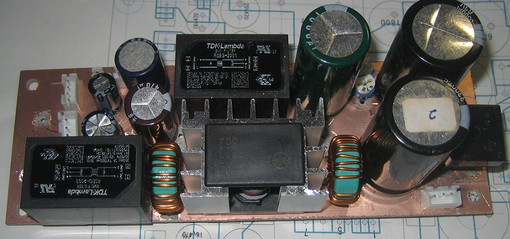

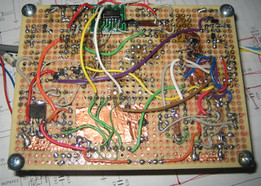

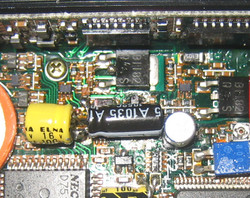

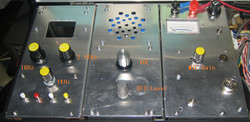

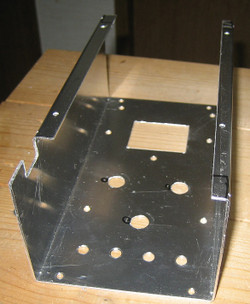

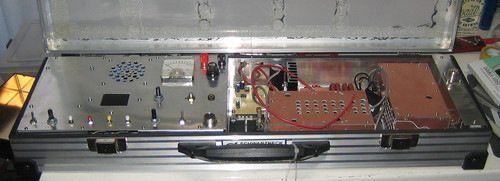

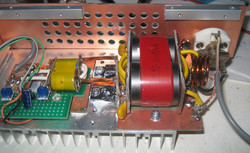

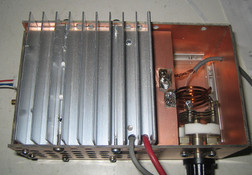

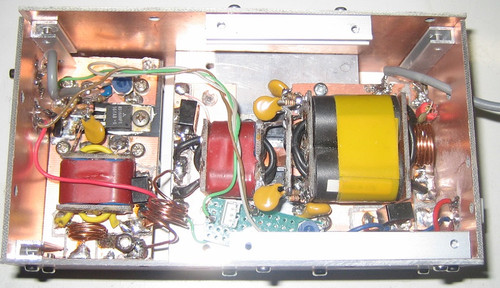

直交復調と変調回路が載った基板状態です。

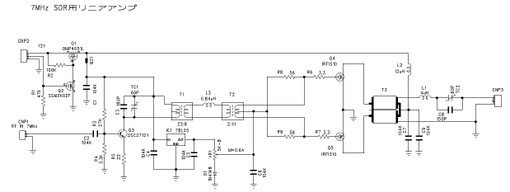

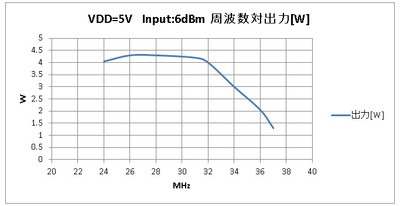

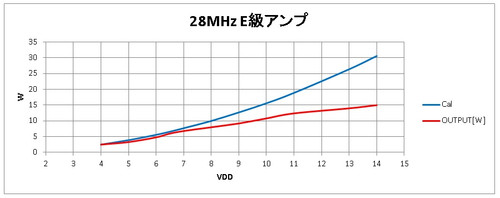

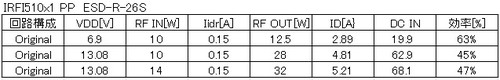

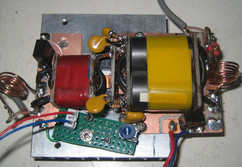

現在のRF出力はスペアナの表示で-8dBmくらいですが、これを3Wくらいまで増幅するリニアアンプの製作にやっと進めるようになりました。

リニアアンプが完成し、いざ、実際の交信を開始すると、キャリア漏れをアナログのキャンセル技法で対応している、QSE回路の限界が見えてきました。

SDR用 7MHz QRPリニアアンプの製作 へ続く。

INDEXに戻る

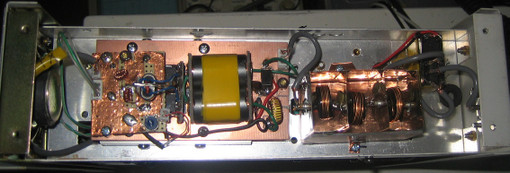

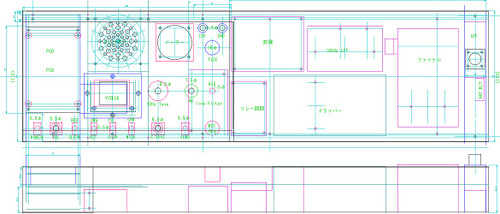

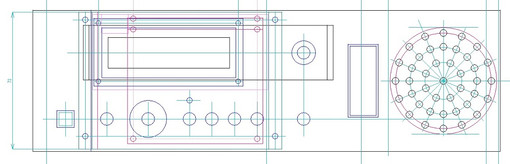

元が周波数カウンターでしたので、周波数を表示するLEDが8個並んだ表示部がありました。 ここにLCDの窓が収まるようにデザインを決め、右端の入力端子エリアはスピーカーを取り付ける為、穴をいっぱい開け、付属していたレベルメーターは、目盛板を書き換えて、電源の電流計に変更します。

元が周波数カウンターでしたので、周波数を表示するLEDが8個並んだ表示部がありました。 ここにLCDの窓が収まるようにデザインを決め、右端の入力端子エリアはスピーカーを取り付ける為、穴をいっぱい開け、付属していたレベルメーターは、目盛板を書き換えて、電源の電流計に変更します。 電源基板を組み立てる時、ハンダのタッチ部分を修復する為に、ハンダ吸い取り編線を部品箱から探しだし、いざ使おうとすると、フラックスが全くしみこんでいない、ただの編線でした。 2個買ったのに、2個とも同じです。 どこから買ったのか忘れましたが、多分、何に使うか判らない業者が、コピー品を作り、安く売り込んだのでしょうが、それを、売っている販売会社も使い方をしらないのでしょうね。 仕方がないので、フラックスのビンの中に編線を押し込み、フラックスをしみこませた後、半日、日光で乾燥させて自作しました。

電源基板を組み立てる時、ハンダのタッチ部分を修復する為に、ハンダ吸い取り編線を部品箱から探しだし、いざ使おうとすると、フラックスが全くしみこんでいない、ただの編線でした。 2個買ったのに、2個とも同じです。 どこから買ったのか忘れましたが、多分、何に使うか判らない業者が、コピー品を作り、安く売り込んだのでしょうが、それを、売っている販売会社も使い方をしらないのでしょうね。 仕方がないので、フラックスのビンの中に編線を押し込み、フラックスをしみこませた後、半日、日光で乾燥させて自作しました。