<RFパワーアンプ(リニアアンプ> [FET TR 自作 2SK1530]

スーパージャンクションFETの放熱の限界が見えて、200Wリニアアンプの開発は頓挫していましたが、今になって考えれば、FETを3個も小さな銅片に集中させた事が熱暴走の主因だったと気がつきましたので、まだ諦めきれません。 大きな放熱板にFET1石のみを半田付けした銅板を間隔を開けて実装すれば、200Wも可能かも知れません。いつか再トライしたいと思います。

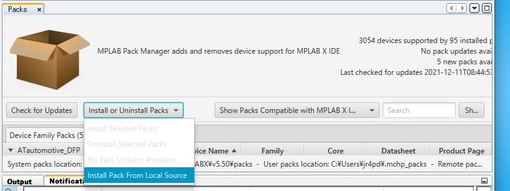

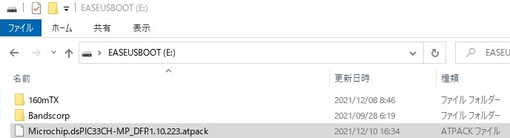

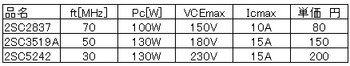

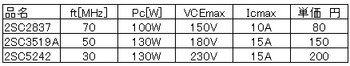

スーパージャンクションFETの代わりに最新の高fTのトランジスターは使えないものかと、実験を開始しました。 トランジスタは全て秋月で入手できるものばかりです。 用意したのは、時間的な差はありますが以下の3種類です。

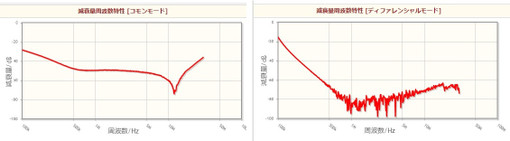

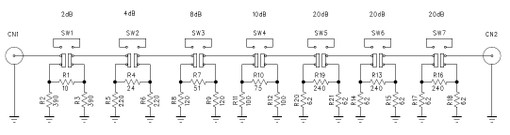

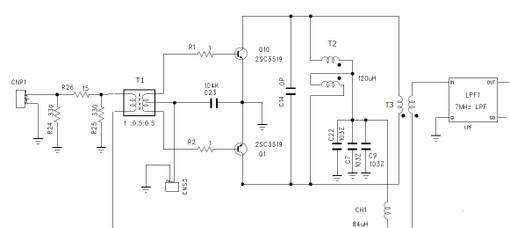

全て、オーディオパワーアンプ用ですが、沢山の種類の中から、fTが高そうな石をピックアップしました。 PCの大きさから、プッシュプル回路で、効率が50%とした時、1石のPC相当が出力電力となりますので、いずれも100Wアンプをめざし、それが実現したら、電力合成で200W出力を得ることにします。 今まで、出力の確認はLPFなしの状態で測定していましたが、歪波形の場合、効率が100%を超える事があり、あきらかに誤計測していますので、以降全て7MHzのLPFを通した後の出力をクラニシの電力計で測る事にします。

全て、オーディオパワーアンプ用ですが、沢山の種類の中から、fTが高そうな石をピックアップしました。 PCの大きさから、プッシュプル回路で、効率が50%とした時、1石のPC相当が出力電力となりますので、いずれも100Wアンプをめざし、それが実現したら、電力合成で200W出力を得ることにします。 今まで、出力の確認はLPFなしの状態で測定していましたが、歪波形の場合、効率が100%を超える事があり、あきらかに誤計測していますので、以降全て7MHzのLPFを通した後の出力をクラニシの電力計で測る事にします。

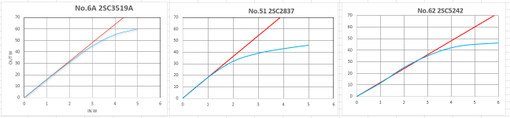

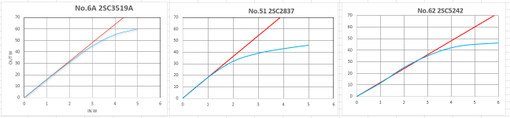

上のグラフは、候補の3石でリニアアンプを構成した時の入力対主力特性です。VCCは40V、出力トランスは1:4のインピーダンス比に固定した時のデータです。 青色が実測値、赤色は理想特性です。 この中で、最も出力が大きいのはサンケンの2SC3519Aで、他の2石は20%以上少なくなりました。 従い、以降、2SC3519Aに絞って検討する事にします。

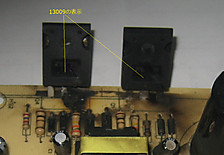

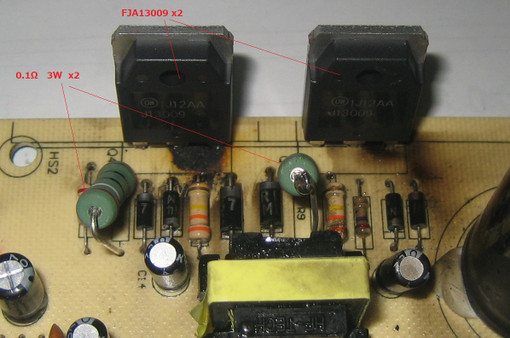

この2SC3519AはVCC=50Vくらいから熱暴走が起こります。 オーディオアンプの場合、エミッターに抵抗を入れるのは常識ですから、この石も抵抗を入れる前提で設計されているのではと考え、以後、0.1Ωのエミッター抵抗を入れ、かつ温度検出用のダイオードは、TRと共締めするのではなく、コレクタフィンに密着させ、かつシリコングリスで覆う事で、70V電圧でも熱暴走する事はなくなりました。

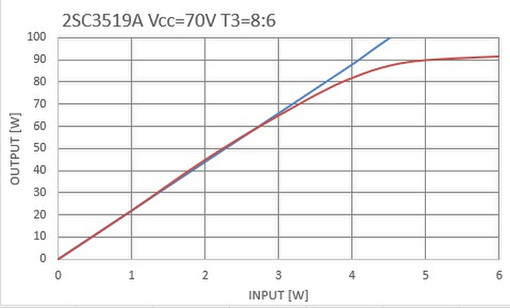

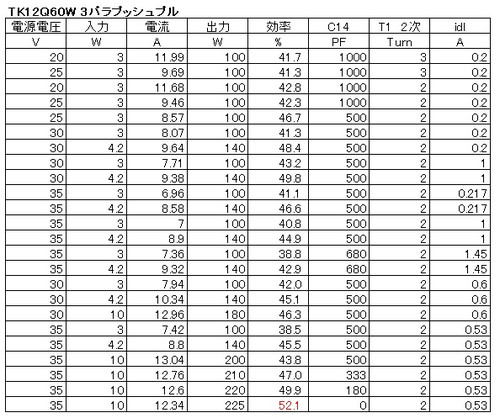

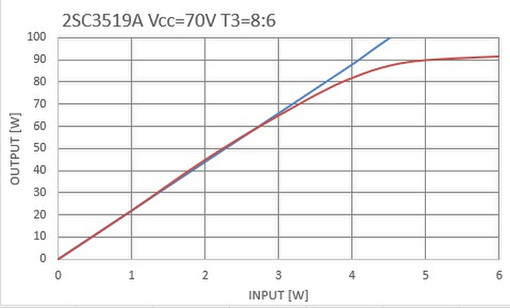

2SC3519Aを70Vの電源で動作させ、最大出力が得られるようにT3の巻き数比を調整した結果が上のデータです。 この時の最大効率は40%くらいでした。 5W入力で90W得られていますが、これはCWの時のみ利用出来る出力で、SSBの場合、少し歪みますが70Wくらいが限界と思われます。 Vccの電圧をこれ以上、上げると、負荷電流が3Aを超えるに伴い電圧が下がってきますので、レギュレーションを確保出来る限界です。 仮に80Vまで上げたとしてもSSB推定出力は91Wくらいです。

この回路で100W以上出す事が出来たら、2台用意して電力合成し、200Wを達成するつもりでしたが、あきらめました。

次は、SiCを含めて MOSFETの安いものが無いか探す事にします。

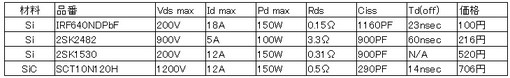

SiC構造で、1000円以下のFETを探すと、何石か候補が出てきます。 それらのspecを眺めていると、普通のSi構造のFETでも似たような特性を持つFETが、存在します。

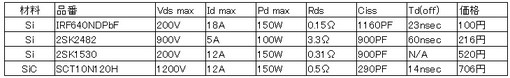

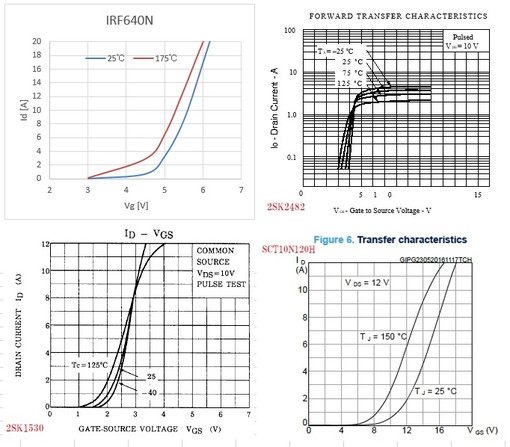

上の表に有るFETは、上から順に、E級アンプに良く利用されるIRF640、サムウェイがHF 500Wアンプに使用している2SK2482、JA1QVM OMがブログ上で紹介しているオーディオパワーアンプ用の2SK1530、1000円以下で買えるPd=150WクラスのSiC FET SCT10N120H。 一番下のSiC FETを使ったリニアアンプの記事は、まだ見つかっていませんので、本当にHFのリニアアンプに使えるかは不明です。

その中で、IRF640に注目しました。 このFETはEクラスアンプでの使用例はWEB上に沢山ありますが、リニアアンプに使った例を見た事が有りません。 specシートを見た状態では、Ciss以外、SiC FETに匹敵する数値を示すのに、なぜ使われていないのか? 手元にチップタイプのIRF640Nが2石有りましたので。これを使い確認する事にしました。

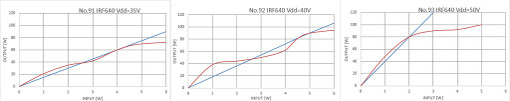

上のグラフは、IRF640Nをリニアアンプとして、使用した時の入力対出力特性です。 使ったチップタイプ(表面実装用)のFETを20mm x 30mmの銅板にハンダ付けし、この銅板を放熱板に固定したもので、温度補償用のダイオードは0.3mmの銅板に包んで、ドレインの近くにハンダ付けし、かつ、熱暴走を防止する為、ソースに0.1Ωの抵抗を入れてあります。 青色の直線がリニアリティOKの理想カーブを示しますが、赤色の実測データは、とてもリニアリティが確保されているとは言い難いカーブをしています。 このFETはスィッチング用ですから、VgとIdの間にリニアリティは必要なく、その特性は全く考慮されておりません。 Vddをもっと上げたら改善するのだろうかと、50Vまで上げ、5W入力を10W入力にしたとたん、FETが煙を出して死にました。 このFETではリニアアンプを作れない事が判りましたので、ここで検討は終了です。

上のグラフは、IRF640Nをリニアアンプとして、使用した時の入力対出力特性です。 使ったチップタイプ(表面実装用)のFETを20mm x 30mmの銅板にハンダ付けし、この銅板を放熱板に固定したもので、温度補償用のダイオードは0.3mmの銅板に包んで、ドレインの近くにハンダ付けし、かつ、熱暴走を防止する為、ソースに0.1Ωの抵抗を入れてあります。 青色の直線がリニアリティOKの理想カーブを示しますが、赤色の実測データは、とてもリニアリティが確保されているとは言い難いカーブをしています。 このFETはスィッチング用ですから、VgとIdの間にリニアリティは必要なく、その特性は全く考慮されておりません。 Vddをもっと上げたら改善するのだろうかと、50Vまで上げ、5W入力を10W入力にしたとたん、FETが煙を出して死にました。 このFETではリニアアンプを作れない事が判りましたので、ここで検討は終了です。

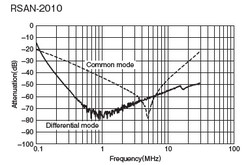

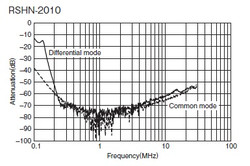

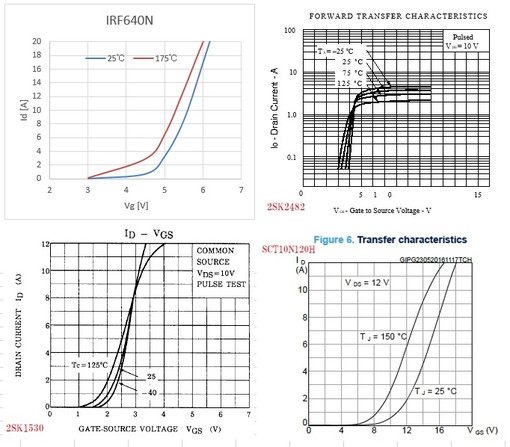

そこで、IRF640はリニアアンプには使えないが、2SK2482や2SK1530はなぜリニアアンプに使えるのかをデータシートの中から、考察しました。

リニアアンプのリニアリティを見る場合、Vg対Id特性が一番重要ですので、上の4石のFETのVg対Id特性を抜粋しました。 IRF640と2SK2482はIdが対数目盛で作成されていましたので、IRF640のみ、リニア目盛に書き換えてあります。 このグラフを見ていると、どのFETでもグラフの線がほぼ直線になる条件は存在しますが、IRF640の場合、動作領域となるId 3A以下の部分では、直線となっていません。 またリニアアンプとして実績のある、2SK1530はその動作域(1A~5A)で、1A付近はアイドル電流でカバーするとすれば、直線に近くなっています。 特に2SK1530はオーディオアンプ用ですから、このリニアリティの確保に最重点を置いたFET設計になっているのでしょう。

リニアアンプのリニアリティを見る場合、Vg対Id特性が一番重要ですので、上の4石のFETのVg対Id特性を抜粋しました。 IRF640と2SK2482はIdが対数目盛で作成されていましたので、IRF640のみ、リニア目盛に書き換えてあります。 このグラフを見ていると、どのFETでもグラフの線がほぼ直線になる条件は存在しますが、IRF640の場合、動作領域となるId 3A以下の部分では、直線となっていません。 またリニアアンプとして実績のある、2SK1530はその動作域(1A~5A)で、1A付近はアイドル電流でカバーするとすれば、直線に近くなっています。 特に2SK1530はオーディオアンプ用ですから、このリニアリティの確保に最重点を置いたFET設計になっているのでしょう。

こういう風にみると、SiCのSCT10N120Hもリニアアンプとしてそこそこ使えるかも知れません。 ただし、1000円を切ったとは言え、簡単に飛ばせる価格ではないし、どこのメーカー品を見ても、Vg対Idの温度依存性がSiに比べて4倍くらい悪化しています。 とりあえず、SiCではありませんが、通販サイトで入手した2SK1530で実験を再開する事にします。

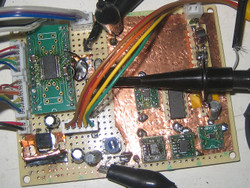

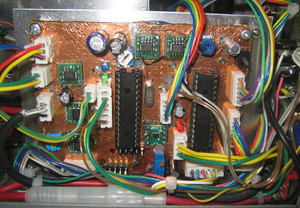

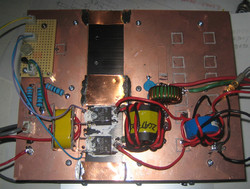

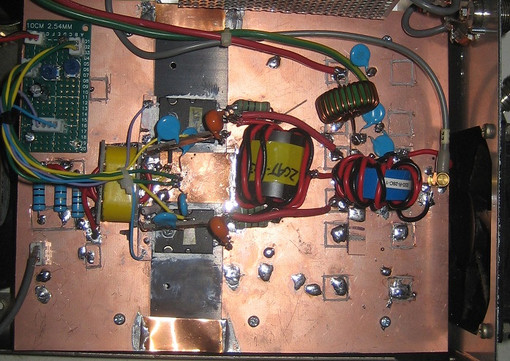

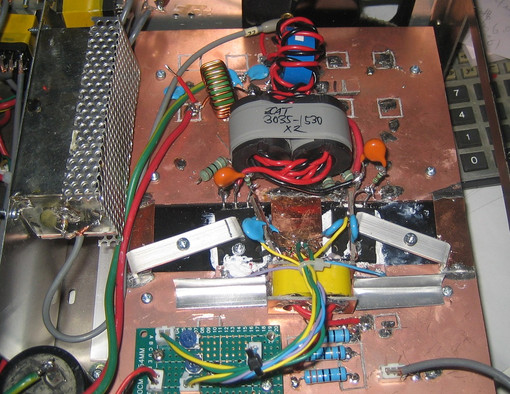

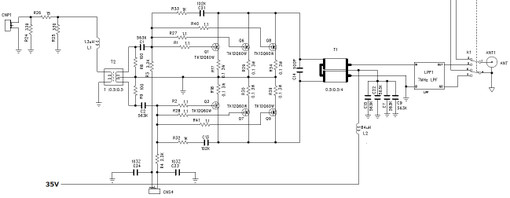

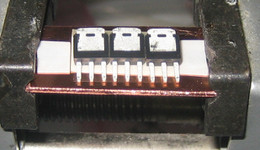

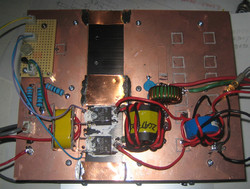

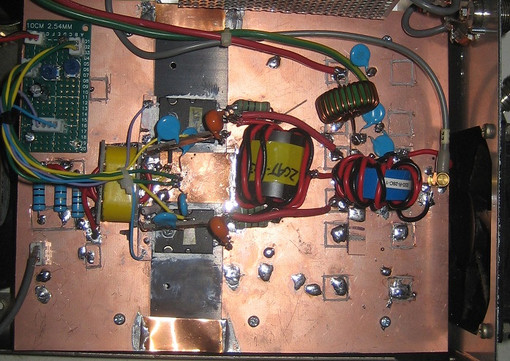

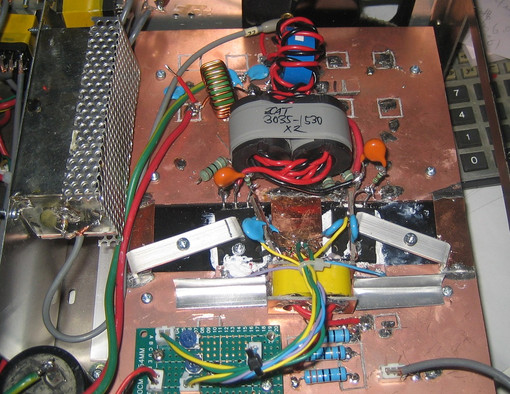

190 x 165 x37mmのサイズの放熱板に2SK1530 2石と入出力トランスをマウントし、オリジナルの紹介回路図とは少し異なる回路で検討をスタートしました。 ファンは臨時に直径14cmの扇風機を使用しています。

最初、2石のアイドル電流の調整を1個の半固定VRだけにして、2石合計で0.8Aに設定したのですが、出力が出ません。 入力レベルを1Wにしても、電流だけは4A以上流れますが出力が有りません。 どうも出力トランスで、PPの出力がキャンセルされているようです。 そこで、2石のアイドル電流を個別に測ってみました。 一方が0.7A、もう片方が0.1Aで、0.1A側の出力は位相が反転せず、2石が同相となっていました。 結局、通販で買った4石のFETの特性はバラバラで、アイドル電流は個別に合わせないとアンプとして動作しない事が判りました。 バイアス回路を変更し、アイドル電流を個別に調整できるようにしました。

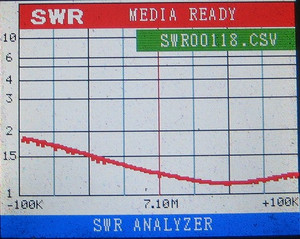

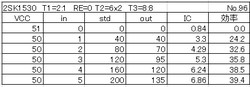

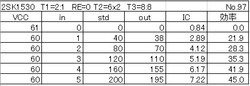

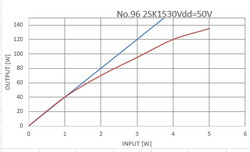

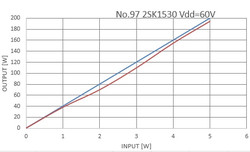

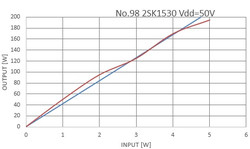

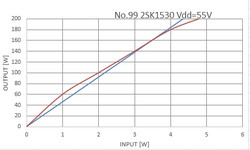

一応出力が出るようになりましたので、Vd=50Vと60Vでテストしてみました。 入力端子のSWRは1.7くらいです。

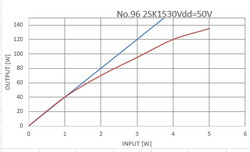

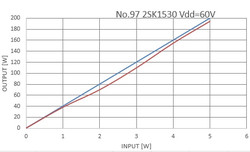

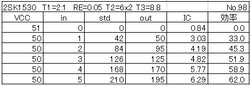

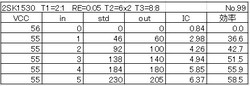

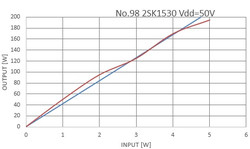

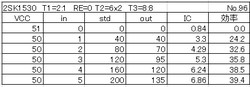

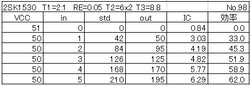

左上がVd=50Vの時の入出力データとそのグラフ、右上がVd=60Vの時の入出力データとグラフです。 Vd=60Vの時、5W入力時、195Wの出力が得られていますが、この測定が終わった直後にFETが熱暴走を起こし壊れました。 ダイオードによる温度検出で、温度補償を行ったつもりでいたが、不十分でした。 今まで、温度補償用のダイオードはFETの樹脂の表面に押し当てていたのですが、どうもうまく温度をピックアップしてくれません。そこで、FETのドレインに一番近い放熱板に押し当てる事にしました。 さらに、安全の為、ソースに0.05Ωの抵抗を挿入する事にしました。 出力が落ちますが、落ちたらVdを上げてカバーします。

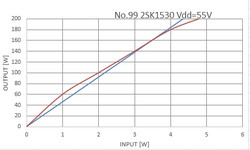

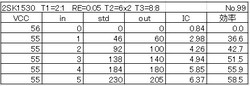

温度補償用ダイオードの位置を変更し、ダイオードの数も4本にし、かつソースに0.05Ωの抵抗を追加した時のVd=50VとVd=55Vのデータです。 Vd=55V時に飽和しかかりの状態で205Wの出力が得られています。 ここで、ソース抵抗を入れた事により効率も向上しています。 リニアリティの実測データは、100W以下で、多少出すぎになっていますが、温度による差と考えられ、測定の時間差により出てきた数値と思われます。 従い、大きな歪はないと思われます。

使用したRFパワー計がクラニシのMAX200Wであり、長くパワーを印加できないので、オイル冷却のダミーと、コメットのSWRパワーメーターに変更し、60Vで熱暴走の有無を確認する事にします。

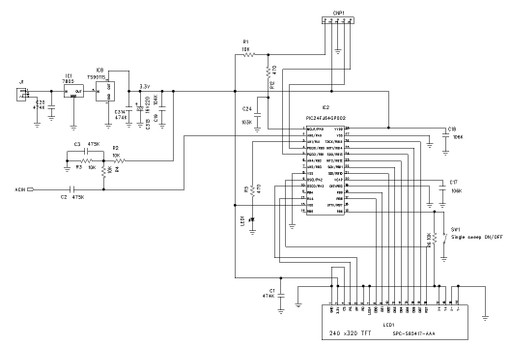

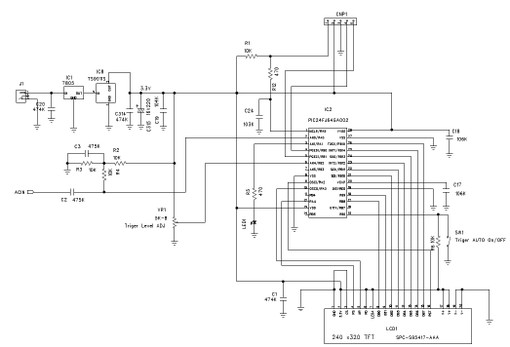

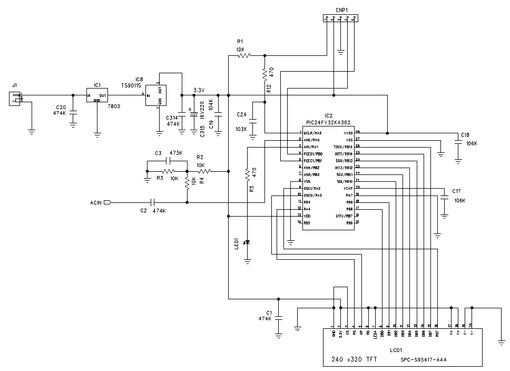

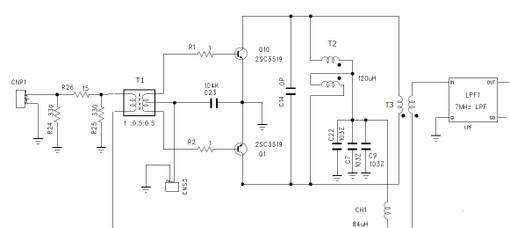

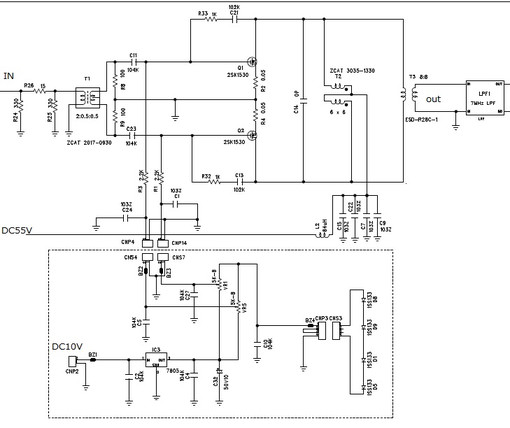

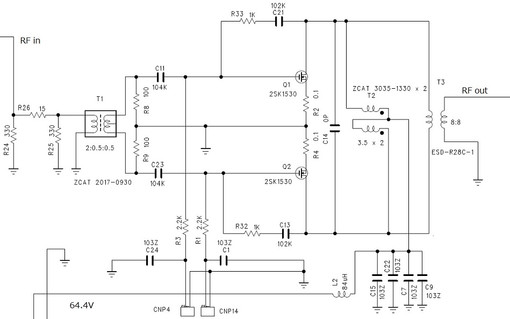

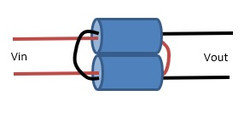

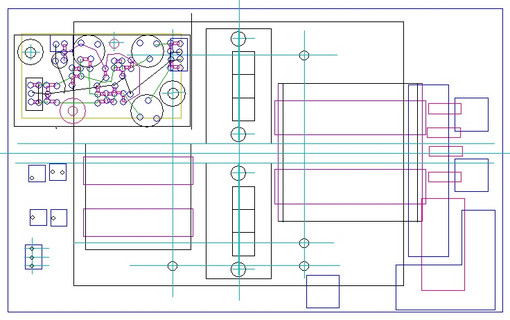

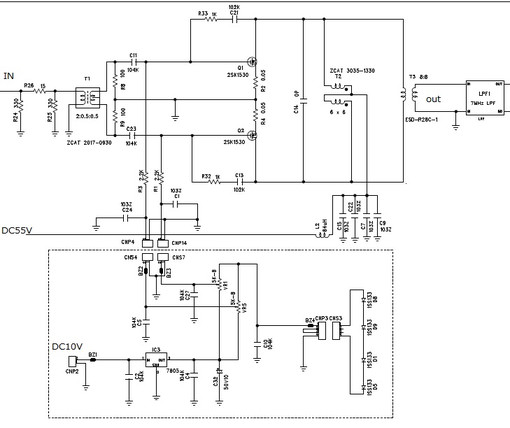

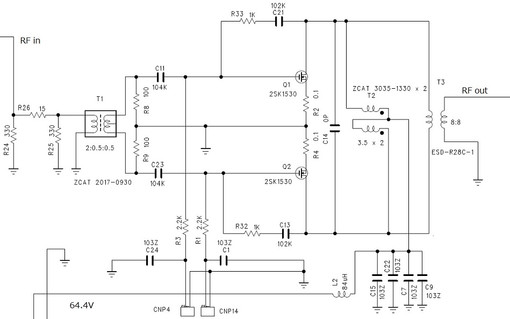

現在の状態での配線図は以下です。 トランスに使用したフェライトコアは配線図の中に書き込みました。 使用したケーブルはエーモンブランド0.75SQの自動車用低圧ケーブルで、ホームセンターの車用部品売り場で見つけたものです。

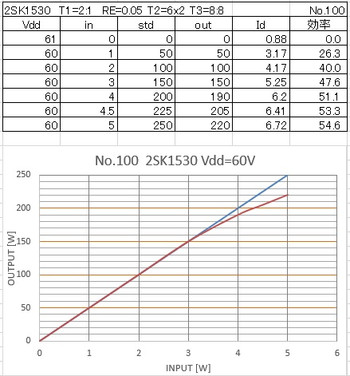

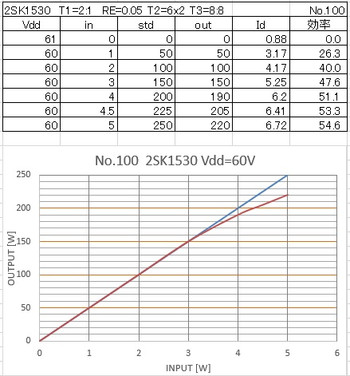

左のデータはVd=60V時の入出力特性です。 200W出力を2分間キープした後で測定したデータとなります。 さすがに、200Wを2分間もキープすると、焦げ臭いにおいも漂いますが、熱暴走は起こらず、Idは次第に減少していく傾向にあります。 グラフデータを見る限り完全なリニアリティが確保された出力は170Wくらいですが、TSSで200Wの認証を受けるには、ちょうどぐらいの出力です。

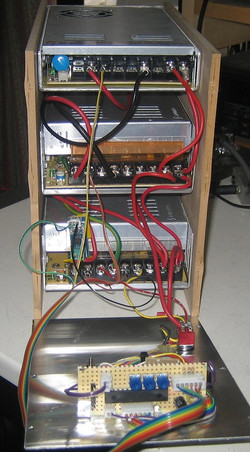

これから、実際のケースに収めて、エージング試験を行い、実用レベルを確かめる事にします。

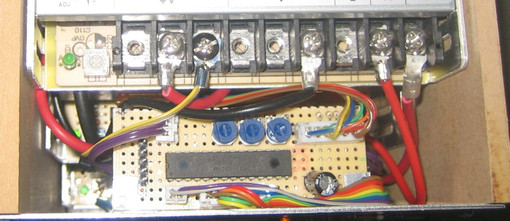

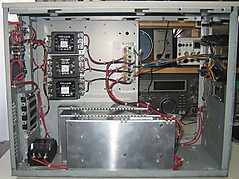

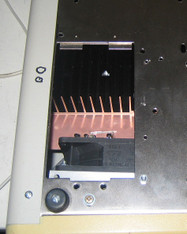

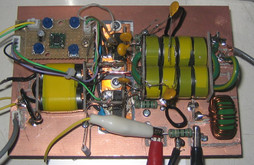

従来の100Wアンプユニットを取り外し、今回の200Wアンプユニットをケースに収納しました。 LPFやアンテナ出力切り替えリレー及び、ファンの移動を行い、ぴったりと収まりました。

このケースインした後の確認事項は、電源からアンプまでの配線が長くなったことによる電圧降下と、ファンによる冷却効果です。 以下の配線図のごとく、配線し、順次確認していく事にします。

配線図 PWR-AMP200W_2sK1530.pdfをダウンロード

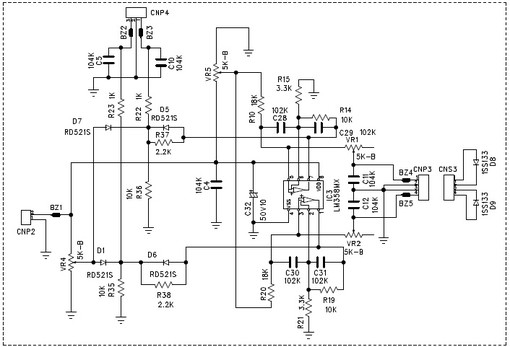

ケースインした状態で、アイドリング電流の安定度の確認を行いました。 DC61Vの電源で、それぞれのアイドリング電流を0.41Aに設定、合計0.82Aとした状態で、無信号状態で、放置テストをしました。すると、次第にアイドリング電流が増え、3分後には0.98Aまで増えます。 この原因は、ファンの風が、温度補償用ダイオードに直接当たり、FETよりダイオードの冷却効果が大きい事のようです。 そこで、ダイオードとファンの間に、衝立を立て、ファンの風がダイオードに直接当たらないようにしました。すると、5分経過してもアイドリング電流は0.88Aどまりで、増加しなくまりました。

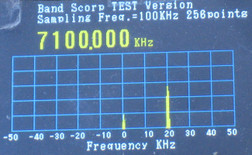

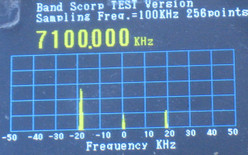

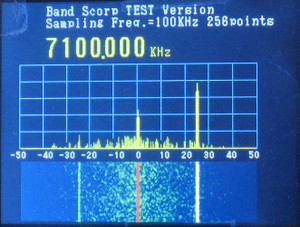

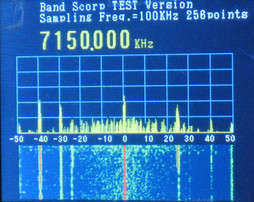

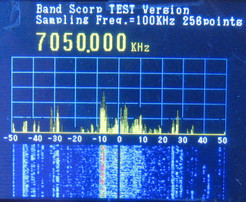

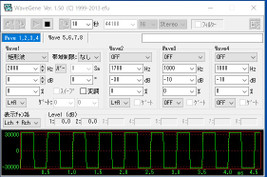

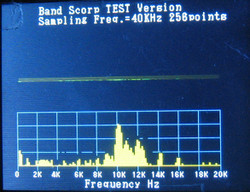

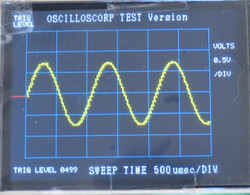

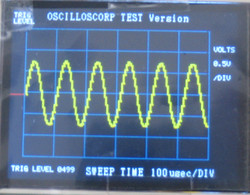

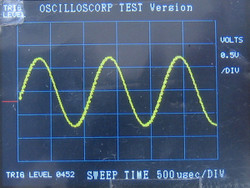

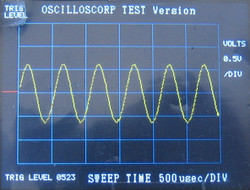

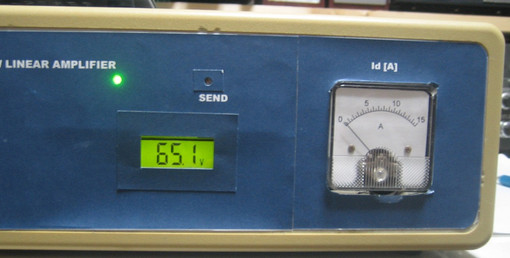

SDRトランシーバーに接続し、2信号特性を見てみました。 電源電圧は無信号送信時64Vです。 この状態で、アイドリング電流を各0.41A 合計0.82Aに合わせ直してあります。

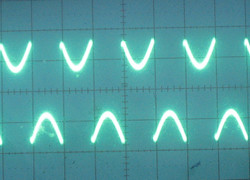

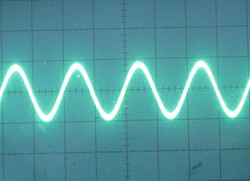

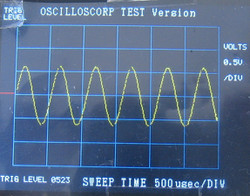

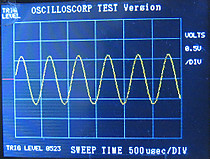

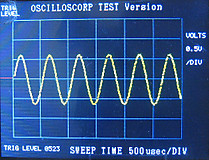

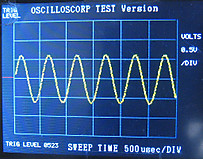

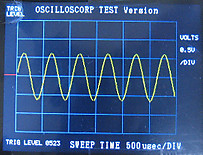

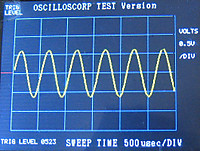

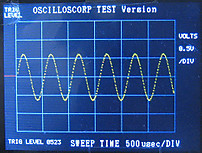

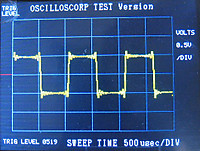

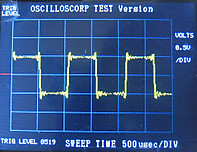

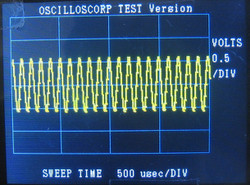

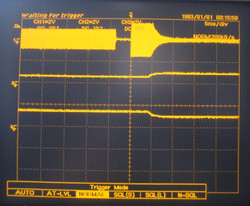

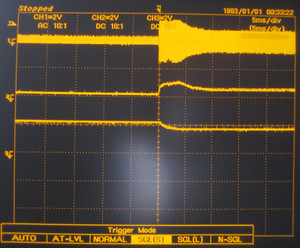

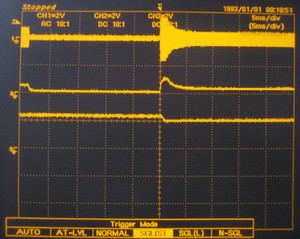

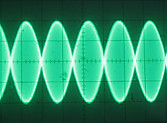

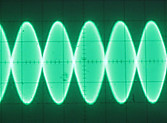

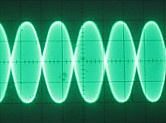

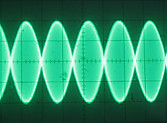

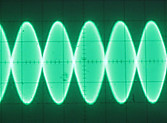

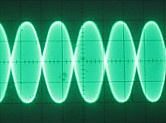

左から順に100Wpep,140Wpep,200Wpep時の2信号特性です。 従来の100W機よりは改善しておりますが、200Wフルパワー時はかなりつぶれます。 マイクアンプリミッターによる出力制限を200Wに置いても、電源電圧や、ファイナルのFETで決まるリニアリティ悪化開始出力が200Wに近かったら、先頭波形がつぶれるのは止むを得ません。

アンプのケースを完全にかぶせた状態ではありませんが、200Wで2分連続、140Wで30分連続のエージングテストを終了し、残すところ、ケースに完全収納し、実際の設置状態でのエージングテストを実施するのみとなりました。 左は、オープン状態でのエージング風景です。 200W連続の時のドレイン電流は下がり気味でしたが、140W時のドレイン電流は開始から終了までの間に20mA増加しました。 エージング終了時に入力をゼロにした時、急速に元のアイドリング電流に戻ろうとしますが、その時間は5分くらいかかりました。

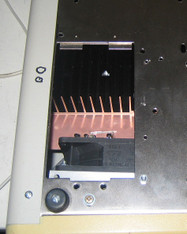

リニアアンプユニットにケースの上蓋をかぶせ、最終チェックです。 200Wで2分間、続けて140Wで30分間エージングした結果、200W時の電流変化はオープン時と同じでしたが、140W30分のエージングの間、電流の変化は5mA以下の減少となりました。 推測ですが、ファンによる風量は変化はないものの、ケースがかぶさった事により、風速が上がり、冷却効果を高めたものと考えられます。 140W出力から信号をゼロにすると、元のアイドリング電流に戻るのに、4分弱でした。 ケースをかぶせた場合、良くなっているようです。 放熱板の下の底板は右上の写真のように、大きな開口になっており、ここからエアーを吸い込みます。

140Wを30分間も連続送信するような実使用は無いでしょうから、以上のテストで、安心して運用出来ます。

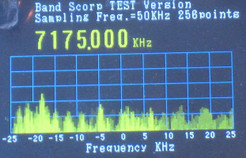

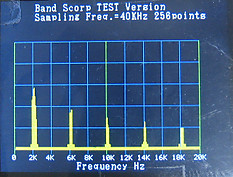

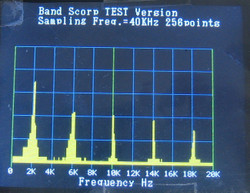

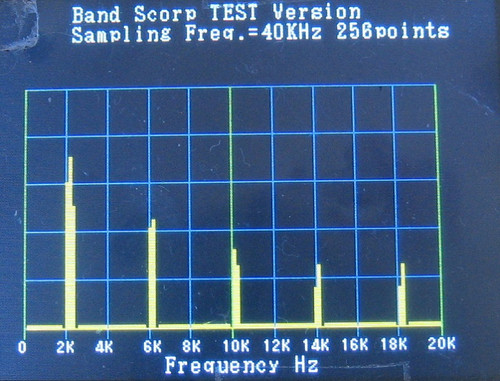

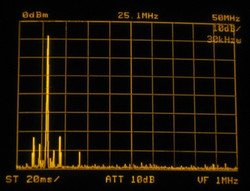

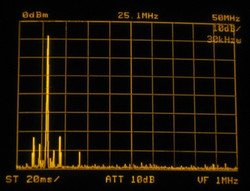

200W出力時のスプリアスは左のようになりました。 7MHz近傍のスプリアスはdsPICトランシーバー由来のもので、リニアアンプ有り無しで変わりませんが、高調波は、第2高調波が-62dBくらい、3次以上はノイズに隠れて見えません。 いずれのスプリアスも新スプリアス規制に合致しています。

このリニアアンプは最大出力が300W以上あり、200Wに制限する為に、マイクアンプにリミッターICを使用し、大きなマイク入力が有っても、200Wを超えないようにして有ります。 また、CWのキャリアレベルも200Wを超えないようにdsPICの中で固定してあります。 AMの場合、AM100%変調時のピーク値が200Wを超えてもOKなので、キャリアレベルで60Wに設定してあります。 最終的な電源電圧は、12V+24V+36VのDC電源の電圧を調整し、アイドル状態で64.1V、200W出力時63.5Vで、200W出力時の入力は4Wになりました。

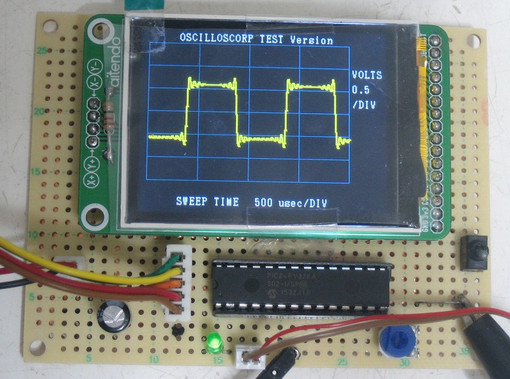

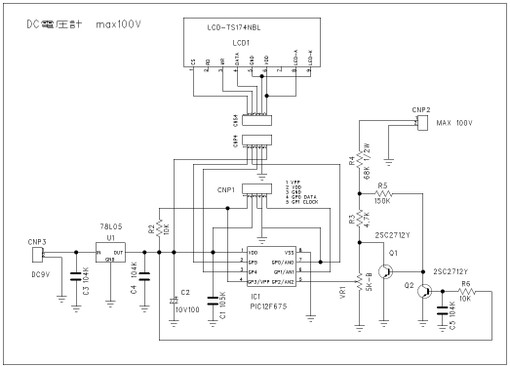

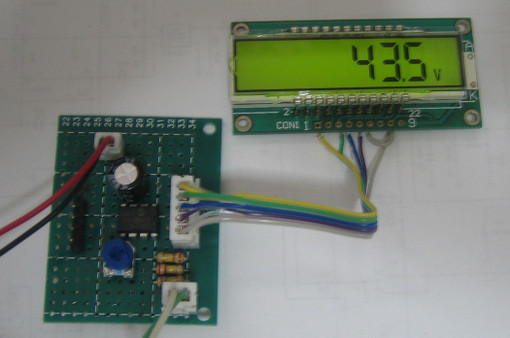

DC電源を3台合成して使う関係で、電源電圧の監視がマストになりますので、上の写真のように、簡単なDC電圧計を追加しました。 この電圧計は+/-0.1Vの精度があります。 写真に写っているQRPトランシーバーの記事はこちらにあります。

2021年3月

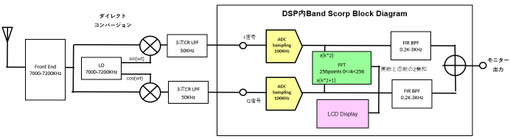

そして、下記ブロックダイアグラムを添付してTSSに認定申請する事にしました。

SDR_200W_TX_BLOCK.pdfをダウンロード

TSSに申請して2日後に、SSBジェネレーターについて、質問がありましたが、最終的に上のブロック図のごとく修正して、1週間でTSSの認可が降り、即日(金曜日)、総通へ申請したところ、次の週の水曜日には審査終了となりました。 今回も指定事項の変更は無いので、即ON AIRできます。 ただし、実際にON AIR出来るのは、次の土曜日です。

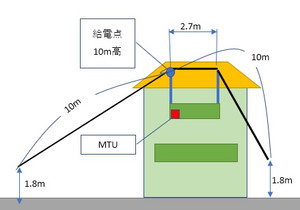

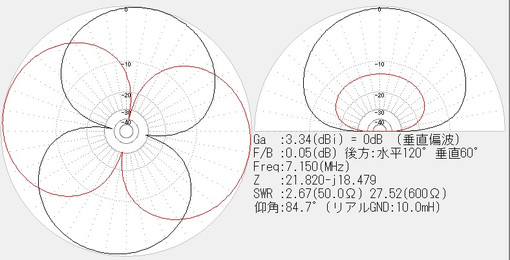

その土曜日の朝からZeppアンテナを張り、200WでCQを出しましたが、QSOには至りませんでした。 コンディションが悪いですねエ。

2021年4月

トラブル発生です。 交信中に突然、電流が15Aとなり、FETがショートモードで死んでしまいました。 とりあえず、TS930SをONして、ファイナルだけは送った後、ケースを開けてチェックしました。 原因は、FETを止めるビス穴がバカ穴になっており、FETが放熱板に密着しなくなったものでした。 放熱板に切ったタップがバカになっており、きつくビス締めしてもFETが指で簡単に回転してしまいます。

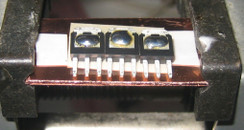

対策は、左上の写真のごとく、アルミ板をコの字型に加工し、これを生きているタップ穴を使い締め付けました。 また、このFET交換に伴い、取り外したNF用のCR回路に使った1/6W 1KΩの抵抗が黒く焦げていました。 この焦げはPPの両方のFETとも同じようになっていましたので、サイズが3倍くらいある、公称1/4Wの抵抗に変更しました。 FET交換後、バイアス電流を64V時、0.4Aづつ合計0.8Aに合わせて、簡単な動作チェックを行い、200W出る事を確認して修理完了です。 今回の事故で2SK1530のストックがなくなりましたので、手配して置かないと危ないですね。

予想は的中し、もう片方のFETもビスバカで壊れてしまいました。 放熱板のアルミ材に粘り強さがなく、タップを切っても、綺麗に切れず、ボロボロになった上、長さの短いビスの為、タップ穴を貫通していなかった事が要因みたいです。 もう片方も写真と同じように追加加工を行いました。 このトラブルが発生したのは、2SK1530が入手できた次の日でした。 ラッキー!

そして、3回目のトラブル。 最初のトラブルの場合、FETの絶縁にはマイカを使用し、シリコングリスたっぷりで固定しましたが、2回目のFET交換時、シリコンラバーで絶縁しました。 そして、このシリコンラバーで絶縁したFETが、またも破壊しました。 修理は、最初のFETと同じく、マイカとシリコングリスで行いましたが、大丈夫だろうか?

後日、インターネットで検索すると、シリコンラバーよりシリコングリスの方が熱伝導は良好であるけど、マイカはラバーより劣るとの事。 使ったマイカはFETサイズの半分くらいのサイズで、単に絶縁するだけの機能とし、残り半分の面積をシリコングリスのみで絶縁した事になりますが、その効果はいかに。 5月連休中、毎日1時間以上の交信を行いましたが、異常なしでした。

2021年7月

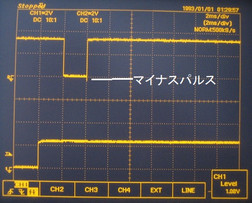

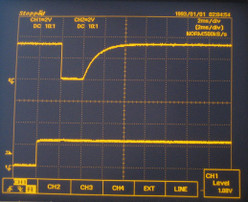

順調に運用を続けてきたリニアアンプでしたが、6月末、交信中にFETがショートモード壊れてヒューズが飛びました。 当然、交信は尻切れで終了。 原因は、熱暴走のようでした。 翌日、FETを交換し、ダミー抵抗を使って、修理確認をしていたところ、電流は流れますが、出力が半分くらいしか出ません。 原因はなんだろうと、入力電力を10Wまで上げたところ、また、FETがショートモードで壊れてしまいました。 仕方なく、手持ち最後の2SK1530に交換したのですが、この交換したFETでも出力は半分しか出ず、最大出力は120W位で、効率も従来の半分くらいでした。

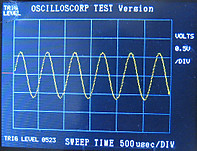

2現象オシロを持ってきて、ゲートやドレインの波形を観測すると、ゲートは正常ですが、ドレインの波形は、正弦波のピークが折り返してつぶれています。 どうも、終段のトランスT2の磁気飽和のようです。 今まで、パワーに対して、あまり大きくないフェライトコアを使用していましたが、プッシュプルのFETのドレイン電流が、フェライトコアの中で、直流による磁界をキャンセルさせていたので、大きな問題になりませんでしたが、FETを交換した事により、DCバランスが崩れ、そのため、フェライトコアが磁気飽和を起こし、FETの熱破壊が早まったのが原因のようです。 このリニアアンプの検討の初期段階で、アイドル電流の調整を1個の半固定抵抗で行った為、ドレイン電流がアンバランスになり、出力がさっぱり出なかった事がありましたが、察するに、この時もフェライトコアの磁気飽和が原因だったと思われます。

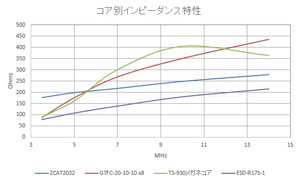

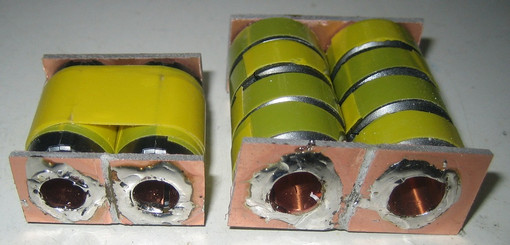

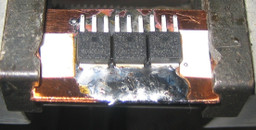

そこで、現在ZCATタイプのコア1個で作られているトランスをコア2個とし、かつ、インダクタンスも可能な限り少なくすることにしました。

従来のトランスのインダクタンスは129uHくらいでしたが、これを110uHくらいまで減少させ、ドレイン電流のアンバランスによる磁気飽和の起こる確率を1/2以下にしました。 また、トランスをバイファイラ巻きで作っても、完全なバランストランスは不可能ですので、FETのバラツキと反対のバラツキになるようにトランスの接続を選択する事にします。

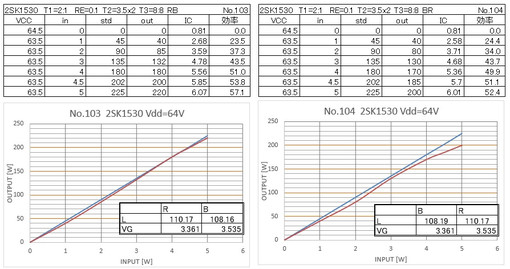

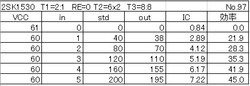

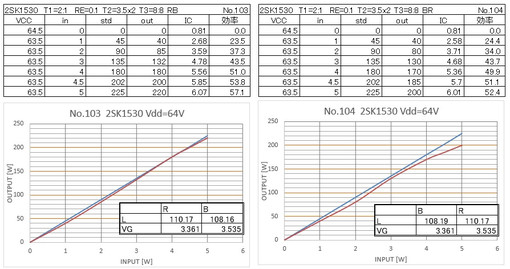

上のデータは、熱暴走防止対策として、ソース抵抗を0.05Ωから0.1Ωに変更し、終段のトランスT2のコアをZCAT-3035-1330 2個使いとし、巻き数は3.5ターンの状態で、巻線の接続を入れ替えたデータの比較です。 表にあるLは巻線のインダクタンスで単位はマイクロヘンリーです。 VGはアイドル電流を0.4Aを流すためのゲート電圧です。 数値的に大きく離れているわけではありませんが、これだけの差でフェライトコア1個の場合、磁気飽和を起こしていました。 左のデータは理想値に対して、200Wまで直線に伸びていますが、右側のデータは150Wを過ぎたあたりから、理想値より出力が伸び悩んでいます。 多分この伸び悩む原因がコアの飽和現象ではないかと思われます。

上のデータは、熱暴走防止対策として、ソース抵抗を0.05Ωから0.1Ωに変更し、終段のトランスT2のコアをZCAT-3035-1330 2個使いとし、巻き数は3.5ターンの状態で、巻線の接続を入れ替えたデータの比較です。 表にあるLは巻線のインダクタンスで単位はマイクロヘンリーです。 VGはアイドル電流を0.4Aを流すためのゲート電圧です。 数値的に大きく離れているわけではありませんが、これだけの差でフェライトコア1個の場合、磁気飽和を起こしていました。 左のデータは理想値に対して、200Wまで直線に伸びていますが、右側のデータは150Wを過ぎたあたりから、理想値より出力が伸び悩んでいます。 多分この伸び悩む原因がコアの飽和現象ではないかと思われます。

今回の修理は、上の左側のデータになる状態で収束させる事にしました。 200Wを出す為の入力は従来の4Wから4.5Wにゲインダウンしましたが、QRPトランシーバーの出力はMAX4Wのままで据え置き、最大180Wくらいで運用する事にします。

今回の修理で2SK1530の手持ちがなくなりましたので、手配して置くことにします。

フェライトコア面に書かれた1530は1330の誤りです。訂正して置きます。

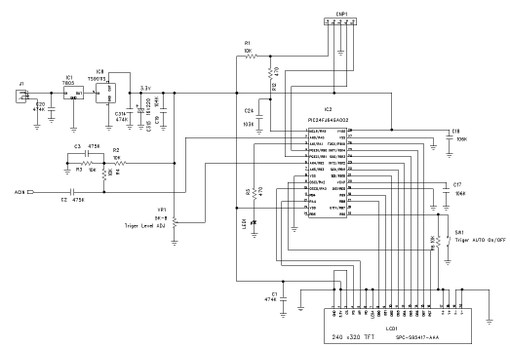

配線図 PWR-AMP200W_2sK1530_2.pdfをダウンロード

このリニアアンプに2MHzのLPFを追加し、2-Band仕様にした記事はこちらにあります。

INDEXに戻る