SDR用 7MHz 100Wリニアアンプ

カテゴリ<SDR>

ダイレクトコンバージョン式SDRトランシーバーが完成しましたが、このトランシーバーに内蔵されているRFパワーアンプは10W出力です。 昨今のコンディションでは、QSOのチャンスもかなり低くなりますので、ストレスが生じない、100W出力まで増幅するリニアアンプを作る事にします。 条件として、電源電圧は48V以下としますが、まだ有りません。 有るのは30V10Aと12V30Aの固定電圧電源だけです。

まずは、予備検討です。

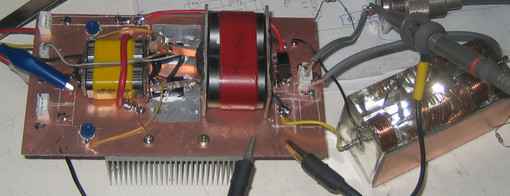

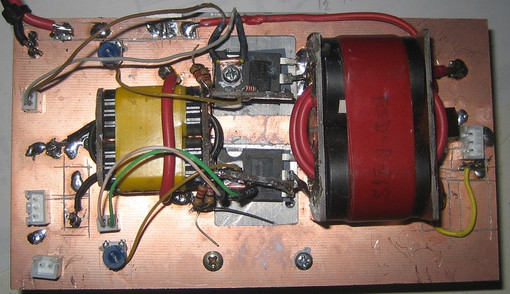

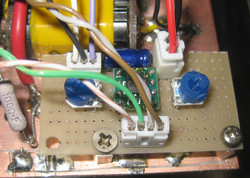

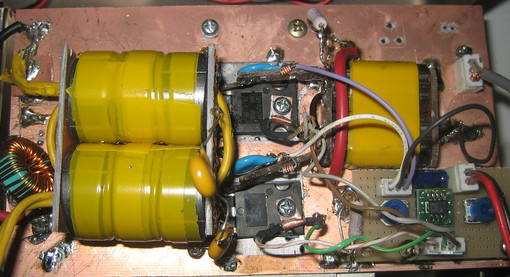

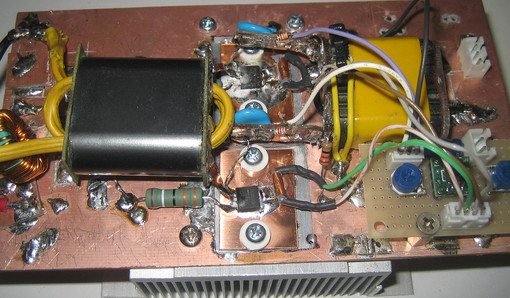

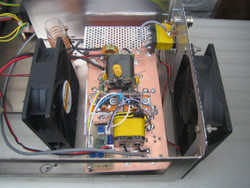

上の写真は以前50WのAM送信機を作った時のPCのCPU用放熱板にマウントしたリニアアンプです。 AM50W出力アンプのピーク出力は200W有り、今回はSSBでピーク出力100Wですから、余裕で行けるだろうと踏んでトライします。 まだ強制空冷ができていませんので、1mW入力で60mW出力が得られる事を確認しただけですが、ちゃんとAB級で動作していることは確認済みです。

使用したファイナルはサンケンのN-MOS FET、FKI10531のプッシュプルで、将来200Wに対応できるように、基板は2パラ-プッシュプルに設計していますが、現在はシングルプッシュプルとなっています。 このサンケンのFETは、秋月にて、1石40円で売っている電源用で、入力容量が1530PFくらいあるにも関わらず、30MHzくらいまでスイッチング可能、Rdsが35mオーム位と、定電圧、高出力を狙うには、都合の良いスペックをもっています。

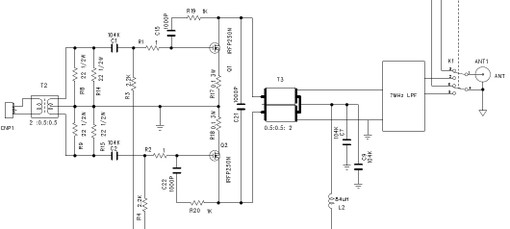

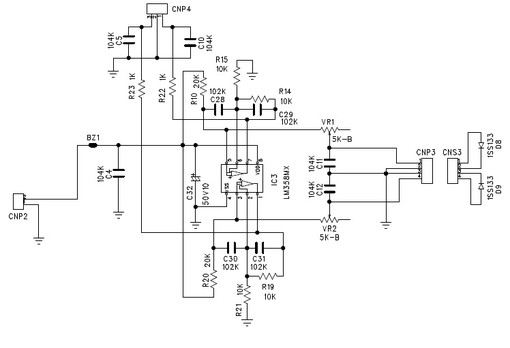

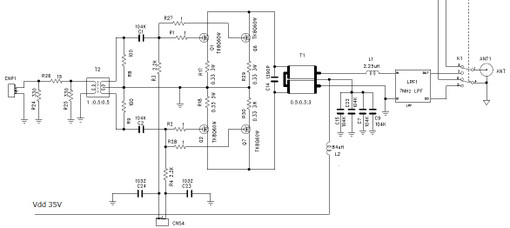

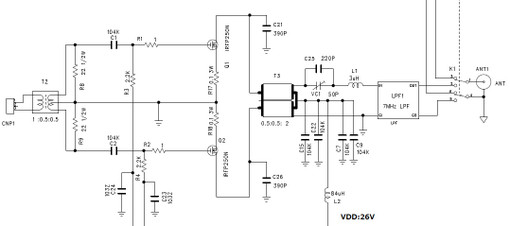

回路図では、電源やバイアス回路、ファンドライブ回路の方が複雑になっていますが、リニアアンプ部は、簡単そのものです。 このRF入力端子から見たSWRは1.5以下です。

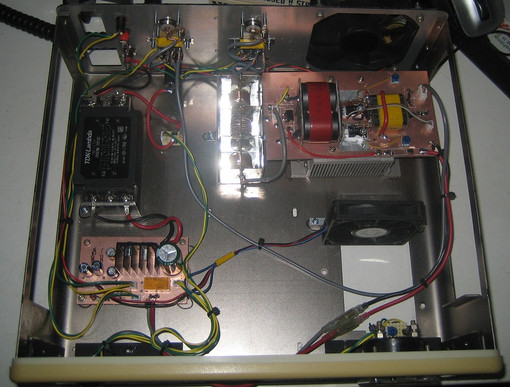

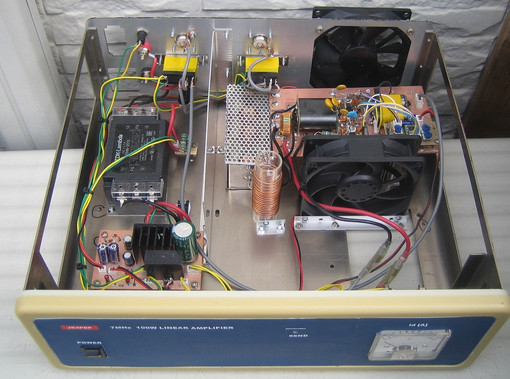

ファンを回しながら、検討する必要から、今回もジャンク測定器を入手し、ちゃんとケースに収めます。 用意したケースは、KEYENCEのマイクロスコープコントローラーです。 さすがに医療機器だけあって、シャーシがステンレスでできており、そのため、ステンレス用ドリルまで購入して工作する必要がありました。

真ん中で白く光っているのは、ブリキで作成した7MHzのLPFです。 すべてのユニットを並べたら隙間だらけです。 この隙間は将来200WまでQROするためにとっておきます。

電源電圧を24Vにして、終段FETのゲートバイアスを調整し、アイドル電流を100mAに合わせようとすると、いきなりドレイン電流が流れ、FETがショートモードで壊れてしまいます。 FETを交換して、慎重にゲート電圧を上げていっても、途中で電流が3A以上になり、また壊れました。 バイアス電圧を2Vに固定し、ドレイン電流が流れない状態で、キャリアのレベルを上げていくと、C級動作になります。 この場合、一応出力が得られますが、歪だらけです。 この状態から、歪がでないように少しづつバイアス電圧を上げていくと、歪は改善されますが、歪がなくなった途端、暴走が始まり、FETが壊れます。

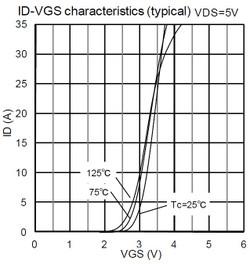

手配したFKI10531はすでに3石壊してしまい、残りは2石のみです。 ここで、改めてこのFETのデータシートを見直してみました。 その中で、左のグラフデータを見つけ、今回のトラブルの原因が判りました。

このグラフデータは、VGSを変化させた時のIdの変化を示しています。

Tc25度の時に、0.1Aにアイドル電流を設定すると、すぐにジャンクション温度は上昇し始め、あっという間に75度を過ぎてしまい、Idは数Aレベルまで増加する事をを示しています。 このFETはC級やE級で使うときは問題ありませんが、AB級ではまったく使用できないFETで有る事が判った次第です。

結局、上辺のデータだけで選んだFETではAB級増幅は不可と判りましたので、FETの選定をやり直す事になりました。

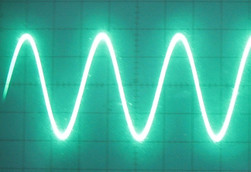

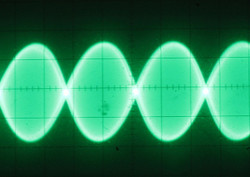

手持ちのMOS FETで2SK3234が有りましたので、これを実装して、終段のトランスの2次側を3ターンとして、テストしてみました。 Rdsが0.65Ωというスペックですが、アイドル電流を初期値で1石当たり、200mAに調整し、RFパワーを加えると、SSBの信号が左の波形のごとく、飽和しかかりの状態で5Wの出力となりました。この時の電源電圧は12.1V、電流は3.3A。 数秒間入力最大にすると、出力が20W を超えますが、リニアリティはあまり良くないようです。 リニアリティを改善する為に、電源電圧を30Vに変えてテストする事にしました。

手持ちのMOS FETで2SK3234が有りましたので、これを実装して、終段のトランスの2次側を3ターンとして、テストしてみました。 Rdsが0.65Ωというスペックですが、アイドル電流を初期値で1石当たり、200mAに調整し、RFパワーを加えると、SSBの信号が左の波形のごとく、飽和しかかりの状態で5Wの出力となりました。この時の電源電圧は12.1V、電流は3.3A。 数秒間入力最大にすると、出力が20W を超えますが、リニアリティはあまり良くないようです。 リニアリティを改善する為に、電源電圧を30Vに変えてテストする事にしました。

30Vの電源でアイドル電流を1石当たり100mAに調整し、SDRを送信状態にした途端、電源が壊れてしまいました。 FETはドレイン ソース間ショート状態で壊れています。

SDRをSENDにした時のショックノイズでFETが壊れたみたいです。

この原因を調べないと先へ進めなくなりましたので、しばらく休止します。 この原因を確かめるには、電源電圧を12Vから徐々に上げていけるDC電源が必要ですが、手元にあるのはMax18V、Max3AのKenwood の電源か、自作のMax20V、Max1Aの電源、6Vから14Vまで可変できる30AのFT991用電源と、30V、12V固定電圧の電源しかありません。 今回は12V電源でうまく動作していたアンプをいきなり30Vに繋いだら、あっけなく壊れてしまったものでしたので、12Vから30Vまで徐々に上げていける電源が必要です。

そんな訳から、リニアアンプは一時休止し、リニア電源を作る事にします。

リニア電源が出来ましたので、終段のFET選定からやり直しです。

すでに3月の最終weekになってしまいましたが、本日、IRFP250Nを6石入手しました。 アマゾンで販売されている、中華リニアアンプに使用されているFETです。 今回はRSから1石261円+送料450円で入手しました。6石注文しましたので、336円/石になりました。

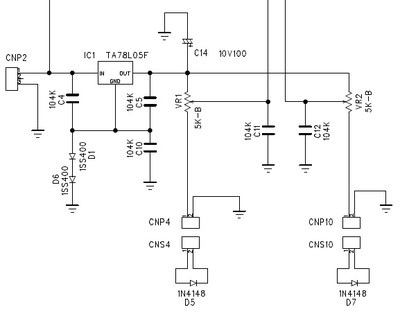

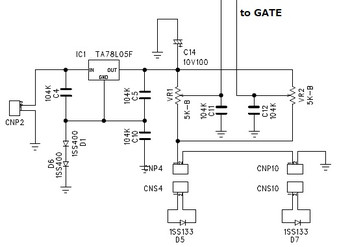

前回の熱暴走の反省から、バイアス回路の熱安定化回路を再検討する為、先にバイアス回路の再設計を行います。

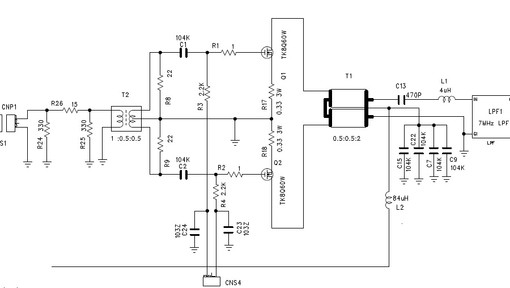

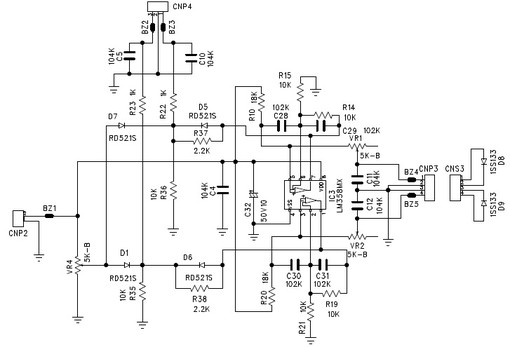

今まで、温度検出ダイオードは1個で、全体の温度補償を行っていましたが、今までにFETが壊れた状況を思い出すと、この検出ダイオードの取り付けられていないFETが壊れる確率が高い事に気づきました。 そこで、今回は、それぞれのFETにダイオードを取り付け、それぞれのバイアス電圧が、独立して温度補償と調整ができるように変更します。 左上が、その回路図です。 また、新しいFETのゲートON電圧が高い方へ、少しずれましたので、5Vの3端子レギュレーターはダイオード2本でかさ上げを行い、6V出力としました。 このかさ上げのダイオードも周囲の温度補償としても動作します。

修正した全体の回路図 PWR-AMP100W_2.pdfをダウンロード

FETの入力容量が2000PFを超えましたので、周波数特性の補正を行う為、入力トランスの出力側に設けた22Ωの抵抗は2本パラにして、11Ωにしてあります。 下の写真は、FETを乗せ換えて、バイアス回路の変更が完了したパワーアンプ基板です。

ファンやDCバイアス電源用の3端子レギュレーターは、電源電圧がMax48Vになった事より、耐圧オーバーで使えませんので、12Vの電源をディスクリート回路で作り、バイアス用6Vの電源は、この12V電源から供給するように変更しました。

電源電圧を20Vにしておき、アイドリング電流を片チャンネル当たり200mA(トータル400mA)として、入力にアンテナアナライザを接続すると、SWRは1.3くらいです。 出力は18mW出ています。 この時の入力は0.8mWでした。 前回はこのテストまでは良かったのですが、次に実際のSDRトランシーバーを接続したら、FETが壊れてしまいましたので、この調整状態から一度、電源電圧を10V以下まで下げて、入力レベルを上げてみる事にします。

10V電源で1Wの出力がでました。そこから、次第に電源電圧を上げていき、15Vまで上げたとき、2.5Wとなり、さらに18Vにした時、電源がパチと音がして、電圧が50V以上に。 すぐに、またパチと音がして、出力なしに。 RFが電源に回り込み、電源のFETが壊れ、その為、アンプの2石のFETも壊れてしまいました。 リニア電源をやり直しです。

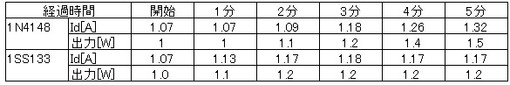

リニア電源用のトランジスターは全て使い果たし、手配待ちの状態ですので、その間に、従来の電源で実験です。電圧を18Vに固定して、出力が1W になるように入力レベルも固定して、電流と出力の変化を見てみました。

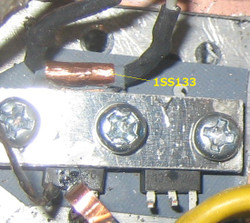

温度補償用ダイオードが従来の1N4148の場合、アイドル電流は2石合計で、100mAです。このデータを見る限り、明らかに熱暴走し始めています。 そこで、温度対Vfの変化が2倍くらいある1SS133に変えてみました。 1SS133のアイドル電流はより暴走が起こりやすい、2石合計で200mAです。 結果は、3分経過した時点で電流も出力も増加が止まりました。

電源電圧18Vのままで、2石のプッシュプル回路のドレイン間に1000PFを追加したり、出力トランスの後に、LC共振回路を挿入したりして、18W連続出力が得られる状態になりました。 この状態での入力は0.8Wで、以前アンテナアナライザーでテストした時と同じゲインが得られています。

電源の電流制限が3Aでかかる為、この電源での最大出力は25Wでした。 そこで、30V 10Aの容量のある電源に、接続し、アイドル電流を2石合計で200mAにしておき、出力を上げていくと、30W出力になったとき、熱暴走が起こり、ファイナルのFETがまたしてもショートしてしまいました。 バイアス回路はまだ不十分でした。

しばらく、放熱板ではなく、頭を冷やす事にします。

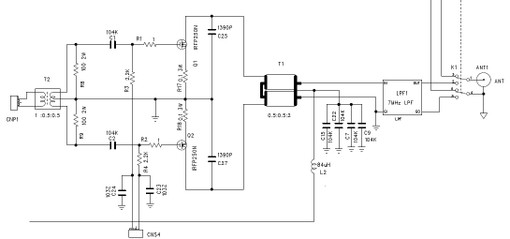

WEB検索をしていると、電源用のFETを使ってリニアアンプを制作しているJE3PRM OMのノウハウ紹介の記事が見つかりました。OMの製作アンプと、私のアンプの構成は異なりますが、かなりのノウハウを生かす事ができそうです。 そこで、電源電圧を20V(12V20Aの電源と8V30Aの電源を直列に使った)の電源を使い、下の回路図で、5W入力時、40Wの出力を得る事ができました。(Very TKS OM)

この回路は、バラックに近い状態で仮組したものでした。 20Vの電源で、5.2Aの電流が流れ、40Wでしたので、約38%の効率です。100Wの目標には、まだ遠いですが、足がかりが出来た感じです。 この回路を実験する途中で、またFETが破損し、今度は楽天にて1石135円で売りが出ていたIRFP250Nを10石購入し、1石だけ交換したのですが、バイアス電圧の差が2V近くあり、PP回路がうまく動作しません。 どうやらロットのバラツキみたいです。 電源用のFETでアナログ動作をさせる場合、この問題はついて回るようです。 誰かの製作例を見ながら、そっくり同じものを作っても、性能が出ないのは、このロットのバラツキによる影響が一番かもしれません。 今回、2石とも楽天から購入したFETに交換したら、アンバランスの問題は解決しました。

今後、さらに電源電圧を上げられるようにバイアス回路を検討する事にします。

左が変更したバイアス回路です。

変更内容は、温度検出用のダイオードを2個直列に接続し、温度変化による、電圧変化が2倍になるようにしました。

そして、このバイアス供給回路を実装した上で、電源電圧を26Vまで上げて、36Wの出力が得られたのが、下の回路です。

この回路では、入力4Wのとき、4.2A流れ、36Wが連続で得られていました。 ただし、この出力が、限界で、いくら入力を増やしても、出力は増えませんでした。

この回路で、アイドリング電流は、両方合わせて、80mAくらい。 入力側のSWRは1.3以下。

この回路で、アイドリング電流は、両方合わせて、80mAくらい。 入力側のSWRは1.3以下。

電源電圧は22Vで出力は35Wくらいで、以降、電圧を上げても入力を上げてもほぼ飽和状態でした。

出力が飽和する原因を確かめようと通電を続けていると、3分も経過しないうちに、5Aのヒューズが切れてしまいました。 そして、AMPの片方のFETが全端子ショート状態で破壊していました。 この原因は、またしてもFETの熱暴走です。アイドリング状態では、問題ないのですが、パワーを大きくすると、例え、ソースに0.1Ωの抵抗を挿入していても、熱暴走を起こしてしまいます。 バイアス回路の再検討が必要です。

現在の1SS133を直列に接続した、バイアス回路で、1SS133がそれぞれ0.1V、2個直列で0.2V変化した時の、FETゲート電圧の変化を計算してみました。 結果は、なんと0.08Vくらいしか変化しない事が判りました。 ここは、少なくとも、1SS133が0.1V変化したら、FETゲート電圧も0.1V変化してほしいので、バイアス回路を以下のOP-AMPを使った回路に変更する事にしました。

この回路のOP-AMPのゲインは6dBあり、1SS133が0.1V変化すると、出力は0.2V変化します。 多少効き過ぎかもしれませんが、この回路を実装してみました。

左が実装したときの写真です。 パワーアンプと同じ基板の上に配置されますので、高周波の回り込み対策はこれでもかというレベルで実施しました。 18Vの電源で実際に動作させた場合、問題は有りませんでした。

最初、この新バイアス回路に変更し、ソースにあった0.1Ωの抵抗はショート状態で、電源電圧26Vでトライしました。 アイドル電流は各FET50mA、合計100mAに調整しました。 残念ながら、出力トランスの2次側を2ターンの時、12Wしか出ません。 3ターンにしたら、5W出しか出ず、熱暴走が起こり、FETが壊れました。 熱暴走する前に2次側を1ターンしてみましたが、5Wしか出ませんでした。

そこで、ソース抵抗の0.1Ωは元に戻し、AMP部分の回路を上の回路図に変更したうえで、出力が飽和する原因を探す事にしました。 オシロで各FETのゲートやドレインの電圧波形を確認すると、PP回路のゲートやドレインの波形がかなり異なります。 どうも、同じアイドル電流では、B級動作の最適状態にならず、出力波形を見ながら、アイドル電流を決め、かつ、ドレインとGND間に挿入するコンデンサの値をアンバランスにすると、まともなプッシュプル動作に近づける事が判りました。この最良状態で、電源電圧18Vにしておき、出力が飽和する直前まで、入力を上げると、0.3W入力で16Wの出力となりました。

ドレインの電圧波形は、ピークは24Vくらいですが、min.は4Vです。この4Vはソースの0.1Ωの両端の電圧と一致します。 すなわち、プッシュプルの片方の振幅は20Vしかなく、これを出力トランスで2倍しますので、出力のピークは40Vです。これを実効値に直し、50Ωの負荷で計算すると、16Wの出力になります。 要するに、この回路では、電源電圧で、出力が決まり、少なくとも、コンベンショナルトランスの巻き数は最良状態であることが判りました。

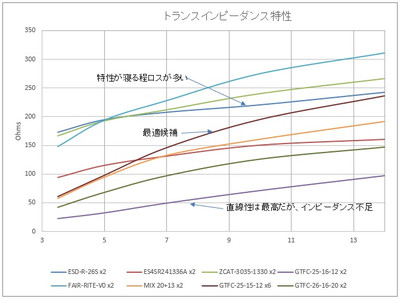

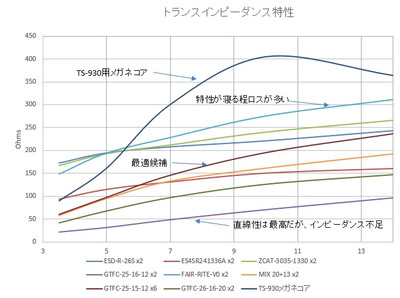

そのコンベンショナルトランスのコアについて、特性を取ってみました。

左のグラフでロスが多いとコメントしているコアが今まで使用していました、NECトーキンのコアで、赤色のテープで巻いていました。

最適候補とコメントしているコアは、北川工業のGTFC-25-15-12を6個使ったもので、全体のインピーダンスが少し低めですが、このコアに変更する事にします。

このコアは黄色のテープで巻いてあります。

出力を上げるには、電源電圧を上げて、かつ、その電圧でも熱暴走が起こらない回路を作るしかありません。

入力のSWRが3くらいあるので、トランスの1次巻線を2ターンとして、かつ、トランスの出力抵抗を22Ωにした状態で、SWRが2くらいになりましたので、電源電圧を少しづつ上げてみました。

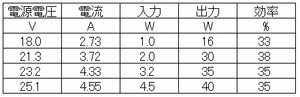

左の表は、その時のデータです。電源電圧は最大で26Vまで上げられますが、電源から送信機入り口までの電線による電圧降下で、最大25.1Vしか上げる事が出来ません。 それでも、40Wの出力が得られました。そして、この40W出力中でも、電流は次第に減少し、1分で10mA近くのペースで少なくなります。 熱暴走が起こっていない証拠です。ただし、3分もすると、出力は38Wくらいまで落ちます。

2020年ゴールデンウィークに突入しました、今年は新型コロナウィルスでどこえも行けません。

ここから、フの字タイプの保護回路付きの安定化電源を使えるようになりました。

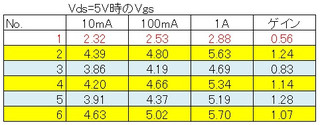

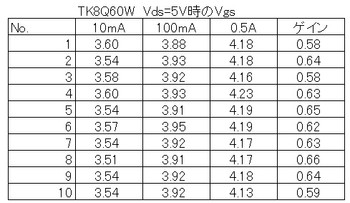

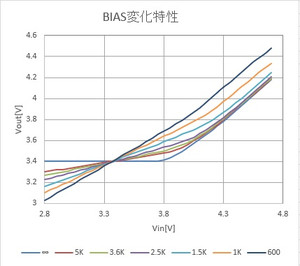

少し気になる問題があります。 上の表を作成するとき、回路が最大出力を出す為には、片方のFETのドレイン-GND間に1390PFのコンデンサを接続し、もう一方のFETのドレイン-GND間にはコンデンサは有りませんでした。 そこで、この二つのFETのゲート電圧対ドレイン電流のデータを取ってみました。No.1のFETにはコンデンサは接続されず、No.2のFETのみ1390PFが接続されています。 見ての通り、ふたつのFETの特性は大幅に異なります。 また、ゲインと表示してある数値はドレイン電流が10mAから1Aまで変化する場合のゲート電圧の差を見たものですが、No.1と2では2倍以上の差があります。

これらのFETは一括して楽天から購入したものでしたが、スィッチング用FETとしては、全く管理されていない項目ですので、この種のFETをリニアアンプに使う場合、このデータを確認して、そろったもの同士を使わないと、期待する出力は出ないという事のようです。 買ったのは全部で10石でしたが、すでに3石壊してしまいました。 残りは7石ですが、1石は不良品で、ゲート電圧を7Vまで上げても、ドレイン電流は流れませんでした。

リニア電源が出来ましたので、アンプの検討を再開しますが、まず、No.1のFETを取り外し、No.2のFETに一番近い、No.4のFETに交換する事にします。

電源電圧18Vにて、最大出力が出るように、回路定数をいじった結果、入力1Wで18W出ました。 以後、すこしづつ電源電圧を上げ、32Vでアイドル電流各0.1Aとして、入力3Wを加えた結果、32Wしか出ません。流れている電流は3.91A。 1分くらい通電すると、電源の保護回路が働き、電圧がダウン。 調べてみると、No.4のFETがドレイン、ソース間ショート状態で壊れていました。 電流は、減少方向にドリフトしている最中で、死んでしまったものです。 原因が判らないまま、No.5のFETに交換しました。

フの字特性の電源は高周波の回り込みもなく大丈夫でした。

前回、25Vの電源で40W出ていました。 今回、電源電圧を33Vまで上げましたが、30W以上出ません。 やる度に、最大パワーが下がっています。 ソースに挿入されている0.1Ωの性かもと、この抵抗をショートしてみましたが、ゲインは少し上がりましたが、最大パワーは変わりません。 考えられる原因は後ひとつ、コアです。 コアを変更してみる事にします。

そこで、TS-930Sに使用されていたメガネコアのインピーダンス特性を、先に測定した各コアのデータに重ねてみました。 左のグラフに示しますが、今まで検討してきたコアとは、全く異なるデータを示します。

このTS-930S用のコアは昨年作った、6m用AM送信機のパワーアンプに使っていたものですが、6mリグには戻さずに、この7MHz用リニアアンプで使ってみる事にします。

左のデータは、コンベンショナルトランスのコアをTS930S用に変更し、トランスとLPFの間に、整合用のLC回路を挿入し、ソースの0.1Ωも廃止して、最大出力が得られるようにした状態で、各電源電圧ごとに、アイドル電流が各100mAになるように再調整した時の出力と効率です。 少なくとも、コアによるロスは最小となっているはずであり、かつこのコアは7MHzで180Wくらいを出力する実力があります。 従い、電源電圧を上げても、出力が上がらない原因は、FETしか考えられません。

このFETは18V前後の電源で使ったとき、最大効率が出せるけど、それ以上の電圧では、どんどん効率が落ちるのではないかと推測します。

このリニアアンプを検討を始めて、すでに4か月以上経過しましたが、この場に及んで、FETの選択からやり直す事にします。

JE3PRM OMが紹介している、FETは、スーパージャンクションと言われるMOS FETで、従来のFETより、高耐圧で、ON抵抗が低く、Cissもかなり小さい、最新のFETのようです。 国産のFETで、同様なFETを探すと、東芝がDTMOS構造のFETとして、かなり前から製品化し、一部は秋月でも取り扱っています。 そこで、TK8Q60Wという品番のFET(1石 60円)を10石入手し、これでリニアアンプを作ってみる事にしました。

IRFP250Nの事も有りましたので、購入した10石のVgs対Idのデータを取ってみる事にしました。

左が、その10石のデータです。 さすがに東芝製ですね。バラツキのレベルがIRとは全く違います。 これだと、どの組み合わせでも、PP増幅のペアを作る事ができます。 ただし、Pd=80Wにしては、かなり小さなパッケージで、このデータを取る為に、0.5AのIdを流すと、あっと言う間に、触れないくらい熱くなります。 放熱板にしっかりと密着させる方法を考えなければなりません。

最初は、シングルのプッシュプルとして、50W出力を狙い、うまくいったら、2パラプッシュプルで、100Wを狙います。 ただし、目標とした電源電圧が48V確保できない事が判りましたので、40V以下の電源で100W出力に目標を変更します。

左の写真は、IRFP250Nを取り去り、基板と放熱板に加工を施し、このFETを取り付けた状態です。 FETは4個取り付けましたが、配線は2個だけ行い、もし、壊れたら、予備のFETに配線し直し、FETの交換の煩わしさを軽減します。

ただ、FETの足が短く、配線には難儀しそうです。

なんとか、配線完了です。

電源電圧を落として、恐る恐る動作テストを行う事にします。

18Vの電源電圧で、テストしました。 アイドリング電流は、各100mAです。 入力3Wで13.5Wしか出ません。 1分くらい通電した後、入力をゼロにしたら、電源電圧が0.5Vくらい上昇し、電流はアイドル電流に戻る事無く、熱暴走を開始してしまいました。 バイアスの温度補償機能の応答速度が遅くて、熱暴走を阻止する事が不可能になっているようです。 結局、熱暴走を止められず、安定化電源が保護動作したのは、アンプのFETがバリバリと言った後でした。 温度センサーの位置や構造を一から見直す必要がありそうです。

対策として、1SS133をシリコンラバーごと銅板で丸め込み、これを、FETのドレインとシリコンラバーの間に挟み、止めた状態で、再テストしてみました。

電源電圧が16.4V、2W入力で、12W出て、入力をゼロにすると、ドレイン電流は、2秒くらいで、アイドル電流の状態に戻ります。

次に、電源電圧を22Vにして、3Wの出力まで、入力を加えたところ、熱暴走が始まり、またしても、FETはショートモードで破壊しました。 FETがショートモードで破壊しても、安定化電源のプロテクタが働き、電源は無傷です。

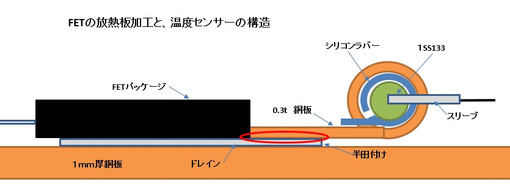

スーパージャンクションタイプのFETは、構造的に、ジャンクション部分から、ドレインの外側金属面までの熱抵抗が小さく、小さなドレイン面積でも、無限大サイズの放熱板を付けたら、仕様書に出てくる80WのPdを確保できますが、有限サイズの放熱板と、いくら、マイカより、熱抵抗が小さいという、シリコンラバーを介した放熱では、無理があるようです。 ここは、OMが採用しているように銅板をドレインに半田付けして、ドレインの面積を増やさないとダメなのかも知れません。

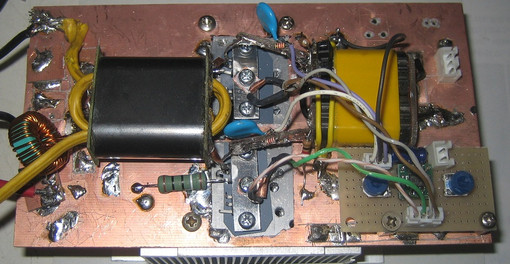

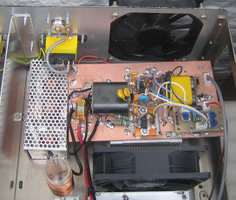

近くのホームセンターに1mm厚の銅板を買いに行き、現在の放熱板に取り付けられる、放熱フィンを作る事にしました。 結果は、大成功です。 52Wの出力を安定して得る事ができ、電源電圧40Vで70Wの最大出力を確認できました。

実施内容は全て、JE3PRM OMの記事の通りですが、具体的な工程を紹介します。

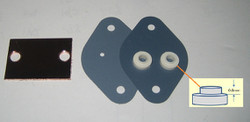

まず、1mm厚の銅板を左の様に20mm x 28mm角に切り取り、放熱板に取り付ける為の、丸穴を開けます。 大きめのシリコンラバーを用意しますが、銅板の下に敷くサイズを確保できないときは、複数枚用意します。 さらに、ビスとドレインを絶縁する、絶縁ワッシャを用意します。 この時、ワッシャの内側の高さが0.8mm以下の物でなければなりません。 銅板に開けるふたつの穴はこのワッシャが入る大きさが必要です。 私のワッシャは4.5φの穴でOKでした。

銅板をバイスでつかみ、60W以上の半田こてで、半田を少し盛ります。 また、FETのドレインの金属面にも半田メッキを行っておき、銅板上にFETを置き、銅板の半田を暖めると、その内、FETが簡単に銅板の上を滑りだします。 この状態で、FETが適当な位置で動か無いようにピンセットで押さえた後、半田こてを離し、半田が固まるまで待ちます。 このくらいの熱処理くらいでは、FETは壊れませんので、失敗したら、何度でもやり直します。

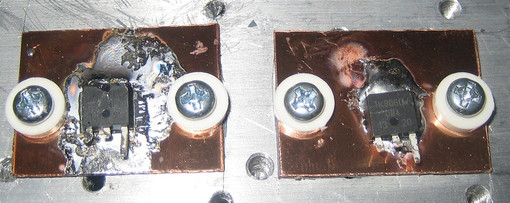

上は、そのようにして加工した放熱フィン付きのFETです。 右側は一発で半田付けが成功しましたが、左側は何度も失敗し、銅板面が半田メッキだらけになってしまいました。 ここで、注意したいことは、決して銅板の裏側に半田がつかないことです。 もし、誤って半田がついてしまったら、その銅板は廃棄するのが賢明です。

放熱板に止めるときは、間にシリコンラバーを挟み込みますが、もし、分割されたラバーの場合、互いに重ならないようにします。 上の写真では、放熱フィンを固定した後、銅板の端に沿って、ラバーをカッターで切り取りました。

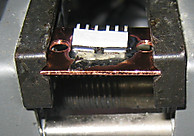

次に、このFETに温度補償用のダイオードを半田付けします。

まず、1SS133の両方の足に長さ10mmくらいの耐熱スリーブをかぶせます。 耐熱スリーブが無いときは、耐熱リード線(半田こてで電線に半田メッキをしても、被服が縮まないリード線)の導体を抜き取り、残った被服をかぶせておきます。 0.3mm厚の銅板で図のように丸め込みますが、ダイオードと銅板の間にシリコンラバーを詰め込み、ラジペンで、丸く成型しながら、締め付けていきます。 ダイオードが自由に回転しなくなるまで締め付けます。 あまり強く締めるとダイオードが割れてしまいますので、要注意です。 最初シリコングリスを塗った状態で、銅板を丸め込みました。 しかし、ダイオードが破損する事が多く、緩衝材と熱伝導を兼ねて、シリコンラバーを挟み込むようにしたものです。 1SS133を入手出来ない場合、1SS178でも代用できます。 ダイオードのリード線に延長用の耐熱リード線をハンダ付けし、その部分に2φの熱収縮チューブをかぶせ、しっかり固定します。

この出来上がった銅板によるダイオードホルダーをFETのドレインの金属部分に半田付けします。

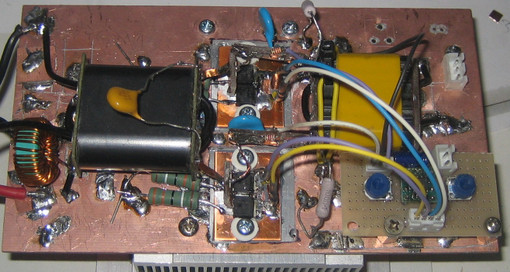

このようにして、加工したAMPの全体が上の写真です。 実装にあたっては、ドレインが放熱板にショートしていないか十分に確認します。 この実装状態でも、銅板のはしっことプリント基板のエッジがタッチしており、この修正の為に、基板をやすりで削る羽目になりました。

写真では、入力トランスの出力端に22Ωの負荷抵抗が見えますが、これは100Ωに変えてあります。 また、写真には有りませんが、ドレイン間に390PFのコンデンサを追加してあります。

さらに、コンベンショナルトランスの出力からLPFの間にあった470PFのコンデンサは廃止し、コイルは2.25uHに変更しました。 オリジナルは、LC直列回路でしたが、それじれの容量とインダクタンスをLCメーターで測定し、7100KHzのインピーダンスを計算すると、合計でプラスのリアクタンスとなりましたので、コイル単独で、同じリアクタンスが得られるようにしたものです。

左の表が、恐る恐る入力レベルと電源電圧を上げたときの、出力データです。

電源電圧40V、入力5Wのとき、めでたく70Wの出力が得られました。

そして、この70W出力状態から入力をゼロにすると、いっきにアイドル電流の状態に、Idが減少します。

今までの回路では、このテストをすると、アイドル電流状態に戻るまで10秒i以上かかったり、最悪熱暴走していました。

また、効率も、まずまずの数値を示しています。 ソースに接続した抵抗が0.33Ωなので、もう少し悪くなるのではと、危惧しましたが、それほど悪さはしていないようです。 ただし、70Wを連続1分以上出力すると、Idが少しづつ上昇します。 その程度は5秒で10mA程度ですが、30mA上昇したところで、入力をゼロにしたところ、Idは初期のアイドル状態に数秒で戻りました。 多分、70Wくらいが、最大電力になりそうです。 さらに、このFETのSOAを確認すると、40Vの電圧のとき、2Aが最大となっていますので、2石に均等に電流が流れたとしても、このくらいが限界でしょう。

FETのPd maxは2石で160Wですが、それは無限大放熱板の時だけです。 現在は95mmの2個のファンで強制空冷していますが、実際問題として、許容できる最大Pdは1/2の80Wくらいと、推測します。効率が50%なら、80Wくらいの出力が限界となりそうです。 このAMPはSSB用ですので、1分間くらい100Wの出力が出来、70Wくらいを連続30分以上出力出来たらよいと考えますので、 今後この限界を詰めようと思います。

アンプとは、別問題ですが、電源電圧を40Vにした事により、12Vのシリーズレギュレーターの放熱板の温度がずっと触れないくらい熱くなります。これは、ちゃんと対策しないと、バイアスが狂って、アンプを破壊する原因になりそうです。

そこで、基板上の小さな放熱板からトランジスタを外し、ステンレスのシャーシに直付けしました。 これで、様子を見る事にします。

この、プロジェクトの目標は100Wのリニアアンプですが、今までのスーパージャンクションFETを使った回路では、FETのPdが160Wしかなく、常温で、80Wまで許容できるとし、かつ、アンプの効率が50%とすると、最大で、80Wしか出せません。 そこで、このFETを2パラ、プッシュプルとし、最大Pdを320Wにして、100Wの出力を得る事にします。

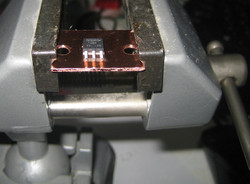

上の段の左は、銅板に2石並べて半田付けしているところです。 2石の並びがずれないように、FETのTOPに両面テープを張り付けています。 両面テープの素材は紙ですので、半田こての熱で溶ける事は有りません。 右側は、2石のFETのゲートに1Ωの抵抗を挿入するために張り付けたプリント基板の短冊です。 この短冊の中に1Ωのチップ抵抗が付けられております。 この基板は両面基板となっており、裏側の銅箔で、2石のドレインを連結しています。

下段の左は、新たに作った、1SS133の温度センサーをドレインのフィンに半田付けしたところです。 銅板は、20mm x 28mmの先に使用した1石用を使用しましたが、FETを2石並べて半田付けするには、寸法的に、少し窮屈ですので、次回作るときは、20mm x 30mmくらいの銅板が良いのですが、放熱板側のタップ穴ピッチと合いませんので、写真のごとく、まとめました。 右上は、この放熱フィンを放熱板に取り付け、ドレイン以外の配線を完了した状態です。

出来上がった配線図とアンプユニットです。

2パラPPにしたので、コンベンショナルトランスの2次側巻線は3ターンにしてあります。 3ターンにしたので、今まで使っていました、2芯シールド線(黄色のワイヤー)がトランスの銅パイプの中を通らなくなりました。 そこで、少しロスが増えますが、50SQのKIV線に変更しました。多分、40V以下でも100Wが得られるだろうと、期待しています。

左が、電源電圧を上げながら測定した、出力や電流のデータです。

アイドリング電流は、各電源電圧の時に、プッシュプルの各片方ごとに100mAに合わせてあります。 パラ付けですので、個々のFETに50mAづつ流れる補償はありませんが、先に確認した、バラツキデータから、一方が100mAで、片方が0mAという事はなかろう、とみています。 C14は当初390PFのままで、測定しました。電源電圧34Vで、10W出力にして置き、最適値を探した結果1390PFと出ましたので、このコンデンサを1390PFに変更し、34.2Vの電源電圧の時、6Wの入力で、100Wでました。 なによりも、うれしいのは、390PFのとき、効率が39%だったのに、対して、1390pFの場合、効率が52%まで改善した事です。

データには有りませんが、電源電圧35Vにて、7W入力すると、120Wくらいでます。 それより出力を大きくすると、安定化電源のフの字プロテクタが動作し、電源がOFFになります。

いくら、温度補償回路を追求しても、放熱板の強制空冷はマストです。 アンプユニットを挟んで、2個のファンを動かしています。 右側の外側についているファンは、この医療機器にもともとついていたもので、95mm角厚さ25mmのものですが、長年使っていたのか、少々騒音が大きいです。 左側のファンは右側と同じサイズですが、最近、秋月より購入した安価なものですが、こちらは、かなり静かです。

このふたつのファンで、風を左から右へ抜けるように、CPU用の放熱板に吹きつけています。 70W出力中にファンを1個止めると、Idがすこしずつ上昇を始めますので、効果はバツグンです。 ただし、電流の増加は数十秒でとまり、こんどはゆっくり減少に向かいます。 この減少に向かうのは、温度補償が効き過ぎている為で、弊害として1分以上エージングすると、ゆっくりと出力も減少します。 10分くらいのエージングで、50Wの出力が42Wくらいまで落ちます。 この弊害は、壊れるよりはましですので、このままです。

やっと、リニアアンプが完成しましたので、TSSへ保証認定を依頼している間に、エージングテストをやることにします。

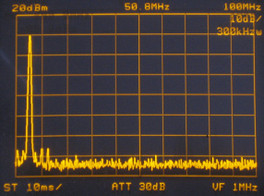

一応、まともに動き出しましたので、スプリアスや2信号特性を確認しました。

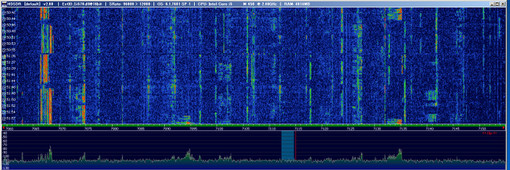

左上は70W出力時のスプリアス特性です。 100W出力にしたら、第2高調波を含め、さらに良くなります。右上は、7MHzのLPFの上部が開いていましたので、蓋をしました。 蓋の有り無しで、データは変わりませんでしたが、気休めです。

なお、これはFETのバラツキと考えられますが、各100mAのアイドル電流にした状態では、第2高調波が、-35dBくらいまでしか落ちていませんでした。 そのため、スペアナを見ながら、バイアス電圧をいじってみました。 結果は、一方はバイアス電圧を上げると、高調波が少なくなるのに、もう一方はバイアス電圧を下げた方が高調波は下がります。結局、両方とも100mAに調整した後、一方のバイアス電圧を下げる方向で調整し、-50dBはクリアーしています。

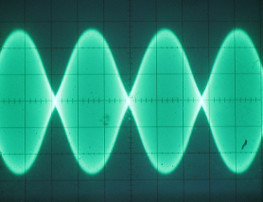

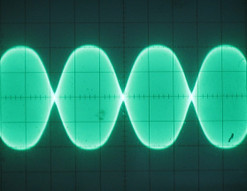

左上が40Wpep出力時の2信号特性です。 右上は、100W平均値出力時の特性で、100Wpepとは異なります。 ただ、この波形は70Wを30分くらい連続出力した後の波形です。

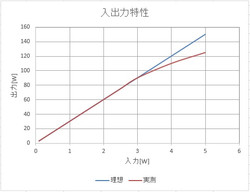

無信号送信状態にしておき、入力を5秒間加えて出力を測定し、直ちに入力OFF。次に入力ONまで10秒以上休むというやり方で、測定したデータが左のグラフです。 このデータを見る限り、90Wくらいまでは、リニアリティが確保されているのが判ります。 私のスペアナの分解能が悪く、IMD特性は見る事が出来ません。 測定専用のバンドスコープ付きSDR受信機を用意できたら、測ってみようとは思いますが、あまり良い特性ではないと、思われます。 ただし、変調音を聞いた感じでは、違和感は有りませんでしたので、当面はこのままです。

また、前回の調整から1か月以上経過したLO漏れとUSB漏れをチェックしましたが、いずれも -50dB以下を確保し、ドリフトはありませんでした。

リニアアンプのケース入れが完了しましたので、この状態で、エージングテストです。

久しぶりに、コメットのSWRメーターとオイル冷却ダミーロードを物置から引っ張りだし、TS-930Sを信号源として、エージングテストをしました。

まず、最初に100W出力で、2分間、連続出力した後、70Wに出力を落とし、そこから、30分間、連続出力を行いました。 時間経過とともに、出力が減少しますが、これは、TS-930Sの出力が下がるのと、このリニアアンプのゲインが下がるのが原因で、下がってきたら、TS-930Sの出力を上げ、常に70W出力が出るようにしました。 最初、入力2.5Wで70W出ていましたが、2分くらい経過すると、出力が下がり始めるので、出力70Wをキープするように、TS-930Sの出力を調整しました。 30分のエージングが終了し、その時のTS-930Sの出力は3Wになっていました。 その状態で、入力を10Wまで上げてみましたが、アンプ最大出力は100Wでした。

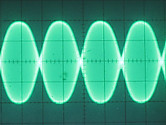

左上は、70W出力時のTS-930S出力。 右上は、リニアアンプの出力波形です。 出力波形は、スペアナのデータでも判るように、完全な正弦波です。

エージング終了後、出力を可変すると、30W前後の時だけ、約5MHzと10MHzのスプリアスが発生します。 原因は、FETの電流がこの付近の値の時だけ発振するようです。 多分、FETのゲインがこの出力付近で最大となるのでしょう。 対策として、ドレインからゲートへ1000p+1Kのシリーズ回路で負帰還をかけることで解決しました。

もともと、このケースのフロントパネルは紺色でしたので、このアンプも紺色で仕上げました。 メーターの左側に縦線が見えるのは、A4サイズのプリンターでは、パネル全体を印刷できず、この線の部分を境に分けて印刷した為です。

TSSの保証と、総通の許可が降りたら、ON AIRにトライします。

10Wのトランシーバーでもコメントしましたが、サウンドカードの中のブロック図は理論的に考えられるブロックで、HDSDRの中が、このようになっているかは確認していません。

このテストの途中、送信から受信にした時のタイミングが、SDRより、リニアアンプの方が、かなり遅れます。 遅れは1秒以上です。 原因を調べたところ、SDR側のフォトカプラーのLEDにつながる電源ラインが、負荷となるリレーとデカップリングコンデンサの為、かなりゆっくり降下し、その間、LEDの消灯開始電圧まで、フォトカプラーの2次側TRがONしたままになっていました。 対策として、フォトカプラー内のLED両端に510Ωを並列に入れ、電源ラインが6V以下になると、LEDが消灯するようにしました。

LED消灯対策済み 7MHz_SDR2.pdfをダウンロード

70W 30分のエージングテストは終了しましたが、ON AIRの許可が出るまで2週間はかかりますので、ダミー抵抗に出力しながら、模擬運用を行っていますが、事故が2件発生しました。

まず、40Vでテスト送信を開始したら、どこかでスパークが起こり、明るくなったのですが、どこでスパークしたのか判りませんでした。 それでもアンプは正常に動作しており、正常にテストが終了しました。 後日、コンベンショナルトランスのメンテの為、これを取り外すと、電源が供給されるチョークコイルを通った後の、コモン部分に設けた4個の104Kの内、2個のチップコンデンサが黒焦げになっていました。 チップコンデンサが黒焦げになりましたが、オープン状態となった為、アンプは正常にに動いていたものです。 このコンデンサはDC50V耐圧のもので、ここに通常電源電圧以上の電圧は加わりません。 壊れたチップコンデンサはメーカー不明の秋月から買ったもので、壊れなかったコンデンサはRSで買ったTDK製でした。TDK製は全部使い果たし、秋月のものしか手持ちがありませんので、秋月のものに、とりあえず交換しました。 1週間後、このスパークが再発しました。 壊れたのは、また秋月から買ったチップコンでした。 今度は、村田SSのラジアルタイプ0.1uF2個に変更し、様子を見る事にします。

35V 20Wくらいで、エージング中にアンプ入力をON/OFFしていたところ、突然、出力なしになりました。 調べると、FETと電源は正常、 バイアス電圧が2Vくらいまで下がり、FETがカットオフ状態になっていました。 この原因も入力トランスからの信号をFETのゲートに接続するとき、絶縁の為に挿入した50V 104Kのチップコンデンサが、絶縁不良を起こし3KΩ位の抵抗値を示していました。 ここでもDC50Vを超えるような電圧がかかるとは思えないのですが、壊れてしまいました。 修理は、同じ50V 104Kに交換です。

FETのゲートバイアスの温度補償が、効き過ぎの状態でしたので、左のグラフのように、温度変化に応じて、傾斜が変わるような回路を作り、その効果を確認してみました。

このカーブは、R37、R38の値をパラメーターとして、作成したものです。 グラフはVR4によるバイアスを3.5Vくらいに固定して作成しましたが、VR4を動かすと、飽和レベルが上下します。

VR4による固定バイアスを実際に動かしながら、実験した結果、従来の回路では、例えば、50W出力から、いきなり入力をOFFにした場合、即、元のアイドリング電流以下まで戻り、ひどい時は、一瞬0mAになります。 これは、高出力時、回路がB級ではなくC級で動作していたことを意味し、リニアリティの悪化につながります。

正常なバイアス状態は、出力レベルにかかわらず、常にB級もしくはAB級で動作する事ですから、入力OFFしたら即座にアイドリング電流値に戻らねばなりません。

従い、実際の調整方法は以下のようになります。

まず、R37,38を2.2KΩに固定しておき、さらにVR1,VR2最小の状態でVR4を最小電圧になるようにしておき、VR1とVR2を調整し、アイドリング電流が100mAになるように調整して置きます。 そのあと、出力を70Wくらいまで上げ、FETが十分熱くなったら、急に入力をOFFします。 すると、ドレインに流れる電流は即、アイドリング電流まで落ちるか、あるいはそれ以下になります。

同様にして、VR1,2を最小にした後、VR4による初期電圧を少しあげ(0.2V刻みくらい)、VR1,2でアイドリング電流を100mAに調整します。そして、また70W出力にした後、入力をOFFした時の電流を観察します。

これを何回か繰り返していくと、あるVR4の電圧を超えると、入力を調整し、OFFしても,即アイドリング電流に戻らず、数秒から10秒以上遅れるようになります。 この遅れが発生するようになった場合、70W出力の時、アイドリング電流が増えていることを意味します。

そこで、VR4による電圧を少し下げて、入力OFF時、即、電流がアイドリング電流まで落ちるポイント選び、その状態に固定します。

これで、温度補償を考慮したバイアス電圧の設定は完了しましたが、場合によっては、出力レベルにり第2高調波が、規定の50dB以下に収まらない事が発生します。

もし、そのような現象が発生した場合、以下の調整を行います。

VR4は先に決めたポジションにしたまま、再度アイドリング電流をVR1,2を調整して、今度は120mAくらいに設定し、入力を次第に上げていくと、出力レベルにより第2高調波レベルが変動する現象がみられます。 この現象が現れたら、第2高調波レベルが一番高くなる出力にしておき、そのレベルが小さくなるようにVR1かVR2どちらか一方を調整します。 どちらを調整すのかは、VR1もしくはVR2をバイアス電圧が低くなる方向に回したとき、高調波レベルが下がるVRのみを調整します。

このようにして調整した結果、100W出力で第2高調波を60dB以上低くする事ができます。 ただし、ある程度が限度で、VRを調整しても低くならないときは、LPFのATT量が不足とか、LPFの入力が出力と結合しているとか、ほかの要因が考えられます。

この調整方法はスペアナが無くても可能です。 第2高調波である14MHzを受信して、7MHzの基本波より50dB以上低ければ問題なしです。

この調整状態で確認した2信号特性のリニアリティが以下の波形です。 80Wくらいまでなら、我慢できる波形をしています。30分エージング後の波形で、左から順に60Wpep、80Wpep、100Wpep出力時の2トーンの波形です。

また、当初より有ったエージング中にゲインが低下する件も若干の改善がみられました。 入力2.2Wで70W出力があった状態で、30分エージング終了後、同じ70Wを出す為の入力は2.4Wくらいでした。 なお、30分エージング後の最大出力は入力を10Wにしても、100Wと変わりませんでした。

下の写真は、完成したリニアアンプの内部です。

1週間で、TSSの認定がおりましたので、即日、総通へ、SDRトランシーバーとこのリニアアンプの追加申請を行いました。 そして、さらに1週間後、総通から審査終了のメールが届きました。 指定事項の変更はないので、即ON AIRできますが、その前にHFのアンテナの整備が必要なようです。

HFのアンテナを4か月くらい使っていなかったのですが、ベランダのMTUを調整して、いざ、送信機に繋ぐと、SWRが3以上になります。 色々試した所、同軸の長さでSWRが変わります。 また、新しい問題が出てきました。 1時間余り奮闘した結果、MTUにつながるMコネクタのゆるみが原因でした。 それを対策して、CQを出しました。 1エリアのOMさんとつながりましたが、了解度がさっぱりです。 RSの交換のみで終わってしまいました。 そのときのバンドスコープが以下です。

コンディションが良い時は、左にある橙色の帯が画面いっぱいに広がるのですが、さすがに、カーソルが示す周波数帯の信号は、良く見えません。 相手の方には59で届いているみたいですけど、残念ながら、こちらの受信状況はR2くらいでした。

ここで、送信と受信のアンバランスが問題として浮上してきました。 今後の課題です。

dsPICでSSBトランシーバー(SSBジェネレーター)へ続く。

実際に運用を開始すると、バイアス回路やファンモーター駆動用の12V電源のトランジスタがあっちっちになります。 この対策の為、電源回路に14VのDC出力を追加し、12V電源は電源から直接供給を受ける様に変更を行いました。 ところが、リップルが多くて、12V電圧では、ハム音が変調されますので、9Vの3端子レギュレーターをダイオードで0.6Vほどかさ上げし、9.6Vの安定化電源を作り、これでモーターとバイアス回路をまかなう事にしました。

最終状態の配線図 PWR-AMP100W_8.pdfをダウンロード

200Wリニアアンプの検討はこちら。