<カテゴリ AM送信機(PWM方式)>

13.8Vの電源で100Wの出力が得られるファイナルステージのアンプは完成しましたが、これをTS-930Sにてドライブした場合、7Wの出力が必要でした。 クリスタルOSCの出力でこのファイナルステージをドライブする為には、正弦波に近い7Wの出力が必要となりますので、ドライバーだけでQRP送信機より大きな出力の送信機が必要になります。

7Wの送信機が必要としても電源電圧は12V固定とすると、かなり小さなFETでも出力できる可能性が出てきます。 小電力のFETなら、TC4422やTC4452などの専用のFETドライバーを使わずに、CMOSゲートICだけでドライブ出来る回路が実現できそうです。

そこで、この小電力で入力容量の小さいFETを探すと、RSで見つかりました。

IRFI510GPBFというモールドタイプのFETで最大5Aですが、入力容量はノミナル値で180PFしかありません。 このFETを終段として、7WくらいのRFアンプをプッシュプル回路で作る事にしました。

ドライバー回路付の回路図 7M_amp_3para_driver.pdfをダウンロード

実験の途中に過大入力を加えた為、IC1の1番ピン(1A)を壊してしまいました。 そこで、遊んでいたIC2の3A-3B回路を使う事にしましたので、74HCU04の周辺が複雑になっています。 過大入力の保護回路を追加し、無信号時、FETのゲートが常に0Vになるようにクランプ回路を追加してあります。

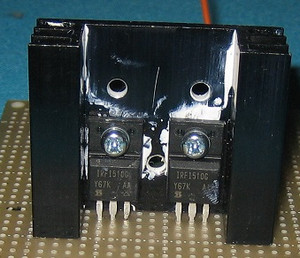

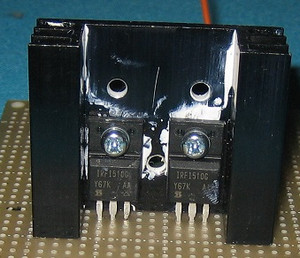

100Wアンプの入力インピーダンスは3.5Ωくらいでしたので、ドライブ用FET Q5,Q6を入力容量の小さいIRFI150に変更したところ、5.5Ωくらいまで上昇しました。

T2の巻き数比は3:1ですから1次側から見たインピーダンスは約50Ωです。 ここにQが約3.5くらいの直列共振回路を経てT3につながります。 T3の巻き数比は1:2(実際は0.5:1)ですから、T3の1次側は12.5Ωとなり、ここに12Vを加えますと、最大9Wくらいまで出力をとりだせますので、直列共振回路の共振周波数をずらして出力を調整します。

この状態で7Wの出力が出るように検討した回路が添付の回路図です。

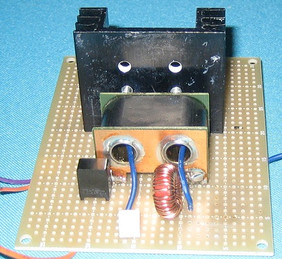

L2はカーボニルコアに0.6φのUEWを巻いて4uHのコイルにし、直列共振のコンデンサC7はとりあえず、最大350PFのバリコンを使用しています。

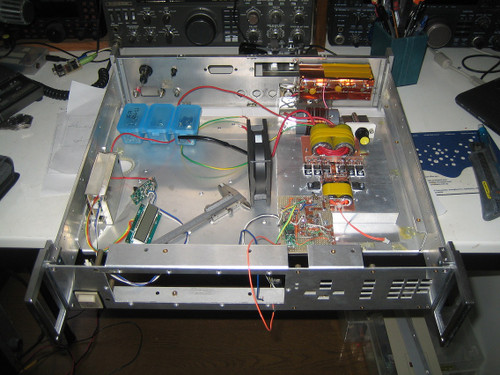

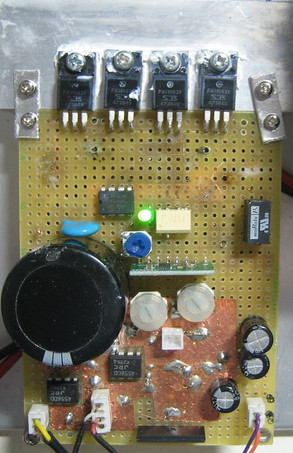

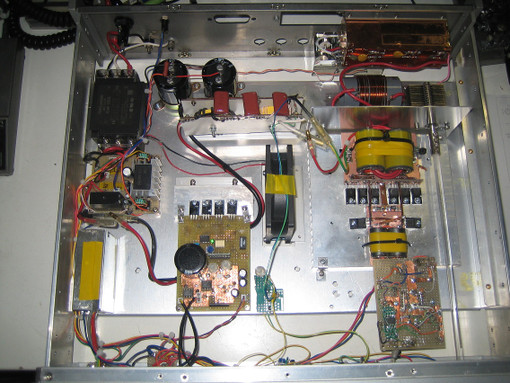

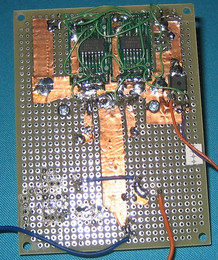

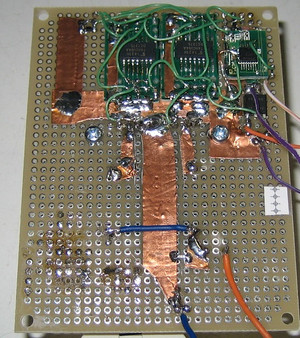

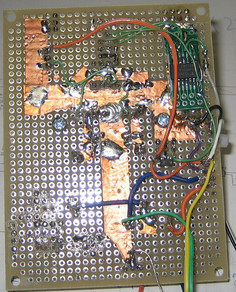

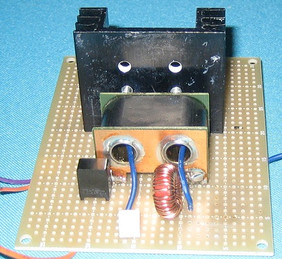

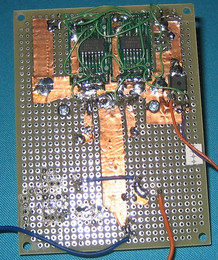

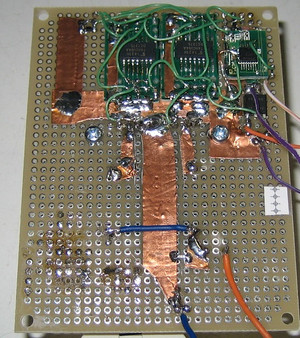

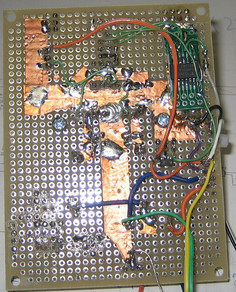

左上がRFトランスにTS-930Sのパワーアンプで使われていた入力トランスを使用した、7W出力のD級PPアンプです。 右上はその基板の裏側で、大きな部品は74HCU04 2個と5Vの3端子レギュレーターくらいです。 不要インダクタの発生を抑える為に、蛇の目基板の配線は出来るだけ銅箔テープで行っています。

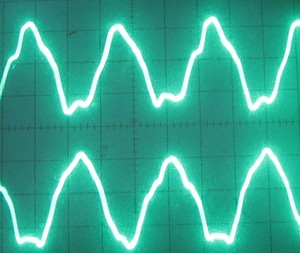

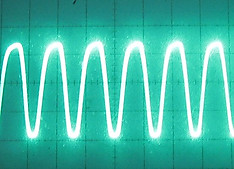

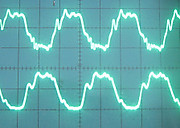

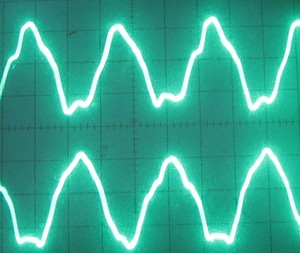

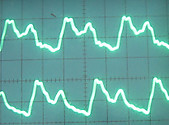

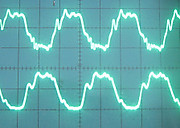

左は、ドライバー出力のLC共振回路のVCで、終段のFETのゲート電圧の波形が上下で大きく崩れないように調整した時のゲートドライブ波形です。

波高値は5Vppくらいです。 ここは7Vppくらいは欲しいところですので、 終段が動作状態になってから、直列共振回路を調整する事にします。

この状態の時のドライバー回路の消費電流は電源電圧12Vで0.46Aくらいでした。 約5.5WのDC入力ですから、仮に効率90%としても5Wくらいしか出力していませんが、なんとか終段FETのドライブが出来ています。

Q5,Q6のゲート電圧を7Vppくらいまで上げようとすると、ゲートのドライブ電圧のデュティが変わってしまい、均等なドライブが出来ない事が判りました。 原因は74HCU04の初段に加えられた正弦波の電圧値が変わると、このデュティが変わってしまうという問題です。

アナログ的な対策をいくつか検討しましたが、バラツキの要素を取り除く事が出来ません。

恒久対策としたのは、RF信号は14MHzで発生させ、これを途中で1/2にして、デュティを50:50に強制的に合わせこむ方法です。

新回路図 7M_amp_3para_driverPLL.pdfをダウンロード

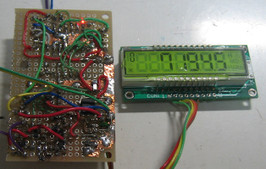

左の基板で右上に追加された小さな基板が74LVX74です。 以前実験した2mまで使えるデジタルSWR計用の基板から切り出しました。 このICは150MHzくらいから分周に使用できます。ICは2個のFFを内臓していますので、配線は2個を直列に接続した1/4分周器となっていますが、今回の回路では、1/2分周部分から出力を取り出しています。

TS-930Sから14.4MHzの1W以下の信号を加えて、綺麗なFETドライブ波形が得られました。 実際に使う時は、以前試作してお蔵入りとなっている7MHzのPLL VFOを14MHz用に変更して使います。 前回は原発振周波数とパワーアンプの出力が同じ周波数でしたので、出力段からVCO回路へ回り込みが発生し、キャリア近辺のスプリアスが増えると言う問題で使えなかったのですが、今度は、出力周波数とVCOの原発振は異なります。 出力周波数の2倍の高調波がVCOと重なりますが、そのレベルは30dB以上低くなっていますので、多分大丈夫だろうと予想しています。

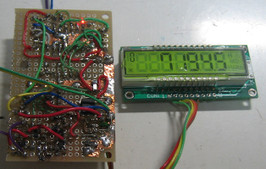

ジャンクボックスの中から、以前作成した7MHz用PLL VFO基板を引っ張り出し、ハードと、ソフトの変更を行いました。

PLLの原発振は14MHz台ですが、LCD表示は、その周波数を1/2分周した7MHz台となります。 14MHzも1KHzの周波数スパンで可変できますから、これを1/2分周すると、7MHzは0.5KHzスパンで変化する事になります。

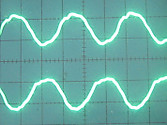

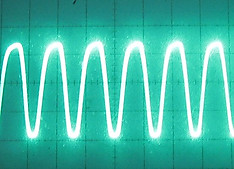

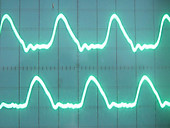

左上は、PLLの原発振を14MHzに変更した基板と7194.5KHzを表示しているLCDです。右上はこの時のPLL VFOの出力波形で周波数は14389KHzです。 波形は上下非対称で歪んでいますが、この後段で1/2分周しますので、デュティには影響有りません。 レベルも7Vppもありますので、ATTが必要になるほど有り余っています。

14MHz PLL VFOの回路図 PLL_OSC_schema14.pdfをダウンロード

14MHz PLL VFOのソースコード PLL_VFO14to7.cをダウンロード

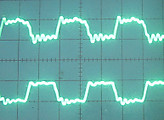

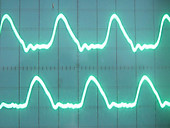

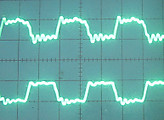

PLL基板、ドライバー基板、終段基板をつないでみました。以下はその時の波形で、左から、Q9,Q10のゲート電圧、Q9,Q10のドレイン電圧、Q5,Q6のゲート電圧です。

真ん中のQ9,Q10のドレイン波形は理想よりかなり離れておりますが、Q5,Q6のゲート波形はなんとか使える状態です。この状態でファイナル段に電源電圧5Vを加えると、最大で10Wしか得られませんでした。 また、この時のQ9,Q10のドレイン電圧は30%以上のレベル差がありました。 原因を調査したところ、Q9,10のIRFI510をフルスイングするのに必要なゲート電圧は8V以上必要で、5Vのゲート電圧ではノミナル1Aくらいしか流せない事でした。 FETのバラツキによっては1A以下しか流せないものもあります。 要するに5Vの電源で動作する74HCU04ではドライブ不足という事です。 5Vの3端子レギュレーターのGNDにゲタをはかして6Vにする実験もしましたが、少しだけ良くなる程度で、正、逆の電圧差は解消しませんでした。

バラック状態で、あっちがショートしたり、こっちが外れたりとトラブルが相次ぎ、またまたドライバー段のIC3 CLOCK入力が壊れてしまいました。 この修理の途中で5Vの3端子レギュレーターが壊れた事に気付かず、12Vの電圧がスルーして、74HCU04を2個、74LVX74を4個も壊してしまいました。 ICはまだ手持ちしていますが、これ以上の検討を諦め、正規のFETドライバーを探す事にします。

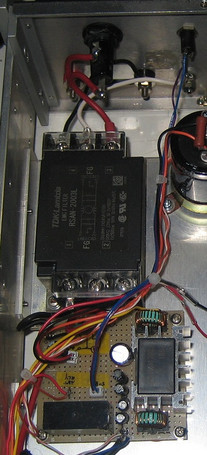

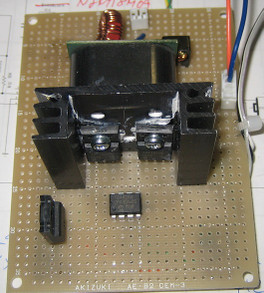

RSでFETドライバーを検索すると、極端に安いドライバーが見つかりました。 1個90円ですが、1.5Aのドライブ能力があり、スピードもTC4422並みです。TC4426という品番で8PIN DIPの中に2回路入っています。 ただし、このICは反転出力です。 非反転出力のICはTC4427という品番ですが197円もします。 反転出力のICは人気がないのかも知れません。 私が使う場合、反転も非反転も関係ないので、安いTC4426に決定しました。

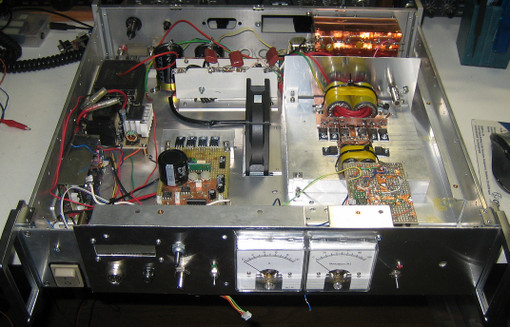

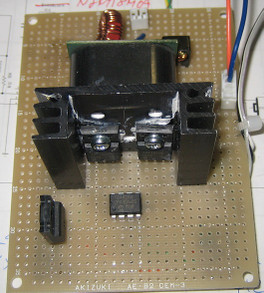

左上がTC4426を使った基板裏側、右上が部品挿入面で、8pinのDIPがTC4426です。 このFETドライバーを使う事により、従来あった74HCU04の回路がなくなりましたので、回路的にはかなりすっきりしました。 TC4426は9Vの3端子レギュレーターから電源供給させます。また、14MHzを1/2分周するICは74HC74に変更し、このICが持っている反転出力を使い、直接TC4426を互いに逆相でドライブします。 TC4426の入力部には+5Vに電位を固定するクランプ回路を入れ、14MHzが供給されない時は、FETのゲート電圧が両方とも0電位になるようにしています。 下にその回路図を示します。

回路図 7M_amp_3para_TC4426driver.pdfをダウンロード

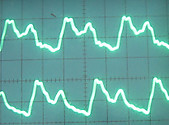

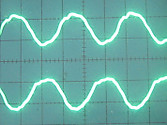

上の波形は左から、Q9,Q10のゲート、真ん中はQ9,Q10のドレイン、右はQ5,Q6のドレインすなわち、終段のゲートドライブ波形です。 この終段のゲート波形は10Vppを超えていますので、ドライブ能力は十分と考えられます。 まだ終段には電源がつながれていません。 真ん中のQ9,Q10のドレイン波形はプッシュプルのアンバランスも解消し、画期的に改善しました。 そして、なんとなく判った事は、ドレインの電圧波形のピークがつぶれて凹む現象はドライブ不足が原因であると言う事でした。

現在は、FETの破壊を恐れて、恐る恐るチェックしていますので、全体像はまだ見えていませんが、なんとか使える状態になったと思われます。

机の上にオープン状態に置き測定した出力は

5V時 16W

6.9V時 26.4W(13.8V時 105.6W)

13.8Vとそれ以上の電源電圧時の出力は、シャーシに組み込み、ファンが動くようになってから確認する事にします。

なお、この状態でQ9,Q10の電流は1.2Aくらいになりましたので、約14.4WのDC入力です。 効率80%とすると、約11.5Wくらいの出力になっている模様です。

7MHz D級アンプ QRO計画4(組み込み) へ続く。

INDEXに戻る