7MHz D級アンプ QRO計画 2

<カテゴリ AM送信機(PWM方式)>

サンケンのFKI10531というN-MOS FETによる2パラプッシュプル回路は、6.9Vの電源で22Wの出力を得る事ができましたが、この時点でMax Vdsは40Vありました。 これは13.8Vの電源で80Vになる事からFETの最大Vds=100Vの規格に対してほとんど余裕が有りません。実験中にFETを壊すのは確実ですから、実験前に諦めてしまいました。

RSで適当なFETがないか探すと、以前チェックした事があるSTマイクロのSTF17NF25というFETが86円くらいでありました。これならVds max 250Vですので、かなり余裕が出来ます。 これを10個購入し、このFETで再度6.9V 25W出力に挑戦します。 ただし、このFETのRdsは165mΩくらいありますので、4個パラくらいにしないと、FKI10531と同等のRdsにはなりませんが、とりあえずは、3個パラプッシュプル(合計6石使い)でトライします。

回路図 POWER_amp_3para.pdfをダウンロード

比例計算では6.9Vの電源で21.4Wくらいになりますが、その他のロスの軽減策でチャラに出来るくらいのロスです。

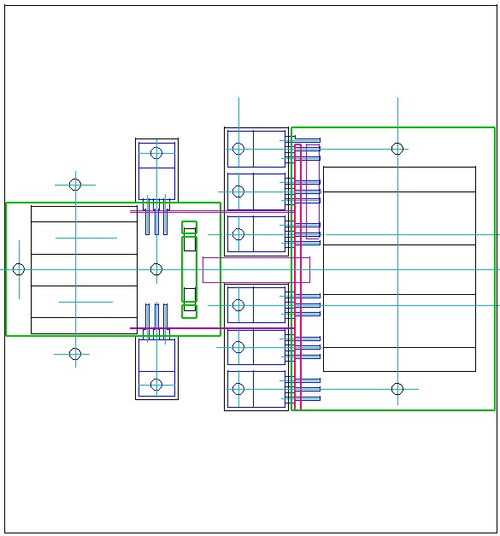

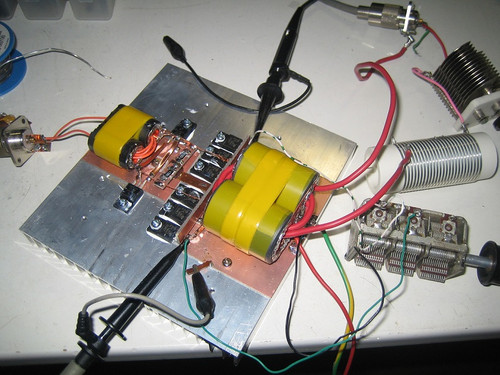

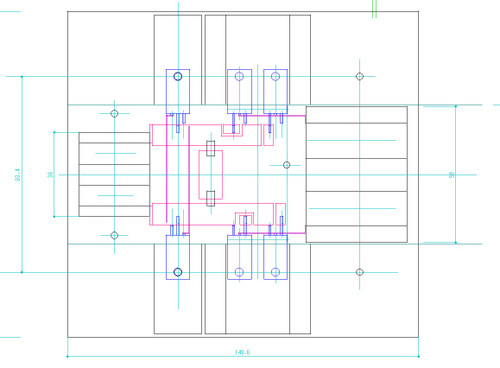

上の図面は、リンギング対策の為、FETのレイアウトを変更した、3パラプッシュプルのD級アンプ回路です。放熱板のサイズは前回と同じですが、向きを90度変えてあります。

この新アンプより、両面ガラエポの基板が使えるようになりましたので、基板は生基板をそのまま使います。加工するのは、ゲート入力回路のみで、ダイソ-で買った300円のミニドリルの刃先をグラインダーに付け替え、銅箔を削ってパターンを作り、チップ部品を装着できるようにします。 それ以外の配線はすべて短冊状の銅板で行います。

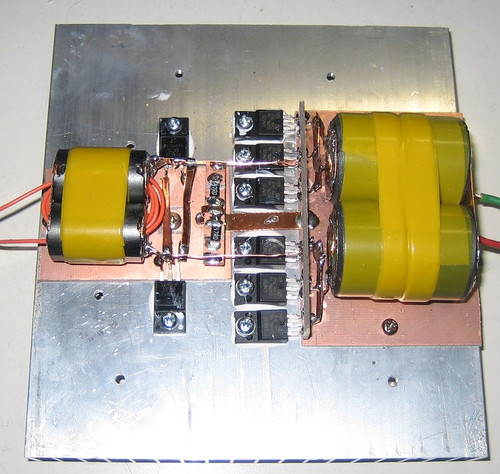

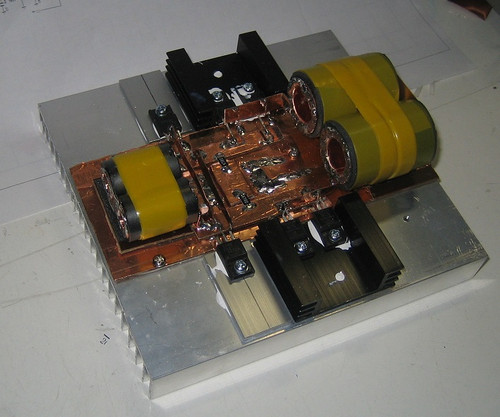

上が図面通り、放熱板や基板を加工して配線完了したアンプユニットです。放熱板のサイズは前回と同じです。

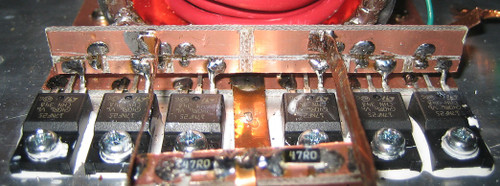

上は、6個のFETとそのゲート入力回路の基板です。各FETのゲートに1608の1Ω抵抗をシリーズに入れた手作り基板です。 リンギング対策の基本は構造が簡単であるという事ですが、この構造なら、4パラでも6パラでもすぐにできます。

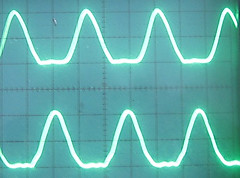

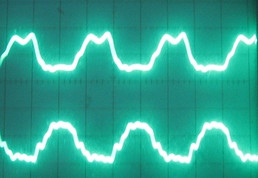

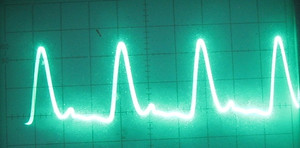

左上は、電源電圧を3Vにして最大出力ポイントより30%くらいパワーを絞った時のVds波形です。 右上は同じ電源電圧にて、最大出力時のVds波形です。 ドレインGND間にバリコンをいれリンギング最小状態にしてあります。 まず、プッシュプルの両側で波形が異なります。また、この時の最大波高値は前回の半分くらいになっています。 どうも動作モードが変わってしまっているようです。

原因を調べたところ、最大波高値が下がったのはFET3パラによる出力容量の増大が影響しているみたいです。 また、プッシュプルの両側で波形が非対称となっているのは、ドライブ入力部のFETを含むアースポイントが最適になっていないようです。 また、入力トランスの入力部分(TS930Sの出力端)の波形がきれいなサイン波からかなり崩れています。 これらは、今後ドライブ回路の設計のなかで、詳細を検討する事にします。

しかし、ダミーアンテナの両端波形はLPFなしですが、一応まともな波形をしています。

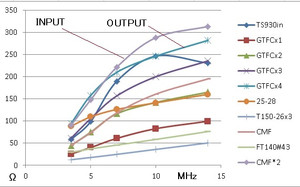

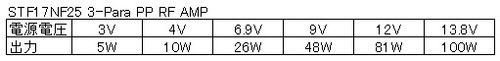

肝心な出力ですが以下のようになりました。

一応当初の目標6.9Vで25W、13.8Vで100Wの出力を確保できました。 Rds=165mΩは最大値ですので、実力は結構低いのではないかと思われます。

一応当初の目標6.9Vで25W、13.8Vで100Wの出力を確保できました。 Rds=165mΩは最大値ですので、実力は結構低いのではないかと思われます。

この時のTS-930Sからの出力は7Wでした。 効率は3Vの電源の時70%くらいでしたから、100W出力時は70%以上あると思われます。 また、入力を7W以上にするとリンギングが多くなりますが、出力は変わりません。 逆にに7W以下にすると次第に出力は低下しますが、リンギングも改善され、最大出力の30%減くらいできれいな写真のような波形となります。

このアンプを2台シリーズに繋ぎ、電力合成すれば、13.8Vの電源で50WのAM送信機が出来ることが判りましたが、この13.8V 50WのAM送信機の使い道が有りません。今の所、AMで移動運用をするつもりは有りませんので、このパワーアンプはここで終わりにします。

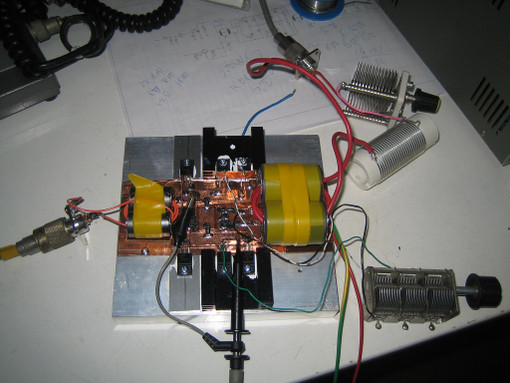

上は、この新RFアンプの実験風景です。

これから、入力ドライバー回路の検討を行い、現行の50W AM送信機をQROする方向に目標を変更します。

7MHz D級アンプ QRO計画 3 に続く。