7MHz D級アンプ QRO計画 1

<カテゴリ AM送信機(PWM方式)>

キャリア出力50W(ピーク出力200W)のAM送信機は完成し、時々ON AIRしていますが、この送信機を製作始めたころの最初の目標「12V電源で50Wの送信機」はいまだに実現しておりません。 SSBトランシーバーでは13.8Vの電源で100Wの送信機は当たり前ですから、市販のトランシーバーは13.8Vの電源で25W出力のAM送信が普通に可能です。 そこで、当初の目標であった13.8Vの電源で50WのAM送信機(ピーク200W)に再挑戦する事にしました。

今回検討するパワーアンプの回路図です。POWERAMO_0.pdfをダウンロード

終段はサンケンのFKI10531パラレルプッシュプルでこの回路でまず25Wを狙います。 首尾よく目標達成できたら、同じものをもう1台作り、電力合成して50Wが実現できるだろうというもくろみです。

終段をドライブするには終段の入力容量は3000PFを超えますから、従来のTC4452などでは無理で、昔のトラ技に紹介されたFETをクロスして配置したオーソドックスな回路にもどしております。この回路では、ドライブパワーとして3Wくらいが必要になりますので、実際はこの前段に5WクラスのC級アンプをおきますが、実験の初期はTS-930Sから50Ωの出力インピーダンスで5Wくらいでドライブします。

まずは、入出力に使うメガネコアの吟味です。

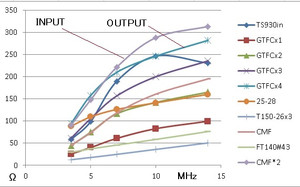

左のグラフは手持ちのフェライトコアに1ターンのコイルを通した時の周波数対インピーダンスを表示したものです。 デジタルでインピーダンスを表示できる手作りアンテナアナライザで実測しました。 この中で、TS930Sの入力トランスの実測カーブが濃い青色で示され、特性は10MHzをピークに14MHzでは下がっています。 一応この特性を目標に、コアを調査した結果、INPUTと表示してある、昔1個30円で買ったコモンモードチョーク用の分割コア(CMF)2個分が一番良い特性を示しました。 次に出力用としては、北川工業の分割コアGTFC4個分(OUTPUTの表示)でそこそこいけそうですので、これらを使い、メガネコアを手作りする事にしました。

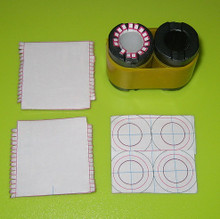

左上の写真は、CMFコアを2個ビニールテープで縛り、その状態での寸法を基に、コアを貫通する銅パイプと側面でこれを受け止めるリングの図面をJW-CADで作図し、これを実寸大にプリントアウトした紙を厚さ0.3mmの銅板に貼り付け、ハサミで切り出した銅板です。 銅板をリング状に切り取る為に、まず「タケノコ」と呼ばれるドリルでリングの中心部分に穴を明けた後、外周をハサミで切り取って作ります。

右上の写真は出来た銅板をフェライトコアの中に埋め込みワンターンコイル付メガネコア状にしたものです。 この状態で裏、表ともハンダで結合すればメガネコアによる入力トランスが完成します。

同じようにして、出力側のメガネコアも作成します。

左側の大きなメガネコアはGTFC 28-16-13という分割コアを4個使い、ビニールテープで縛りまくった状態で銅板によるパイプとリングを作り出来上がったもので、外形は58x43x28mmでパイプの内径は12.5mmあります。

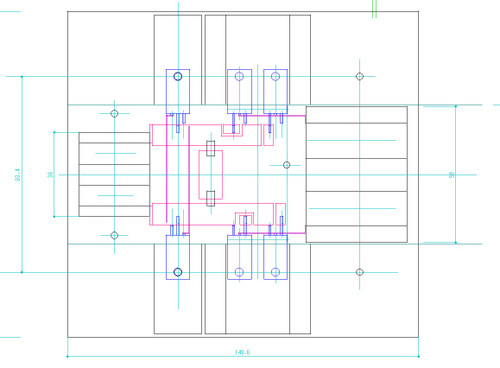

メガネコアのサイズが固まりましたら、これを基板上に配置し、FETを放熱板に固定する構造を考えながらパワーアンプ全体のレイアウトを決めます。 プリント基板は片面ガラエポをカッターで削りながら作る条件で、立体配置図をJW-CADで作成します。

この作業はプリント基板のように平面で回路を構成する電気屋の作業ではなく3D構造で回路を構成する為、機構屋の作業になってしまいます。

上の図面はこの3D構造のパワーアンプ部分をJW-CADの2D図面で描いたもので、FETの配置を青色で、基板のパターン構造を赤色で示してあります。

上の図面はこの3D構造のパワーアンプ部分をJW-CADの2D図面で描いたもので、FETの配置を青色で、基板のパターン構造を赤色で示してあります。

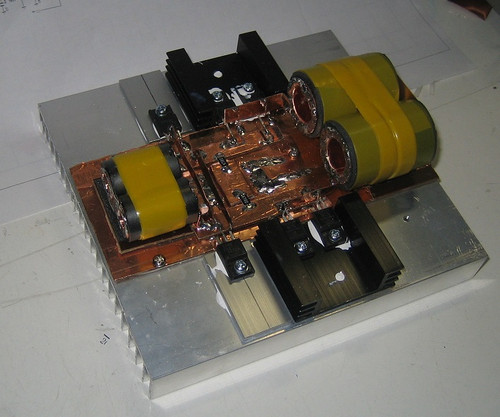

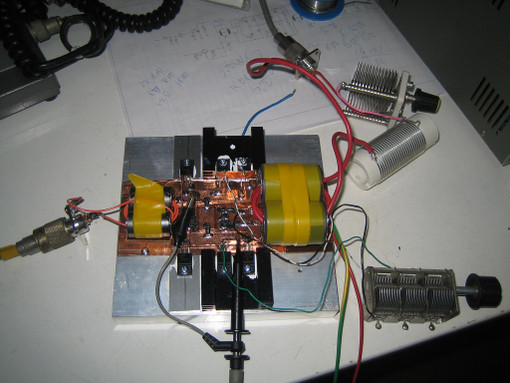

この後、放熱板や、基板を図面通り加工すると、下の写真のようなパワーアンプが完成します。 ただし、ガラエポの基板はまだ未入手ですので、紙エポの銅箔なし基板に厚さ50ミクロンの銅箔テープを両面テープで張り付け基板の代用としています。

このパワーアンプの入力トランスに2ターンの1次コイルを巻いてアンテナアナライザで入力側のSWRを測ったところ、SWR=6くらいでした。この状態でTS-930Sから出力を加え、電源電圧3Vの状態で出力が飽和するレベルは12Wくらいでした。 そこで、1次の巻き数を3ターンして、再度トライするとTS-930Sの出力が6Wくらいから、D級アンプの出力は飽和します。 次に4ターンの1次コイルを巻き動作テストを行いました。 TS-930Sの出力が3WくらいになるとD級アンプの出力は飽和します。このときの入力側のSWRは1.8くらいでした。 以後、この状態でのテストです。

出力側のメガネコア(出力トランス)の2次巻き数は2ターンです。

Vds=5V 出力6.8W

となりました。これは従来の50Wアンプと同じ出力インピーダンスの場合に相当し

Vds=15V 時 出力は61Wに相当します。

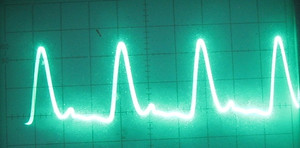

上の波形は、Vds=3V時のドレイン電圧波形です。 従来の50Wアンプよりリンギングが多くなっており、最大出力にすると、ゼロレベルの部分にもう二山波形が現れるほど、乱れます。 最大出力付近でのリンギングを最少にする為、ドレインとGND間にバリコンを挿入し、リンギング最少になるようバリコンを調整しています。 ただし、今回の回路では、ドレインとGND間にコンデンサを入れてもドレインピーク電圧は下がりませんでした。

次に出力トランスの2次コイルを3ターンとし、バリコンでリンギング最少とした状態で

Vds=3V 4.2W

Vds=4V 7.1W

Vds =4.9V 10.4W (この時の電流は2.972A)

Vds=6.9V(13.8Vの1/2)のとき、22W

この状態で終段FETのドレイン電圧はmax40Vまで上がっていました。 またこの時のリンギング波高値は10Vくらい有りました。

という事は、13.8Vを電源としたAM送信機の場合、ピークパワー時80Vのドレイン電圧となりますので、Vdmax=100VのFKI10531では25Wの目標はかなりきついとい事が判ってきました。

過去の経験から、このギリギリのスペックでは、実験中にFETが壊れる確率が100%近くになりますので、FETの再選定は避けられなくなりました。

上の画像は、この出力テストの実験風景です。

リンギング対策の為、GNDの引き回しを再検討する必要が生じ、一度分解し、レイアウトをやり直した上で、FETの選択をやり直す予定です。

7MHz D級アンプ QRO計画 2 へ続く。