VXO再検討

<カテゴリ AM送信機(PWM方式)>

PLL VFOを試作し、キャリア近傍の不要輻射の為、採用を断念した代わりに、可変の拡大が可能なVXOについて、再検討する事にしました。 PLL VFOの時取ったVXOの不要輻射が以外と良い事に気付いた事によります。

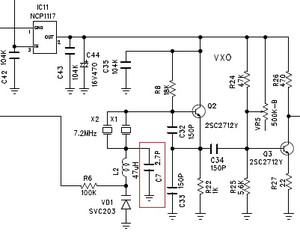

現在のVXOは、いわゆる「スーパーVXO」と言われる、水晶発振子を2個パラに接続した回路で、11kHzの可変範囲を確保していましたが、AMのもうひとつの常用周波数である7181KHzはカバー出来ていませんでした。

まず、60PFのトリーマーをSVC203CというONセミコンのバリキャップに変更してみました。バリキャップの最大DC電圧を8Vとした時の可変範囲は7197KHzから7186KHzとなり可変範囲は変わりませんが、全体が1KHzほど低い方へシフトしました。 この状態で単純に水晶発振子を2個から3個に増やしてみました。 すると、最低周波数が7165KHzくらいまで拡大しましたが、最高周波数は7194KHzくらいとなります。 メインの7195KHzをカバーできないので、この方法は採用できません。

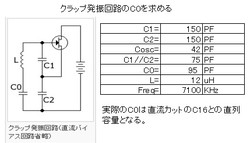

FCZ研究所の機関紙でコンデンサを追加して、可変範囲を拡大するアイデアを紹介していましたので、水晶2個の状態で、水晶とコイルの接続点からGNDへ4.7PFを追加して見ました。 すると、周波数可変範囲は200KHzを超えて7000KHz以下まで発振し、かつ最高周波数は7195.2KHzとなりました。 しかし、7100KHz以下の周波数では、かなり不安定で、CWモードでのビート音もなにか不安な音です。

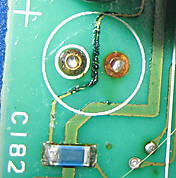

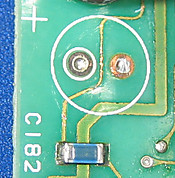

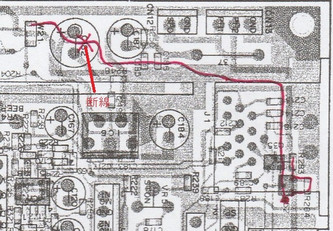

そこで、このコンデンサを2.7PFにした上で(赤枠で囲んだC7)、バリキャップ電圧を上げる為に9Vの専用3端子レギュレーターを追加しました。 その結果、

最高周波数:7195.5KHz 最低周波数:7159.4KHz

となり、ビート音も澄みきっています。 目標とした7195と7181はカバーできましたので、どうやら使えそうです。

使用した水晶発振子はaitendoで扱っている uxcellのHC-49Sタイプ 7.2MHz

47uHのコイルはRSで扱っているTDKのNL453232T-470J-PFというSMTタイプです。

発振回路に使われているトランジスタは、東芝の2SC2712Yですが、リードタイプの2SC1815Yと同等品です。

その後、このVXO回路を200W AM送信機にも使いましたが、気温の低下と継時変化により、最高周波数7195.0KHzが確保しにくくなってきました。 よって、クリスタルを2個から1個にして、C7を2.7Pから3.9Pに変更しています。 この変更後の状態で、周波数は7196.6KHzから7173.0KHzまでをカバーしています。

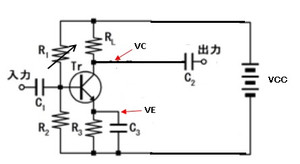

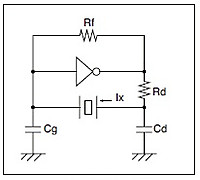

アナログ回路でベース抵抗を決定する方法を紹介しておきます。 これを知っていると、大抵のトランジスタやFETを好きなように使う事が出来ます。

左の回路に於いてR1を可変抵抗器にしておきます。 可変抵抗器は100KΩから1MΩくらいを用意しておき、回路の状況で使い分けます。判らない時は1Mか500KΩくらいでトライします。

コレクタにテスターを当てこの電圧が以下の式に合うようにR1の可変抵抗を調整します。

VC =VE + (VCC - VE) / 2

R1を可変するとVEも変わりますので、都度VCとVEを見ながら行います。 VCが目的の電圧になったら、R1を取り外し、テスターで抵抗値を計ります。 そしてE12シリーズの抵抗で最も近い値の固定抵抗に置き換えます。 R3が無い時はVEが常にゼロですから、VCはVCCの1/2にすれば良いのですが、温度安定度が極端に悪くなりますので、最低でも数10Ω以上の抵抗を挿入必要です。 この方法はRLが抵抗の場合の時のみしか使えませんが、オシロが無くても最適バイアスに調整出来ます。 もし、RLがコイルの場合、アナログ信号を入力から加え、コレクタ端子をオシロでモニターし、上下が均等にクリップするようにR1を決めます。 高周波回路では可変抵抗器をリード線経由で接続すると条件が異なってきますので、この時の誤差を最少にする為、ベースのすぐ近くに予想される抵抗の1/3くらいの固定抵抗を入れ、これにシリーズに可変抵抗器をつなぎます。 調整完了後、固定抵抗と可変抵抗の合計抵抗をテスターで測り、固定抵抗に置き換えます。

E12シリーズ抵抗:1 1.2 1.5 1.8 2.2 2.7 3.3 3.9 4.7 5.6 6.8 8.2 の数値をベースとする抵抗値。この数値で1Ωから10MΩくらいまで量産されている。

回路がエミフォロの場合、VCC=VCですからVEがVCCの1/2になるようにR1を選べばOKです。 回路によってはR2が無い時もありますが、やり方は同じです。

回路例と同じトランジスタやhfeランクが手持ちしていないとき、または、RLやR3を変更したい時便利です。 VCの値は厳密にやる必要は無く、とりあえずVCCの1/2程度に設定した後、VEを測り、その分だけ若干補正する程度でOKです。 このようにして設定したバイアス状態は温度変化に対してかなり安定に動作します。

余談ですが、この回路の低周波(100KHzくらいまで)ゲインは簡略的にRL/R3で求まります。 ただし、R3が数十Ω以上でC3が無い場合です。 また、最大ゲインはhfeに関係なく30dB以下です。

周波数可変は10KΩの可変抵抗で行いますが、CWモードでSメーター最大ポイントに周波数を固定しようとすると、270度回転の可変抵抗器では、かなりクリチカルです。 そこで、この可変抵抗器を3回転(1080度)のヘリポットに変更しました。 これでかなりスムースに周波数設定が出来ます。 周波数カウンターを付ける予定でしたが、発振出力を引き回しますと、隣接周波数のノイズフロアーが増える現象が発生しますので、周波数カウンターは無しで、昔のVFOチューニングと同じように、受信中にVXOのみONして、相手局にゼロビートする周波数に合わせるか、CWモードでSメーター最大ポイントにチューニングします。

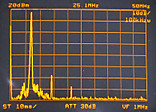

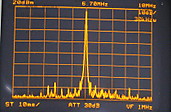

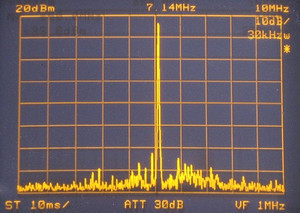

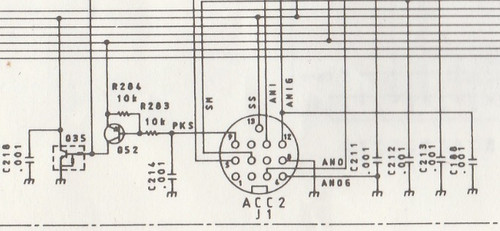

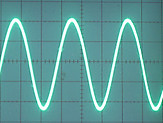

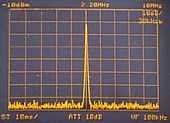

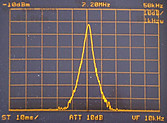

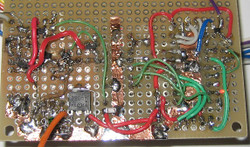

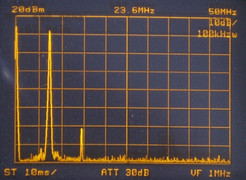

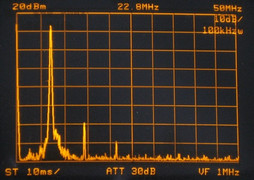

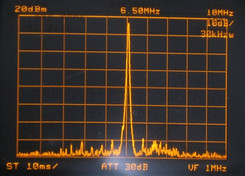

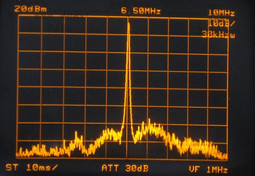

左上は改造したVXO回路、真ん中は7170KHz40W時のスプリアスデータです。一番右は、10MHzスパンの近傍不要輻射データです。 変調をかけてもきれいな音をしています。

全体の回路図 AMTX_PP3.pdfをダウンロード

2016年8月13日追記

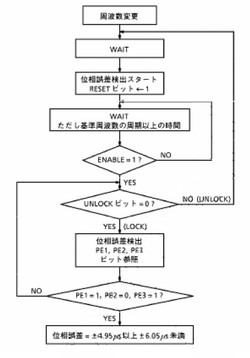

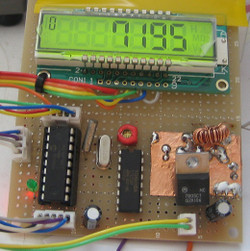

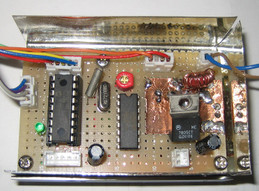

送信周波数を受信機を使って合わせるキャリブレーションは使いにくい為、強引に周波数カウンターを追加しました。 しかし、40W送信時に プリアンプにE級アンプのスプリアスが混入し、カウンターが正常にカウントしません。 VXO回路と周波数カウンター回路を完全シールドしないと使い物にならないようです。 この送信機はオープン構造でシールドは無理ですので、送信時は周波数カウントを停止させ、キャリブレーション時の周波数を保持する事にしました。 受信時もVXOは停止していますので、この時もキャリブレーション時の周波数表示を保持させます。 これをやる事で、カウンターにはつきものの、最下位桁のチラツキも無くなりました。 PICは40W出力時でも誤動作無く動いています。

左のスペクトルは、周波数カウンター付で、送信状態にしたものです。 不要輻射はカウンターが無いときより若干増加しますが、一応スペック内ですので、良しとしました。 上はLCD基板と一体化したカウンター回路です。

使用した周波数カウンターの配線図 VXO_Counter.pdfをダウンロード

周波数カウンターのソースファイル TX_Fcounter.cをダウンロード

7MHz E級アンプ QRO計画 1 に続く。