HDSDR用ダイレクトコンバージョントランシーバー改訂版

カテゴリ<SDR>

LOのキャリア漏れが経時変化で3日も持たないという問題に遭遇し、一時、諦めていたダイレクトコンバージョントランシーバーでしたが、既存のICミキサーを使い構成したIQミキサーの予備検討で、うまくいきそうな感触をつかみましたので、今までのSoftrockコピー品とは異なる、HDSDR用の直交復調器、および直交変調器を作成し、実用可能なSDR SSBトランシーバーの制作に再トライです。

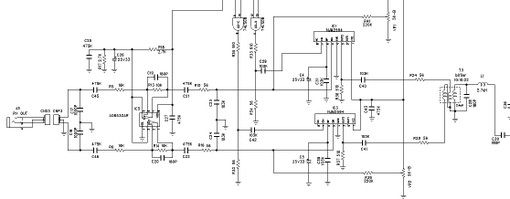

まず、LOの漏れで失敗したQSE回路は止め、ギルバートセル回路をIC化したダブルバランスモジュレーターNJM2594を2個用意し、これでIQミキサーを構成する事にします。 このミキサーは無調整でキャリア漏れを-40dBくらいに抑える事ができ、マニュアルのバランス調整回路を追加する事により-60dB程度まで実現出来る可能性を秘めています。 問題は、2個のICで構成したIQミキサーが、直交変調器として動作するかどうかですが、これは、回路実装が終わってから、確かめる事にします。

また、チューナーの検討の途中で、90度位相の異なるキャリアの高調波成分を抑えると、受信時のノイズが10dBほど少なくなるという現象がありましたので、SoftrockのQSD回路ではなく、高速アナログSWとフィルタリングしたLOを加える事により、受信S/Nの改善を期待する回路に変更する事にします。

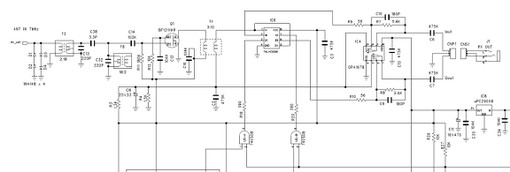

上の回路図は、S/Nを改善する為に、IQ復調回路を2G66に戻し、キャリアの高調波を少なくする為にシリーズ抵抗によるLPFを追加した回路です。 2G66の入力端子には、数PFの容量がありますので、このCとシリーズのRによりRC LPF が出来ています。

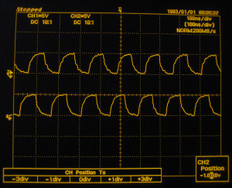

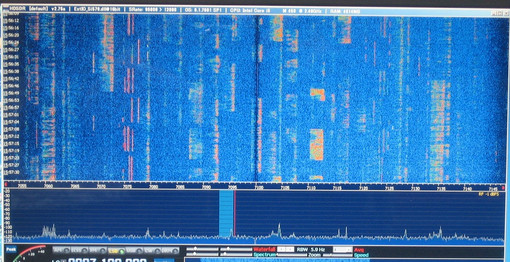

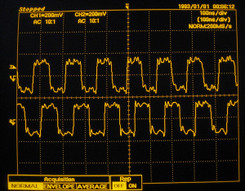

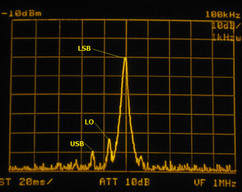

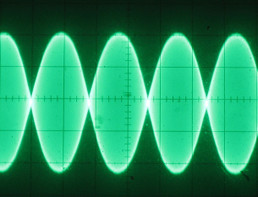

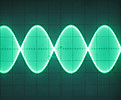

左上は、途中までマウント完了した90度位相の異なるIQキャリア発生部分と受信回路です。 このIQ復調回路に加えるキャリア(LO)の波形が右上でかなり高域をカットしました。 そして、この状態で7MHzを受信したのが、下のスペクトルです。

ノイズレベルが-120dB付近にあります。 この日あまりコンディションが良くなく、TS930のSメーターでも一番強い局がS9くらいでしたので、従来よりかなりS/Nが良くなったのではないかとと期待しています。 このIQ復調回路に、2G66という高速アナログSWを使いましたが、74HC4066でも問題なく動作するはずです。

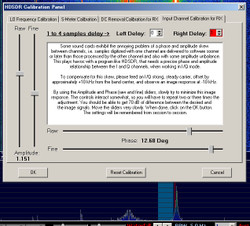

左のスナップは、これらの回路条件で、HDSDRの受信IQバランスの設定状態です。 Right Delayのレベルが赤色に変わるほど、バランスレベルが狂っていました。 この原因は、ノイズを削減する為に、LO供給回路にLPFを入れ、高調波を小さくしたことにより、I及びQのキャリアのレベルや位相がかなりずれてしまい、それをHDSDRの調整機能でカバーした事によります。 USB信号のリジェクションレベルは-50dBくらいです。 アナログ回路にかなりの誤差が有っても、それをカバー出来るだけの広範囲のバランス調整機能が実装されているのは有難い事です。 このRight Delayのレベルは、その後の再調整にて、赤色が消える状態で、調整可能になっています。

以下、その後の感想です。

100Wのリニアアンプが完成し、総通の許可も降り、いざQSO出来る体制ができると、受信機の性能の悪さが大変気になります。 バンドスコープでS/Nが10dBくらいのLSBを聞いても、R3です。 同じ信号をTS-930で聞くとR5です。 ダイレクトコンバーションのRXは聴感上の了解度ははなはだ悪いというのが実感できます。これを少しでも改善する為には、HDSDRをインストールしたPCにつながったサウンドカードを最低のサンプリングレートに設定する事のようです。

一方、送信用のIQ変調回路は、NJM2594によるかなりシンプルな回路とします。 その回路図を下に示します。

ギルバートセルで構成されたNJM2594は、SoftrockのQSE回路程ではないにしろ、通常のAMPより低インピーダンスで動作し、IQ信号の入力インピーダンスは600オームくらいしかなく、その前にあるバッファーのOPアンプは低出力インピーダンスが要求されますので、秋月で手配したAD8532ARをそのまま使います。ただし、SoftlockではIC2個使っていましたが、この回路では1個でOKです。 その代わり、変調回路のICが2個使いになります。

ギルバートセルで構成されたNJM2594は、SoftrockのQSE回路程ではないにしろ、通常のAMPより低インピーダンスで動作し、IQ信号の入力インピーダンスは600オームくらいしかなく、その前にあるバッファーのOPアンプは低出力インピーダンスが要求されますので、秋月で手配したAD8532ARをそのまま使います。ただし、SoftlockではIC2個使っていましたが、この回路では1個でOKです。 その代わり、変調回路のICが2個使いになります。

この変調用ICの応用例では、キャリアも信号も1MHz以上のRFとして説明していますので、今回のように、信号が低周波の場合、周辺のコンデンサの容量を低周波用に修正しておく必要があります。 また、Softrockで有った、キャリアの位相を調整する為のトリーマーは付けておりません。 それぞれのICでキャリア漏れを無視できるまで、減衰できたら、位相を合わせてキャンセルさせる必要はないというのが理由です。

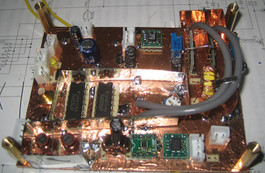

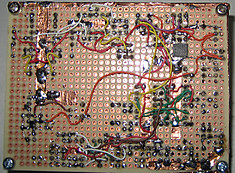

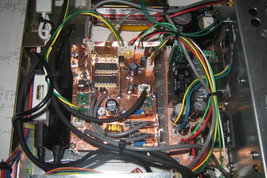

このようにして組んだ回路の全体が下の写真になります。

この基板を組むのは2回目となりますので、先に部品配置を検討することができ、かなりすっきりした配置となり、かつ、念のため、各ブロックをシールド板で囲みました。さらに、変調回路へのキャリア注入は、LO回路から同軸で結すんでおります。

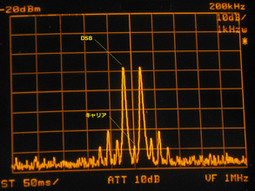

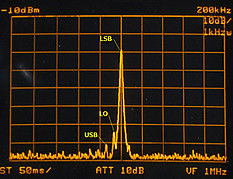

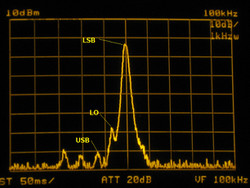

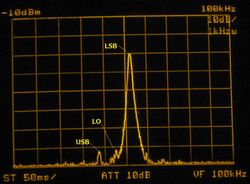

左上が変調ICのキャリア入力波形で300mVppくらいあります。 高調波が多いですが、変調後段にはいくつもの7MHz共振回路がありますので、問題になりません。 右上は、この回路の最終段におけるDSB信号のスペクトルです。 信号周波数は8KHzですが、まだ、IQ信号を加えていませんので、USB、LSB両方の信号が出ております。大きな信号のセンターに少し出ている信号がLO漏れです。LO漏れキャンセル回路は無調整ですが、すでに-40dBくらいのキャリア漏れに抑えられていますので、完成状態で調整することにより-50dBくらいは確保できるのではないかと期待が持てます。

受信のRFアンプにデュアルゲートのFET BF1211WRを使っていますが、この便利なFETは廃番となり、入手が難しいので、東芝の3SK293による回路例も示しておきます。 また、変調回路の+Bラインに6.3V2200uFのデカップリングコンデンサが付いていますが、これはたまたま手持ちが無かったので使っているもので、100uFもあれば十分です。

左上は、IQ変調回路基板を入れ替え完了した状態です。 右上は、NJM2594のキャリア漏れキャンセル回路を調整し、かつ、HDSDR内のIQバランスを調整した状態です。 キャリア漏れは-45dBくらい、USB漏れは-52dBくらいになっています。 この状態で、電源を切り、1日放置した後、再測定してみる事にします。

左上が15時間くらい経過した、朝のテスト結果です。右上は、同じ出力条件での2信号特性です。 とりあえず、半日くらいは問題ないようです。 この後、ドライヤーで温めてみましたが、大きな変化はありませんでした。

左上は、5日後のキャリア漏れとUSB漏れです。前回とほとんど変化はなく、期待した通りの状態を維持しております。 右上は、LO漏れを最小にすべくNJM2594に設けた半固定抵抗を微調整したもので、キャリア漏れは-51dBくらいになりました。 このキャリア漏れを再調整した事によりUSBイメージが若干悪くなりましたが、HDSDR側のキャンセル機能でノイズ以下にする事ができます。 また、出力アップ時のスプリアスは、LOとTUNEのOFF SETをゼロにしますので、許容範囲に収まります。

今後さらに確認を継続しますが、何とか使える見込みができましたので、一旦中止した100Wリニアアンプの製作を再開することにします。

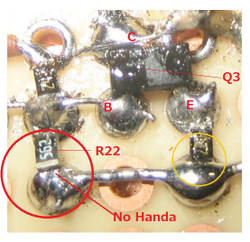

この基板のチップコンデンサの電極断線が3か所も発生し、まともに動作させるまで半日かかってしまいました。 また、トランジスタのコレクタの半田不良により、送信ができなくなるトラブルも発生しました。 左の画像で赤丸の部分ですが、写真で見る限り、半田付けされていません。 しかし、機械的には接触しているようで、動作上は、異常はありませんでした。100Wリニアアンプ検討中に、出力が出なくなるという問題に遭遇し、困っていましたが、その原因がこれでした。 回路が熱を帯びると、膨張の為、接触しなくなり、ベースバイアス電流が狂うという症状で問題が現れました。

チップ部品の半田付けは見た目以上に難しいですね。

リニアアンプにつなぐ為、出力のリニアリティをチェックしました。

左から、出力 3Wpep 4Wpep 5Wpep 6Wpepです。4Wpepまでは、リニアリティの悪化は少ないようですが、5Wpepあたりから、見える形で飽和がが始まっており、6Wpepでは、はっきりと飽和が認められます。 100Wのリニアアンプを最適に使うためには、5Wの出力のとき、70Wくらい出るのが理想かも知れません。

100Wリニアアンプと結合したとき、送信状態から受信に切り替わる場合、リニアアンプが受信になるまで、1秒以上の遅れが有りました。 その対策として、フォトカプラーのLED側に抵抗を追加しました。

LED消灯対策済み 7MHz_SDR2.pdfをダウンロード

100Wリニアアンプの制作に続く。