高効率E級アンプ再トライ

<カテゴリ AM送信機(デジタル方式) >

E級AMPを製作するつもりでしたが、出来上がったのはD級アンプでした。

実験中に次々とFETが死んでいくBS170 6石によるE級アンプを諦めて、せめて、効率が70%を切っても、壊れないPd 20WクラスのFETによる2石プッシュプル回路を検討する事にしました。

パーツBOXの中で見つけたのが2SK2925。 Pd=20WですがCiss=350PFとBS170x3より6倍近く大きく、もう74HC04ではドライブ出来ません。 そこで、7MHzの200W PWM機で使った、FETをタスキがけにして、振幅を2倍にする回路で実験しました。 しかし、たすき掛けに必要なのは、FETのゲートを完全にON出来る電圧であり、その電圧を確保しようとすると、終段のゲート入力インピーダンスが低い事もあり、結構大きなドライブ電力が必要です。 この電力は0.5Wくらいであり、小信号トランジスタではドライブしきれません。 実験の途中で、FETのたすき掛けを諦め、ダイオードクランプによるレベルシフトにより、ゲートをフル振幅でドライブする回路に変更しました。

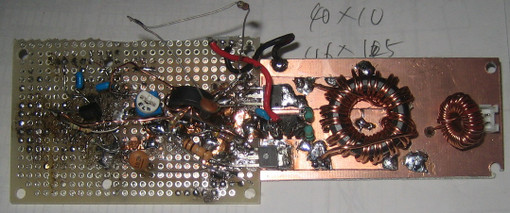

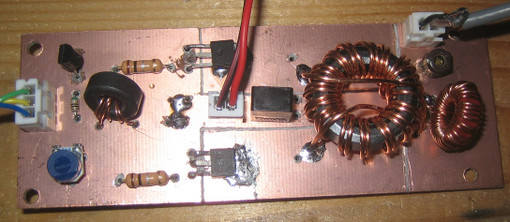

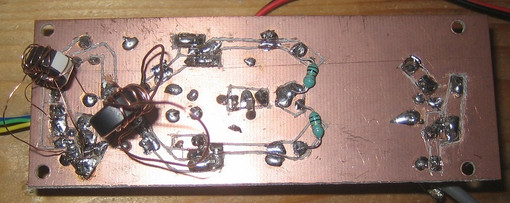

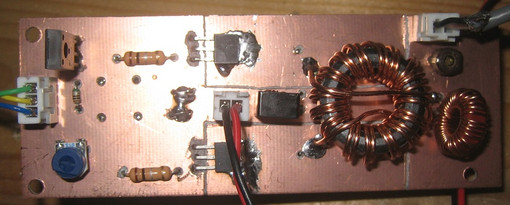

上の実装基板は、回路の基礎検討を行った時のもので、12Vの電源で、9Wの出力が得られ、効率も80%くらいになりましたので、 KiCADで作図した基板図をベースに1枚だけ基板を手作りしたのが、下の基板になります。 終段のFETのドレインは45mmx15mmの銅箔に張り付けて放熱板としてあります。

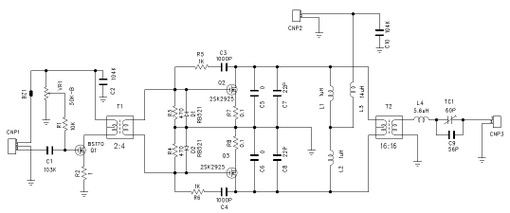

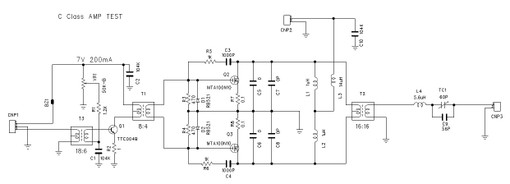

上の回路がその全回路図です。 2SK2925のCossは190PF有り、この容量と両面基板の浮遊容量でE級アンプに必要な共振コンデンサは形成されていますので、C7,8は最終的には0PFとなりました。

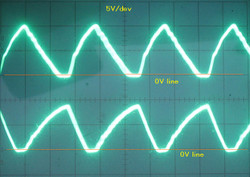

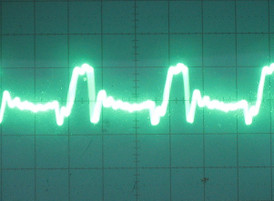

左の波形がQ2,Q3のゲート電圧の波形となります。 ダイオードクランプのおかげで、約10Vppの電圧で、終段のFETをドライブできます。

当初、初段のBS170のVddを12Vに設定していたのですが、200mAくらい流さないと正常にドライブ出来ず、1分くらいの動作であえなく死んでしまいましたので、Vddを7Vまで下げ、200mA流すと、なんとかE級アンプとして動作するようになりました。 ただし、この状態でもPdcは1.4W有り、効率が50%としても700mWのPdですから、通常運用では壊れるのは時間の問題です。 このBS170をほかのFETに変更しようにも、Ciss=20PFというFETはこれ以外になく、放熱板なしで1.5Wくらいの実力のあるTRに変更するしかなさそうです。

そのTRをさがしている間に、ファイナルの効率を調べる事にします。

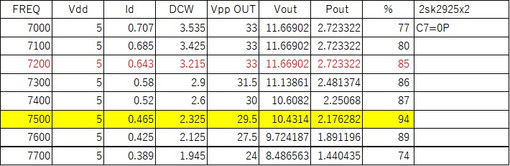

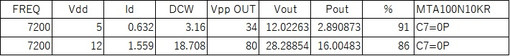

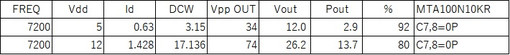

まず、C7,8が0PFと置いて、周波数を変えた時のデータです。 Vddは5Vです。

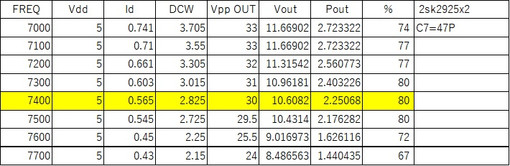

目標の7200KHzで85%。最高94%が得られる周波数は7500KHzでした。 そこで、C7,8を47PFに変更してみたのが下のデータです。

7400KHz付近で80%の最高効率となっており、ここは、C7,8ではなく、L1,2を変更しないとダメなようですが、あいにくL1,2は1uHの固定インダクタでいじれません。

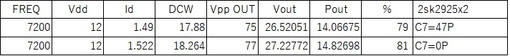

次に実際に動作させるVdd=12Vで比較してみました。

12Vの場合、C7,8は0PFの時が効率はいいみたいです。

終段に使った2SK2925は秋月で90円/石です。 もう少し安いのがないかと物色していると、MTA100N10KRI3というFETが25円/石で見つかりました。 ただし、Cissが425Pもありますので、今度は初段のドライブ能力が問題になりそうです。 そして、BS170の代替TRとともに、このFETを発注しましたので、入手出来たら、確かめる事にします。

8月19日

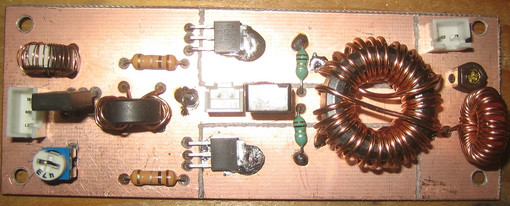

手配していたトランジスターとFETが届きました。早速、組み換えです。 初段のトランジスターはTTC004BというPc=10W、ft=100MHzの東芝製です。 最初、入力トランス無しでトライしたのですが、ゲインがさっぱりでしたので、 18:6のトランスに変更したところ、Ic=40mAで終段のゲートを10Vppでドライブできるようになりました。 このときのDC入力は0.24Wで、効率1%でも放熱板なしで動作可能です。

終段のFETはケース温度100度のときPd=12WというMTA100N10Kですが、これも2SK2925より効率が良くなっています。

回路図は以下のようになりました。

以下、トランジスターとFETを変更した検討時点での基板の表(SMD面)と裏(部品挿入面)です。

T3のコアはESD-R-10Eですが、18Tで148uHでした。 これは、同等のインダクタンスが得られる他のコアでも代用する事にします。 T1のコアは以前SWR計のCM結合器に使用されていたものですが、4Tで5.7uHのインダクタンスとなりましたのでアミドンの#43系と同等のコアと思われます。

そして、5Vと12V時の全体の出力と効率は以下のようになりました。

12V電源でも86%の効率を確保でき、初段のトランジスターも終段のFETも指でずっと触っていられるくらいしか発熱しません。

次は、この回路を再度プリント基板図に落とし、量産前の最終確認を行います。

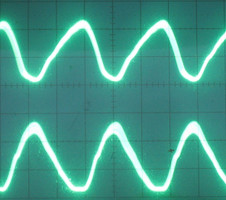

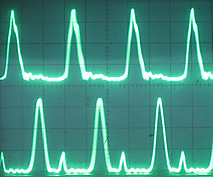

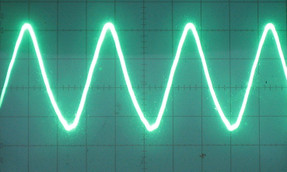

これらの波形は、左上が、この基板の入力コネクタの位置での7200KHz信号です。終段に12Vを加えていますので、リンギングが目立ちます。 右上は、Q1で増幅した後の、終段FETゲートドライブ信号で、終段のドレインには電源電圧がかかっていない状態です。 ちなみに、電源のDC12Vが印加されると、リンギングによりギザギザになります。 左下は、終段のドレイン電圧波形です。 E級アンプのつもりで製作してきましたが、動作はD級アンプで有る事が判りました。 右下は、この基板の出力となる50Ωダミー抵抗両端の波形です。 完全な正弦波ではありませんので、電力合成時に問題がでないか心配です。

そして、このNo.1 基板によるデータは以下のようになりました。

最初に試作した回路より若干効率が落ちましたが、この状態で安定するかどうかは今後の台数確認にかかっております。

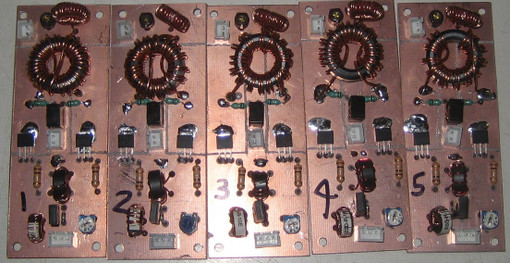

当初、プリント基板を外注しようと考えていましたが、ICを使用する必要が無くなった事から、12台、全部、手作り基板で行く事にし、たちまち、部品を確保済みの5台分を作成する事にします。 プリント基板の作成は、KiCADで4枚に面付したパターン図をインクジェットプリンターで印刷した後、これを両面テープで生基板に張り付け、最初にボール盤で穴あけを行い、次に外径線に沿って、カッターでケガキ線をいれます。 ケガキ線を表裏とも各20回くらい入れた後、自作のアルミベンダーに差し込み、折り曲げると、綺麗に折れます。 その後、パターンのエッジに1本のケガキ線を入れ、直径1mmくらいの棒状ビットを付けたルューターで、銅箔を削りテスターで完全に切り離された事を確認したら、最後に、直径1mmくらいの球状ビットでこの銅箔カット溝を広げれば出来上がりです。 両面基板の部品挿入面側の銅箔で部品の足がショートしないように、予め、6φくらいのドリルで銅箔を削っておけば楽勝です。

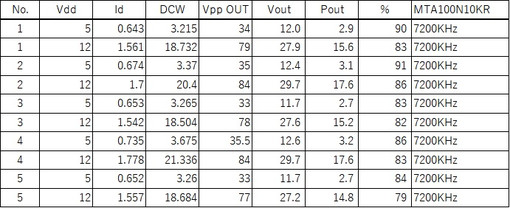

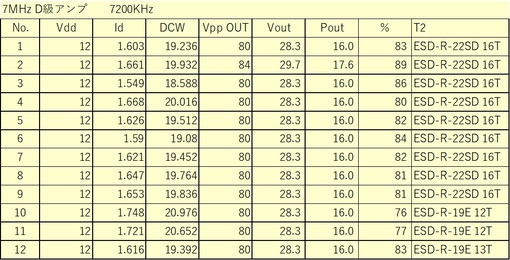

5台のAMP Unitが完成しました。 そして、改めて、各unitを最大出力状態に調整した時のデータは以下のようになりました。

実際に使う12V電源に於いては、出力が最大17.6W、最小14.4W、効率最大86%、最小効率79%です。 各Unitの出力は初段のバイアス電流で調整できますので、直列合成Unitとして使う時は、最小出力のUnitに合わせ込んで、動作させる事になります。

上の表は、4台のアンプをLSB側合成回路に使用した時のデータです。 計算値に対して、かなり少ない誤差で出力出来ており、もう微調整の範囲です。 ここまでできると、自信をもって残り7台のアンプを製作する事にします。

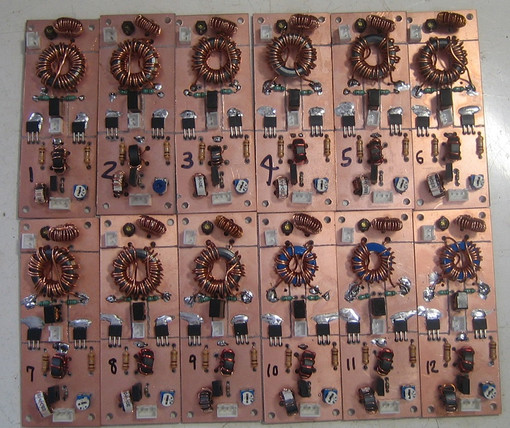

9月の上旬後半ですが、12台のアンプができあがりました。 途中でT2のコアが手配できず、ワンランク下のESD-R-19Eで代用しましたので、このサイズダウンしたコアを使ったアンプは効率も落ちました。 これらはLSB側の小電力用に使えば問題有りませんので、このまま進行します。

出来上がった12台のアンプとそのデータです。

この12台のアンプをRF DAコンバーターとしてAM送信機にまとめていく訳ですが、電力合成回路の製作を行う前に、アナログの音声をデジタルに変換する為に、dsPIC33FJを使った回路を製作必要です。 そして、このdsPICを制御し、送信機として必要な機能をPIC24Fのマイコンで実現すべく、その検討を開始します。

実際に電力合成回路を作成し、12台のアンプによる電力合成を行った結果、合成出力が極端に小さくなり、1Wも出ませんでした。

この原因はパワーアンプ単体の出力が歪んでおり、フェライトコアによるトランスの2次側で、基本波の大部分が第3高調波成分に変わる事のようです。 再検討が必要となりました。

このパワーアンプは、特定の基板で、終段FETが何回も破壊すると言う問題点が見つかり、最終的に没となりました。