DDS VFOの製作 (AD9833)

<カテゴリー:DDS>

アマゾンで安い中華製のAD9833ユニットを見つけ、HF送信機のVFOに使えないか事前検討をした結果、そこそこ使えるめどが立ちましたので、CW、AM送信機の外部VFOに仕上げる事にしました。

回路構成は、DDS VFOの実験の経緯から、16bit PICマイコンと、中華製基板をそのまま使って、パスコンの移動と、SPXOの電源を独立した回路を基本とし、10Hzスパンで1回転96パルスのロータリーエンコーダーと、1KHzスパンで1回転24パルスのサブエンコーダーによる周波数可変手段を持った1.8MHzから50MHzまでのハムバンドをカバーするVFOとします。

まずは、回路図です。

DDS VFO の回路図 DDS_multi_VFO180309.pdfをダウンロード

DDSはAD9833、 コントローラーはPIC24FV32KA302、LCDは新規に手配した16x2のパラレルドライブです。 25MHzのSPXOの電源を専用の3端子レギュレーターからドライブし、マイコンやDDSのデジタル回路電源から侵入するノイズを遮断しました。 また、DDSの3番ピンからAGNDへ落ちるパスコンC1は4番ピンへ最短で接続し直しています。 PICマイコンは、前回の実験で使用したものをそのまま使用しますが、前回の実験中に3端子レギュレーターが壊れた際、破壊されたRA0,RA1,RB0のI/Oは使用不能となっていますので、増加したLCDドライブ用端子を含め再配置しています。

LCDは4bitパラレル駆動ですので、RB4~RB7へ割り付け、同一ポートの他の端子に影響が出ないようソフト面で配慮しました。

ロータリーエンコーダーは10Hzステップと1KHzステップを用意し、バンドによってはステップ数を変更しています。 バンドは1.8MHzから50MHzまでの10バンドですが、このセレクタとしてロータリーエンコーダーを使っていますので、IF周波数を考慮したオフセット周波数のバンドが増加しても、ソフト対応のみで、最大63バンドまで確保できるようになっています。

最高周波数を8MHzくらいと置きましたので、50MHzの場合、8逓倍必要です。 少しでも周波数の分解能を上げる為、周波数指定は0.1Hz単位とし、DDSのレジスターに書き込む場合の乗数kdは一桁落とし、1.073741824を使っています。 LCDへ周波数表示する場合、1/10してから表示します。

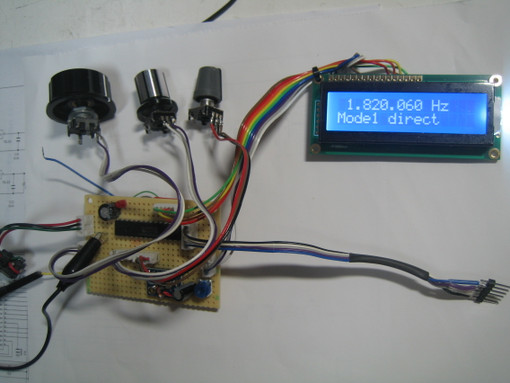

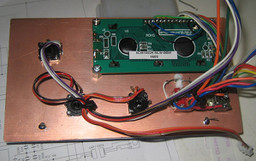

上の写真はバラック状態の全回路です。

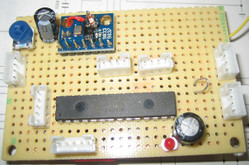

左上が基板の表側、右上がチップ部品装着面です。 私の基板は日圧のコネクターを多用しますが、ほとんどが、2mmピッチのPHタイプです。蛇の目基板の2.54ピッチと合わないので、ドリルで2mmピッチの穴を明け直して実装しています。 最近、秋月で2.54x2mmの基板が発売されるようになりましたので、今後、この基板を採用する機会が増えそうです。

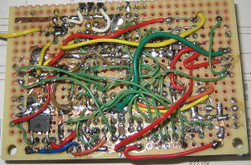

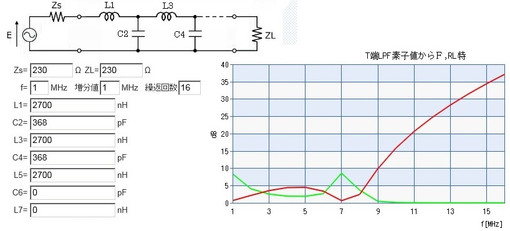

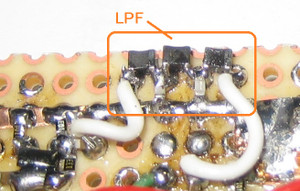

DDSの出力の後にポストアンプと5次のLPFを実装してあります。 LPFは8MHzくらいをターンオーバーとするLPFですが、特性から算出した定数の場合、要求される値の部品を手持ちしていない事が普通です。 そこで、手持ち部品から特性を計算させ、そこそこの特性が得られるように定数を吟味するソフトを探したところ、以下のURLが見つかりました。

4.5MHz付近で5dB近く減衰が増えていますが、ちょうどDDSのDAC出力もこの付近の周波数から、周波数が高くなるほど、減衰していますので、出てくる出力は補正され、フラットに近くなっています。

このLPFを実際に構成した状態は、左の写真に示すように3個のチップコイルと2個のコンデンサです。実際の回路ではコンデンサが368PFという特殊値ですから、それぞれ3個のコンデンサを積み上げて作っています。 基板の占有面積は7.5mm x 5mmくらいで、ちゃんと使える特性を得ています。使ったコイルは太陽誘電製のLBM2016という型番のチップインダクタです。(RSでMOQ (Minimum Order Quantity) 25の条件で1個13円)

基本動作はOKとなっていますので、これから、ケースに収納する事にします。

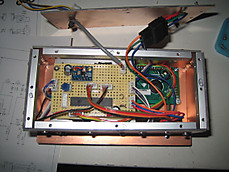

ケースは生両面基板で箱を作りシールド構造とし、AM送信機が200Wフルパワーでも、異常が起きないようにします。

プリント基板の板を互いにハンダ付けして四角い箱を作るわけですが、メンテの為、箱の裏板はビスで止め取り外しができるようにします。

左上はbox内の配線状況、上の方に裏板が見えます。この裏板でboxに蓋をした状態が右上です。VFO出力は左中央の小さな同軸コネクタから取り出します。右中央のコネクタは電源とTX側からのstand-by処理をするコネクタです。

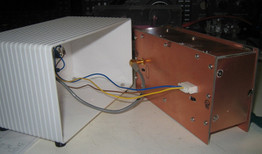

シールドboxからケースの端子へコネクタで配線とケース後側の端子類です。DC Jackとスタンバイ用Jack及びRF出力用のBNC端子です。

全体を100円ショップのプラスチックケースに収納した状態です。 見栄えを確保する為、インクジェットプリンターでレタリングをフォト印刷紙へ印刷し、フロントパネルの両面基板に貼り付けてあります。

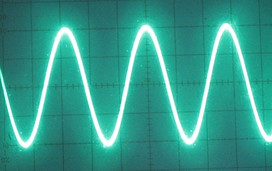

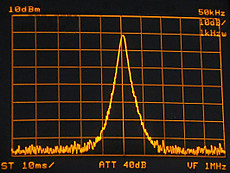

この状態での信号出力波形とそのスペクトルは下の写真の通りです。 第2高調波レベルは-30dBくらいですが、これは特に問題は有りません。

信号純度に関係するスペクトルですが、今までのDDS実験記事で紹介したどれよりもきれいに見えます。 そして、実際のビート音も、CW送信機でも使用できるレベルです。

最終配線図DDS_multi_VFO180406.pdfをダウンロード

ラスト周波数メモリー付のソースリスト DDS_multi_VFO_ACM1602K.cをダウンロード

CALスイッチがONの時、LCDで表示された周波数の信号が出力され、OFFの場合は出力なしとなります。 LCD表示は、送信の時も受信の時も常時周波数を表示していますが、送信及びCALオンの時だけDDSが指定周波数の信号を発生させ、受信時は周波数が0Hz(信号なし)となります。

DDS VFO 逓倍回路付(1.8MHz - 50MHz) へ続く

キャリア周波数+/-500KHzのスプリアスを未確認でした。 これを確認した結果、AD9833を使ったDDS VFOとPLL逓倍ICを使ったVFOは送信機には使えない事が判りました。