dsPICでSSBトランシーバー(製作開始)

カテゴリ<SDR>

dsPICの、基本機能が完成しましたので、トランシーバー全体の構成を、システムコントローラーとDSPがメインのデジタルブロックと、アナログブロックのふたつに分割した回路基板として製作を開始する事にします。

システムコントローラーの役目は、送受信周波数の選択とモード設定、送受信切り替え、その他付属機能をマイコンで実現するものです。

この回路の範囲は、dsPICによるSSBジェネレーターを中心に、システムコントロールマイコン、LCD表示部、受信時のオーディオ増幅部及びAGC制御回路から構成され、トランシーバーとしてのすべてのコントロール機能を受け持ちます。対応するのはPIC16F1938 8bitマイコンです。

HDSDR用のダイレクトコンバージョントランシーバーに使った同じLCDを使いますが、このLCDに使用されているICのスペックを詳細に調べたところ、LCDは5V電源でないと動きませんが、これを制御するマイコンは3.3Vでも、正常にH/Lの制御ができる事が判りました。ただし、条件があり、LCD側へマイコンからの一方通行の制御に限られますが、LCDからの読出しは行わないので、問題なしです。

dsPIC33Fのi/oをPIC16Fメインマイコンで制御する訳ですが、片方のPICへPICKit3を接続しただけのとき、及び、メインマイコンからdsPICへResetをかけたときなど、二つのマイコンのI/Oの状態が不明の為、Lの出力端子にHの電圧が接続され過大電流が流れるのを防止する目的で、必要な端子には、通常動作で邪魔にならない程度のシリーズ抵抗を挿入し、保護してあります。 最初、この保護なしで接続した為、配線ミスも加わり、RC1の入力回路を壊してしまい、その反省からです。 従い、当初RC1に設定してあった、PTT入力は、RC5に移しました。

dsPICの出力は、DACLが受信時のオーディオ出力で、ボリュームを経由してスピーカーを鳴らします。 DACRは送信時の出力で、9.8KHzのサブキャリアで変調された信号を、次段の24MHzミキサーへ出力します。 こうする事により、アナログSWを1回路省略できます。

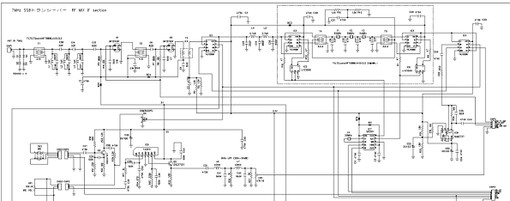

一方、アナログ回路は、RF回路、クリスタルフィルターを挟んだ、ふたつのミキサー回路、およびマイクアンプ、送信用バッファアンプ等で構成し、下の回路図のようにまとめました。

この回路を構成するフィルター部分はブロックとして作成し、簡単な特性のチェックも行っています。

24MHzのクリスタルフィルターは前回の記事で取り上げたように、スペアナで実測したものを、左の写真のように組み替えました。 使った4個のフェライトコアはTDK HF70BB 6.4X5X3.2で、巻き数は4:4:8ですが、バイファイラの巻き線仕様はSDR-3と同じです。

受信のRFアンプの先頭に置く7MHzのBPFもブロック化し、あらかじめ、特性を確認してあります。 7MHz LPFはミキサーの前に置くものです。

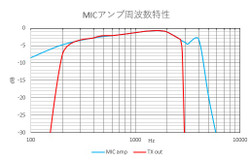

青いコイルは40mHのインダクタですが、マイクアンプの出力に置き、3KHzのLPFを構成させます。このLPFは、この後、ADコンバーターへつながる事になりますが、ADコンバターで発生するエイリアシングを防止する為、エイリアシングが発生始める19.5KHz以上で、-50dB以上の減衰を確保します。 このフィルターとマイクアンプ全体の周波数特性は、左のグラフの青色の線になります。 そして、SSBジェネレーター内のBPFにより、実際に送信される周波数特性は、赤色のグラフになります。 700Hzより1800Hzのレベルを2dBアップさせ、少しでも了解度が向上するように細工しています。

約24MHzのLO2と約17MHzのLO1はdds IC Si5351Aで作ります。 このプログラムは、以前HDSDR用のダイレクトコンバージョントランシーバー用として作った事がありましたので、それをアレンジして、可変のLO1と固定のLO2を同時に発生させています。 この出力をそれぞれ、位相反転させ、高速アナログSW 2G66をスィッチングし、ダブルバランスドミキサーを構成しました。

ここまでの回路図には、まだリニアアンプは含まれていません。

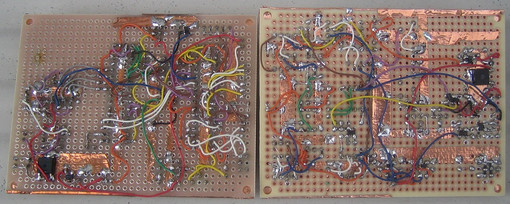

そして、この回路図状態で、配線完了した2枚の基板が以下です。

まだ、配線が完了しただけで、配線チェックも、通電テストもやっていませんが、まず、システムマイコンを動作状態にし、DSP部分、LO、ミキサー部と、順にチェックとカット&トライを繰り返しながら仕上げていく事にします。

そのシステムマイコンの動作確認を行いました。 かなりの配線ミスや、配線図自身の間違いがありましたが、とりあえず、動き出しました。

左は、LCDとロータリーエンコーダーを接続して、動作チェック中のシステムマイコンです。 周波数表示とモード表示、RIT表示、Sメーターの数値による表示など、機能しております。

左は、LCDとロータリーエンコーダーを接続して、動作チェック中のシステムマイコンです。 周波数表示とモード表示、RIT表示、Sメーターの数値による表示など、機能しております。

今後、DSP部分、Si5351AによるLO回路、ミキサー回路、MICアンプなどの動作確認を少しずつ進めていく事にします。 すべての回路機能を確認できるまでは、仮のシャーシとパネルを用意し、回路の改修が簡単にできるようにしておき、完成した時点で、どのようなケースに収めるか考える事にします。

木製の板の側面にアルミ板をねじ止めし、仮組の回路ができましたので、dsPICとSi5351Aが正常に動作できるまで確認できました。 回路図の間違いもありますが、それ以上にコネクタの1番ピンの位置が間違っているのが多いです。 幸い、基板から煙が出るほどではありませんでしたが、この間違いを修正するのは、一度挿入したコネクタのリード線を引っこ抜き、正しい順序に挿入しなおすだけなので、手間はかかりませんでした。

DDSのSi5351Aの発振周波数を周波数カウンターで確認したところ、第2LOの周波数は、24006766Hzでないとダメなところが、24006416Hzとなっていました。 そこで、ソフトの中で定義した SI5351_XTAL_FREQを 24999633Hzに修正し、ぴったり一致させました。 この校正で、第1LOの周波数も校正されますので、+/-0.1ppmの周波数誤差で、運用できます。

アナログSWの2G66の半田付けのトラブルや、1番ピンと8番ピンの逆付けなどのトラブルがありましたが、自作のSGを使い、アンテナからスピーカーまでの受信回路に信号を通す事ができました。 日を改めて、7MHzのアンテナに接続して、受信テストです。

最大感度が市販のトランシーバーより悪いですから、雑音の大きさは、断然小さいのですが、とにかく聞きにくいのなんの。

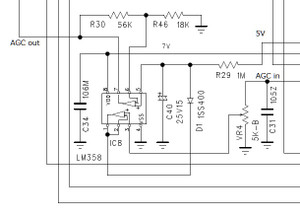

原因はAGCの調整がうまくいっていないようです。 当初、AGCのアタックタイムとリカバリタイム、AGCレベルなど、すべてソフトで対応しようと意気込みましたが、半日でギブアップ。 昔ながらのアナログ回路で作ると、これが、いとも簡単に、TS930レベルの聞きやすさになりました。 左が、そのAGCアンプですが、教科書に出てくる回路と少し違います。通常は、高速に充電して、ゆっくり放電させますが、この回路は逆です。高速に放電して、ゆっくる充電させます。 ICはグランドセンスタイプのLM358ですが、レールtoレールタイプのOP-AMPではないので、出力レベルを5V確保しようとすると、電源電圧は、最低6.5V必要になります。 そこで、78L05の3端子レギュレーターのGND端子にLEDをシリーズに入れ、約1.8V電圧をかさ上げし、6.8Vの電源を作って解決しました。

しばらく、受信テストを行っていると、+40dBくらいの強い局を受信すると、音声のピークで歪ます。 原因を調べると、時定数セット用に導入したダイオード両端の0.6VのVfの為、OP-AMPがフルスイングせず、AGC電圧が2.5V以下にならない事でした。 対策として、OP-AMPにオフセット電圧を加えるようにオフセット調整用の半固定抵抗を追加しました。

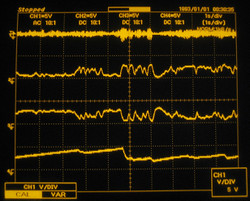

左のデータは、上から順に、dsPICの入力となる第2IFのレベル、その下がdsPICのDA出力、その下が、コントロールマイコンのDA出力です。 dsPICの出力と、コントロールマイコンの出力は、同じアナログ信号ですが、極性が180度ことなります。 そして、一番下が、デュアルゲートFETのG2をコントロールするAGC電圧となります。 このAGC電圧は0Vから5.5Vくらいまでフルスイングできるようになりましたので、実際にSSB信号を聞きながら、一番聞きやすい状態になるよう、オフセット電圧調整用のVR4を調整する事にしました。 このオフセット最適状態で、電源ONすると、音声が出始めるまで5秒以上かかります。 原因は、OP-AMPの電源がONされてから、出力が5Vになるまで、ゆっくりと上昇する事によります。 対策すると大げさな回路追加が必要ですので、そのままです。

トラブル発生です。電源ラインがショートして、5V 3端子レギュレーターがあっちっちです。 最初どこがショートしたのか判らず、焦りましたが、原因はRFアンプのトランスにまかれた、UEW線の被覆が破れ、これが基板に張り付けた銅箔にタッチしたものでした。 このUEW線はルーターで強力によりを入れた為、ウレタン被服に傷がついていたようで、コイルが銅箔に密着したとき、ショートしたみたいです。 対策として、トランスと銅箔の間に絶縁テープを挟み込みました。 これで、強く押し付けてもショートしなくなりました。 最初から、この部分のみ、銅箔をカットしておけば良かったと、後悔しています。

1日中、7MHzのSSBをワッチしてみましたが、HDSDRの時の了解度と、この回路の了解度は、比較にならないほど、この回路が良い事が判りました。 ただ、トータルゲインが不足しますので、ノイズと同等レベルの信号は、音量ボリュームを一ぱいに上げないと良く聞き取れません。しかし、聞こえたら、ちゃんと了解できます。

とりあえず、受信はこれくらいにして、送信の確認に入ります。

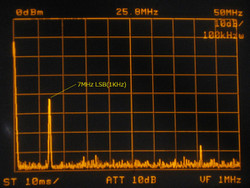

マイクアンプのベースバイアス抵抗を決定し、次の、リミッターアンプの動作確認を行い、LCRの3KHz LPFの実測による定数見直しを行った結果、リミッターが動作した時の最大値は2Vppとなり、これがそのままdsPICのADCへ印加されます。 そして、DSP内部でサブキャリアとMIXされ、第2IF、第1IFを経て、取り出された7MHzのLSB信号が左のスペアナデータです。 外部に20dBのATTが入っていますが、それでも-22dBmくらいの出力レベルが得られました。 この信号をTS930で受信してみると、きれいなSSB信号として復調されます。

送信モードに於いて、dsPICの出力をチェックすると、dsPICの入力の1/4しか有りません。 せめて、入力と出力レベルが同じにする為、DACに入力する前に、データを左シフトを1回行い、データを2倍にして、出力させ、dsPICのDAC出力につながっているOP-AMPで2倍し、元のレベルに戻す事にしました。 これは、受信時でも効果がありますので、受信時の音量不足対策にもなります。

このように、送信ブロックは意外とあっさりと完成してしまいました。

これから、使用頻度を上げていくと、改良事項も出てくると考えますので、出てきたら、アップデートする事にします。

以下の配線図は、いままでの対策を盛り込んだ最新バージョンです。

システムコントローラーとDSPブロック回路図 SSB_generator4.pdfをダウンロード

アナログ部分の配線図 DSP-TRX4.pdfをダウンロード

クリスタルフィルター前後のトランスT4,T5の巻き数が間違っています。 正しくは8:4:4及び4:4:8です。

dsPICのソースファイルです。

コントローラーのソースファイルです。

これらのソースは開発始めたばかりの状態ですから、完成度は低いです。

dsPICでSSBトランシーバー(CW,AMモード追加)へ続く