50MHz AMトランシーバー(パワーアンプ)

カテゴリー<6m AM >

DSP受信機とキャリア生成ユニットが出来たので、パワーアンプの再検討です。 目的は、現行よりサイズダウンして移動用のケースに収める事ですが、ついでに前回までの回路が最適状態なのかを確認し、少しでも改善できないかを検討します。

まずは、ファイナルのメガネコアについてです。

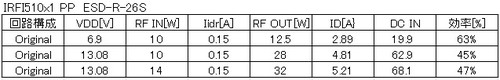

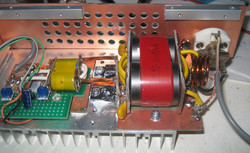

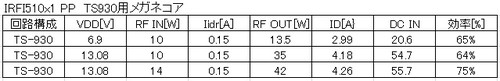

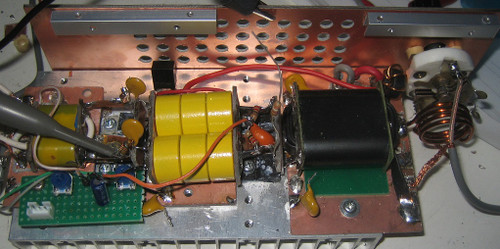

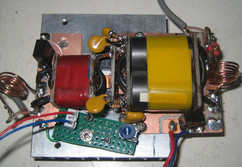

上の表は、従来のコア(ESD-R-26S)を使用した現状の終段のみのデータです。 左は、このデータを得た時の終段の状態です。 すでにオリジナルよりバリコンはサイズダウンし、代わりにコイルは線径と巻き数が増えております。

また、13.8Vの電源を設定するのが面倒なので、今回は13.08Vで測定しています。 前回、13.8V、入力10Wにて31Wとなっていましたが、今回は13.08Vで28Wです。これは電源電圧の差によるもので、前回と大差は有りません。

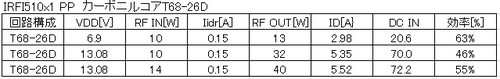

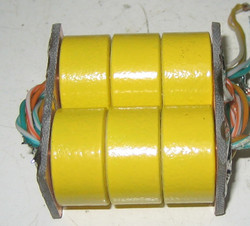

上の表は、左の写真のようにメガネコアをカーボニルコアT68-26D 6個に変更した時のものです。 電源電圧と入力レベルは同じにしています。 それぞれの条件で前回より出力レベルはアップしています。 特に入力14Wの場合の出力レベルに大きな改善が見られます。 また、効率も若干良くなっています。

コア内部の損失が少なく、DC重畳でも磁気飽和に余裕があるコアですが、HFではそのμが小さい事が原因でメガネコアとしては使用できませんでした。 50MHzくらいになると、必要なインピーダンスを確保でき、かつ周波数に比例しますので、あえてこのコアを手配したものです。 コアはアミドン製では無く、中国製のセカンドソースですが、一応カーボニルコアの特性は出ており、共振回路を作ると、それなりのQを確保できるものです。aitendoにて1個50円で販売していました。

上の表は、メガネコアをTS-930Sのファイナルに使用していたものに変更した時のものです。 以前、7MHzの50W AM送信機に使用していました。 出力はカーボニルコアより向上しており、効率も良くなっています。 ただし、送信ONした後、2分間くらいは電流と出力の減少がみられ、この表は通電から20秒以内に取ったデータになります。 2分後には出力が約5%、電流は約10%ダウンします。 カーボニルコアの場合、この減少は有りませんでした。

左の写真はAWG22のリード線による2次巻線ですが、データは、幅4mm、厚さ0.3mmの銅板による2次コイルとなっております。

以上の結果より、この改良アンプの終段メガネコアはTS-930S用で進行する事にします。

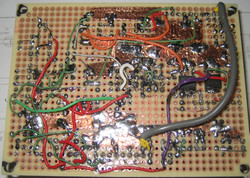

次は前回のファイナル、ドライバー一体のパワーアンプユニットの再検討です。 前回は、異常リンギングにより一体化をあきらめた為、パワーアンプユニットのサイズが大きくなったという反省点がありますので、再度、この一体化アンプについて検討してみました。

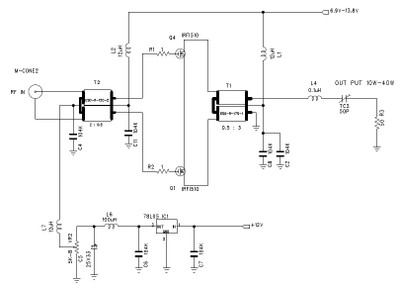

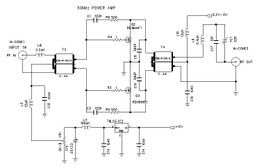

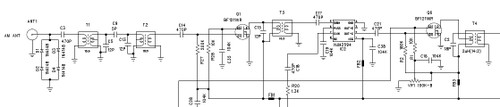

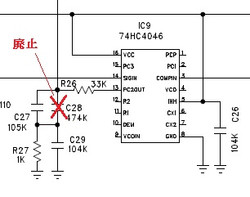

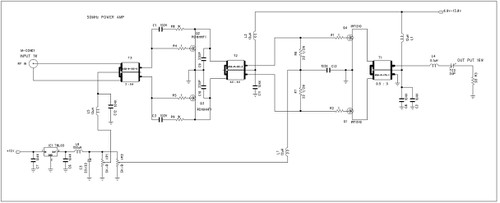

上が、リンギング対策を考慮したダイレクトドライブのパワーアンプ。 下は、その実際の回路です。 リンギング対策は効果的に作用し、リンギングも発振も有りません。

上が、リンギング対策を考慮したダイレクトドライブのパワーアンプ。 下は、その実際の回路です。 リンギング対策は効果的に作用し、リンギングも発振も有りません。

この回路にFT450から1Wのキャリアを入力しても出力は5Wしか出ません。 FT450の出力を5Wや10Wにしても出力は5Wのみです。 ドライバー無しのとき、FT450から10Wでドライブしたとき13Wも出ていたのに。

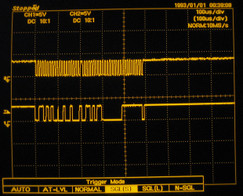

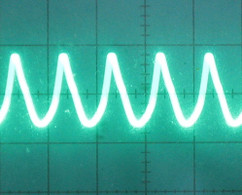

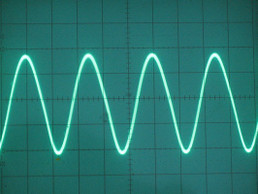

その最大の原因はファイナルのゲートドライブ電圧の波形ではなかろうかと思われます。

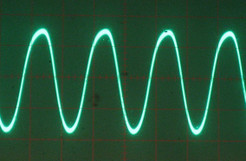

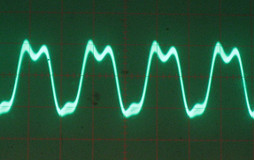

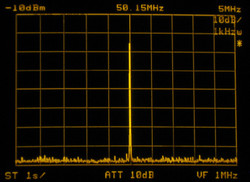

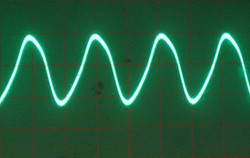

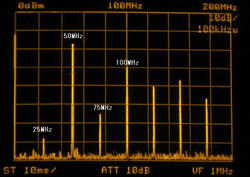

左上がドライバーのゲート電圧です。きれいな正弦波ではありませんが、FT450の出力が少し歪んだ状態で印加されており、FETのドライブとしては、ベストではありませんが、一応納得出来る波形をしています。 右上は、ファイナルのゲート電圧波形で、正弦波の先頭はつぶれ、かつレベルもドライバーの60%くらいまで下がっています。 前回のアンプはこの波形を正弦波に近づける為に、ドライバーとファイナルの間に50MHzの直列共振回路が入っており、確かに共振回路が動作していない時は5Wくらいしか出力できず、50MHzの共振させたとき8Wくらいの出力が得られていました。 この時のゲート電圧の波形は正弦波に近いものでした。

50MHz用のリニアアンプの情報は数えられないほどインターネット上に存在しますが、電源電圧が6.5VでRD16HHF1 PPによるリニアの範囲は2~3Wが限界で、10Wを得ようとすると、そこは非リニアな領域で、共振回路はマストであろうと思われます。

これらの推測から、AM変調が可能な特性を持つスイッチング用MOS-FETの場合、そのゲインが5dBくらいしかなく、かつ、矩形波によるドライブがマストであろうと思われます。 しかし、この周波数で矩形波によるドライブは不可能ですから、波高値の高い正弦波でドライブせざるを得ないのでしょう。

かくして、回路構成は前回と同様、各ステージの出力側に共振回路を設け、次段をドライブする条件で、いかにサイズダウンするか?電気機構屋に頼る事になりました。

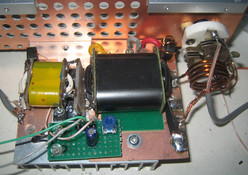

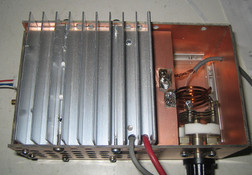

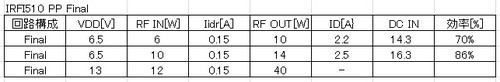

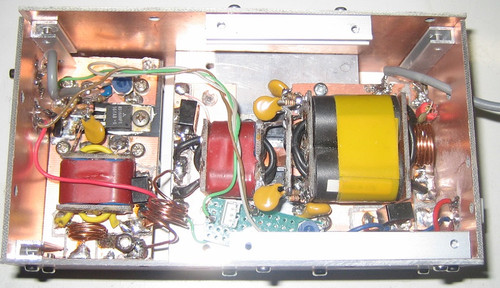

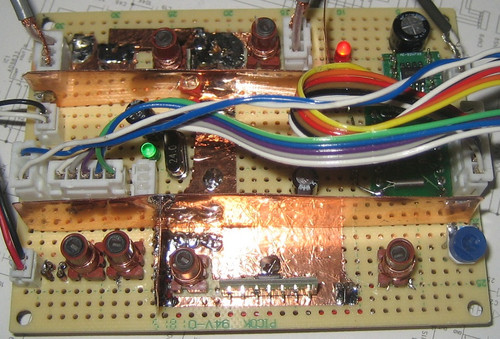

左上がIRFI510プッシュプルファイナルアンプの内部構造です。 右上はこのアンプをシールドで囲った状態です。 回路構成は左の配線図の如く、単純に一段だけを独立してユニットにしたもので、この単体の性能は下の表のようになりました。

電源電圧6.5Vの時、入力6Wあれば、目標のキャリア出力10Wは確保でき、13Vの時、入力12Wあればピークの40Wを確保できる見込みです。

次は、このファイナルをドライブするドライバー段です。 6.5Vにて6W、13Vにて12W以上の出力を狙いますが、こ時の入力は1W以下を目指します。

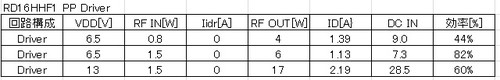

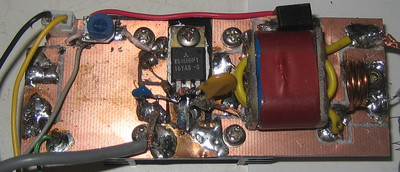

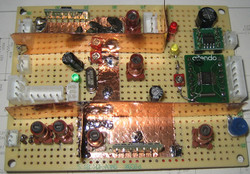

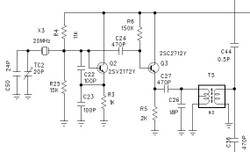

上の写真がサイズダウンして作成したドライバーです。 その回路図を右に示します。 (T4の1次:2次の巻き数比が逆です。1次0.5:2次2が正しい) 当初、ファイナルの予備検討で使ったカーボニルコア6個によるトランスで実験しましたが、コアの発熱がかなりあり、かつ出力もあまり改善しませんでしたので、前回の送信機に使ったNECトーキンのコアに戻しました。 下の表が、このユニット単体のデータです。残念ながら、6.5Vの電源で6Wを得る為の入力は1.5Wとなりました。 従い、この前段で出力1.5Wを対応する事にします。 13Vの電源の場合、出力が出過ぎのデータとなっていますが、全体を結合したとき、検討する事にします。 0.8W入力時、かえって電流が増えていますが、間違いではありません。 多分、入力のパワーが出力側へスルーして、見かけ上効率が良くなっているので、そのスルーレベルが少ない小入力時は効率が悪くなっていると推測します。

次は、PLL VFOの50MHz出力を1.5Wまで増幅するプリドライバーの検討をします。

左のユニットがプリドライバーで、RD16HHF1シングルのアンプで構成し、PLL VFOの出力を入力に加えると、2Wを出力します。

アンプそのものは、5Wの出力能力がありますが、PLL VFOのアンプをQダンプしたり、このRD16HHF1に、ドレインからゲートへ負帰還をかけたりして、50.2MHzから50.7MHzまで2Wを出力します。 アイドル電流は現在250mAくらいですが、出力が大きすぎた場合、このアイドル電流を絞って調整する事にします。

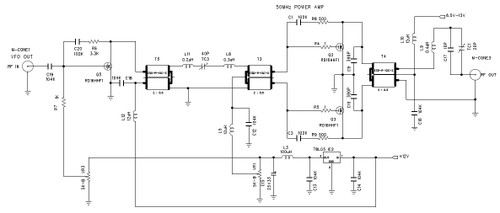

上の回路図は、ドライバーにプリドライバを連結した状態で、この回路全体をシールドで囲み、ひとつのユニットにしたのが下の写真です。

上の回路図は、ドライバーにプリドライバを連結した状態で、この回路全体をシールドで囲み、ひとつのユニットにしたのが下の写真です。

一応全てのユニットが出そろいましたので、全体の構造検討に移る事にします。