50MHz AMトランシーバー(PLL VFO)

カテゴリー<6m AM >

6m AM送信機が完成し、900m近い山頂付近まで移動し、交信にトライしましたが、セパレート式のリグでは、その設営に手間取り、1局も交信できませんでした。 しかし、ローカル局の協力をいただきホームから1st QSOが実現できました。 これで自作送信機の完成を確認できましたので、次の段階に移り、これを移動に使えるトランシーバーに改造する事にしました。

トランシーバーの構成をブロックダイアクラムで検討し、すでに完成した回路ブロックがほとんどで、新規に開発が必要な部分はPLL VFO、送信用ミキサーの部分となります。 そこで、このPLL VFOの製作にかかりますが、まずはトランシーバー用として必要なLCDディスプレイを作る事にしました。

ブロックダイアグラム 6mTransciverBlockDia1901.pdfをダウンロード

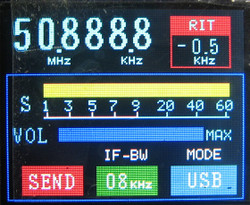

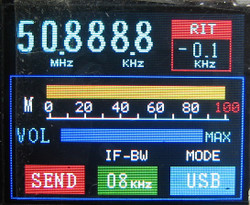

そして、以前作成したDSPラジオ用と同一型番のLCDを使い、LCD表示の試作をおこないました。

左上がSメーター、右上が変調度計をバーグラフで表示させたものです。各インジケーターは実際の動作に合わせ、点いたり消えたりします。 MODEのUSB表示は受信時のみ可能で送信はAMオンリーです。

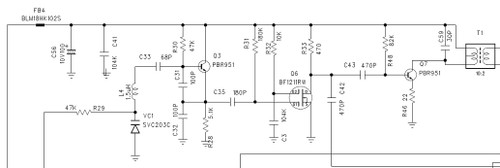

全体の回路図 30MHz_DDS_PLL-VFO.pdfをダウンロード

私のRF回路ではNXP製のPBR951が多用されていますが、これは、手持ち在庫が沢山ある為、使っているもので、秋月で手にいる2SC3356に置き換え可能です。

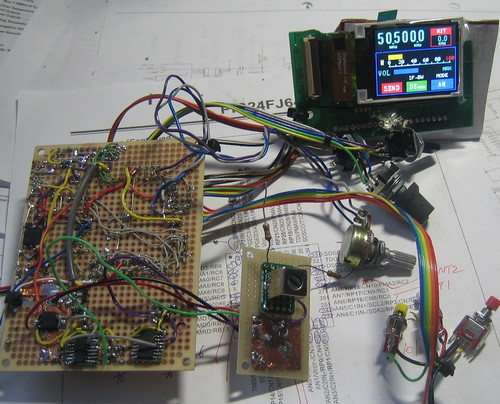

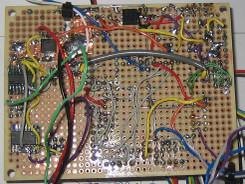

下の写真は、一応全ての回路がマウントされた基板完成品の状態です。

VCOはチップインダクタL4 1.5uHとC34バリキャップSVC203Cの片方のエレメントのみで30MHzに共振させます。この回路定数にて27MHzから34MHzまで発振します。 R28が低すぎるとブロッキング発振をおこしますので、R28を1KΩくらいの抵抗にしておき、R30の最適値を求め、R30を固定抵抗に置き換えます。 次に、R28を可変抵抗に変え、最適値を探します。この回路の場合、最適値は5kΩとなりましたので、一番近い5.1KΩに差し替えました。その後、R30を再度可変抵抗に変え、出力の歪が一番少なくなるような波形が得られる抵抗に置換します。

VFO出力段のバッファーはaitendoで販売している10mm角のIFTキットをコレクタに接続し、30MHz付近で共振するようにコイルを巻きました。 しかし、このIFTは基本的に455KのMW用で30MHzでは共振ポイントが得られませんでした。 そこで、同じくaitendoで扱っている7mm角のコア入りボビンに交換しています。

このボビンに0.26φのUEWを1次側10ターン、2次側2ターン巻きました。1次側のインダクタンスは約1.2uHで多少は可変できます。

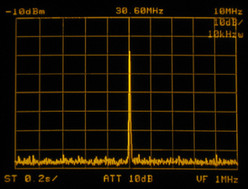

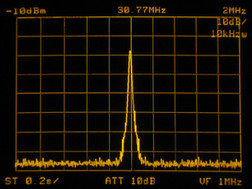

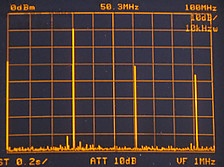

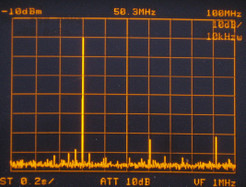

VCO単体のスペクトルは以下のようになりました。

左上が10MHzスパン、右上が2MHzスパンの綺麗なスペクトルをしております。

このVCOを制御するのは、AD9833のDDSと74HC4046のPLL及び1/10分周を行う74HC4017です。VCOは30MHzから31MHzを発振しますが、DDSはその1/10となる3.0MHzから3.1MHzを1Hzステップで発生させます。そして、これらをコントロールするのに、PIC24FJ64GA004を使います。

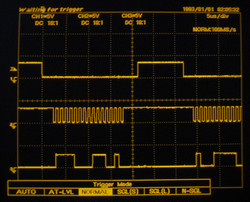

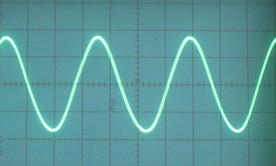

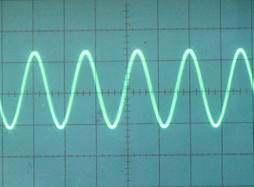

このマイコンはトランシーバーとしてのLCDディスプレイも処理しますので、44pinのQFPタイプです。 このPICによるSPIのマスター動作は初めてで、PIC24FJ用日本語のSPI解説書通りソフトを組んでも、まともに動作せず、左上の波形が得られるように適当に作りましたが、安定に動作しています。

右上の歪んだ正弦波はDDSからの3MHz出力でPLL ICのSIGin端子へ入力されます。 右下の方形波はVCOの30MHzを1/10に分周した信号で、PLL ICのCOMPin端子へ入力されます。

マイコンのソースコードを以下に示しますが、完成しているのは、LCDドライブとDDSのコントロール部分のみで、受信用のDSP(i2C)は未検証です。

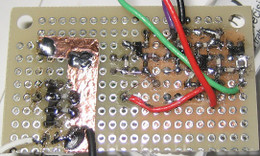

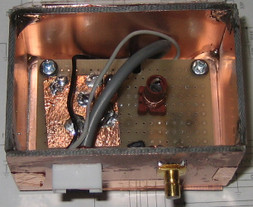

上の段がマイコンとDDS及びPLL回路が実装された基板。 下の段がVCO回路のみの基板です。 VCO出力段に5次のLPFも実装されております。

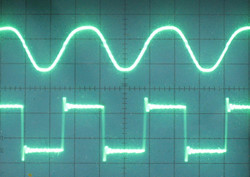

左上が、VCOタンク回路の出力波形、右上がそのスペクトルです。 最終段のLPFの前から取ったものです。

上の波形とスペクトルが最終段のLPFを通った後のものです。

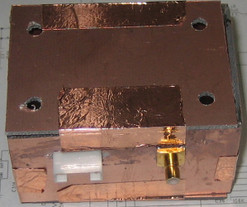

30MHzの隣接周波数に-60dBくらいのスプリアスが見えますが、これは、マイコン部分からVCO基板のハーネスにノイズが誘導しているもので、VCO基板を動かすと、増減します。 最終的には、送信機のファイナルと隔離する為、シールド構造にしますが、VCO基板そのものもシールド構造とすべく、最初から別基板として作ってあります。 下がそのVCOをシールドケースに収納したものです。

2019年2月追記

IF周波数20MHzは隣接スプリアスの関係でNGとなりました。 この為、IF周波数を26MHzか24MHzに変更する事にしました。 この対応でVFO周波数を23.5Mhzから30MHzまでの範囲に変更し、かつ回路構成も変更しました。

新しいブロックダイアグラム TransciverBlockDia2.pdfをダウンロード

新しいVFO配線図 25MHz_DDS_PLL-VFO2.pdfをダウンロード

6mのAMトランシーバーの外観ケースの構想が固まったら、このシールド構造の設計を行う事にします。

その外観ケースはこれです。 これをどうやって無線機に仕上げるか!

DSP受信部とキャリア生成回路の製作に続く。