7MHz RFユニット

<カテゴリ AM送信機(PWM方式)>

AM送信機のRFユニットの作成です。

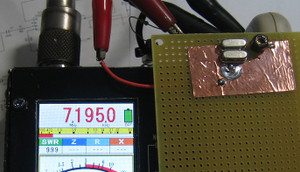

まず、7195KHzと予備として7190KHzをカバー出来るVXO回路を作る事にしました。

7.2MHzという水晶はAM/FMラジオ用PLLシンセの基準周波数として使われていたものですが、最近、この周波数の水晶が大量に格安で売られています。 今回は「aitendo」という通販ショップから購入しました。

この回路で7199KHzから7188KHzまでの11KHzを可変できます。水晶に直列に入れたコイルはSMTタイプの固定インダクタですので、最適インダクターとはなっていないかも知れませんが、目標とした2つの周波数は確保できましたので、良しとします。

AMのもうひとつの常用周波数である7181KHzをカバーするVXO回路の製作はこちらにあります。

次に、ドライバーとMOS-FETによるファイナル部分です。

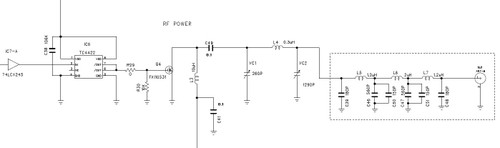

送信機全体の回路図 AMTX_0.pdfをダウンロード

Q3でTTLレベルまで増幅し、波形整形の為、CMOSゲートを通した後、FETドライバーのTC4422に入力し、その出力でMOS-FET FKI10531をドライブします。FETのドレイン側にはチョークコイルとフライホイール回路とインピーダンス変換トランスを設け、7MHzの7次LPFを通してアンテナに出力されます。 E級アンプの基本回路では、FETのドレインとGND間にCdsなるコンデンサが必要なのですが、FETのドレイン、ソース間に120Pの出力容量が存在しますので、60PFのトリーマーだけを入れてあります。 このトリーマーを回しても、出力や効率はほとんど変化しませんが、Vdの0V付近で発生するリンギングの様子が変化します。 調整はこのリンギングが最少となるポイントに合わせました。

この回路は下記のURLを参考に、13.8Vの電源で50Wを出そうと考え、設計しましたが、残念ながら出力も効率も全くダメでした。 (ダメな原因は私の使い方でした。ここで正しい使い方を紹介しています。)

http://people.physics.anu.edu.au/~dxt103/class-e/

当初6V12.5Wで設計したのですが、2SK3234で1Wしか出力できず、効率も30%以下でした。 色々WEB情報を調べても、6V12.5Wクラス(12V50W同等)のアンプは130KHzくらいのアンプの例しかなく、7MHzくらいの周波数では無理があるようです。 従い、6V5W(12V20W相当)まで出力を落とす事にしました。しかし、2SK3234ではどんなに頑張っても3Wくらいしか出ず、効率も50%くらいでした。 また、手元にIRF640もありましたので交換したところ4W出ましたが、効率は50%止まりでした。 そこで、変調器のFETはサンケンが一番良かったので、キャリア増幅用もサンケンのFKI10531に換えてみました。すると、5Wの出力で効率も60%くらいまで改善しました。

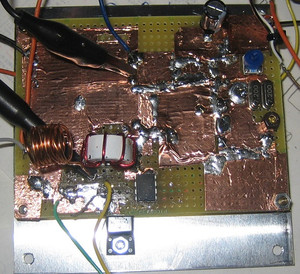

手前の基板がVXOとキャリア送信部です。 今回はVXOの出力は使用せず、アンテナアナライザーから7195KHz付近のキャリアを入力し、周波数を可変しながら、フライホイール回路が最適になっているかをテストしました。 基板上の黒い四角の物体はメガネコアで、ジャンク扱いのTS-930Sのファイナル段から取り外したものです。1次側は銅パイプによる1ターンの巻き数で、2次側はAWG24のビニール線を3ターン巻いてあります。 この出力は左上にあるコイル3個のLPFを経由してクラニシの終端型パワー計につないであります。

FETのドレインに接続される10uHのチョークコイルもTS-930Sのファイナル段から取ってきたものです。

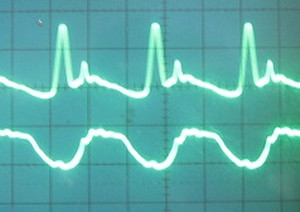

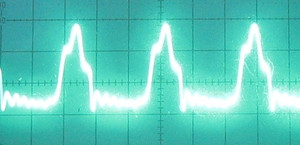

左のオシロ波形は下がFETのゲート電圧波形で8Vピークあります。 E級アンプの技術資料には決まって台形の波形が登場します。1.8MHzくらいなら、きれいな台形波形をしていますが、7MHzともなると、だんだん角が取れてくるようです。 当初、教科書通りの波形にならないので悩みましたが、WEBで見つけた7MHzや14MHzの1KWアンプのゲート波形はこれよりもっとひどくなまっておりましたので、安心しました。

上の波形はドレイン電圧の波形で、37Vピークあります。この時の正確なVDDは6.01Vでしたので、約6.2倍の電圧が発生しています。 このFETのVdmaxは100Vですので、16V以上の電源では使えないという事になります。 パワーアップする場合、再度FETの品種選定が必要です。

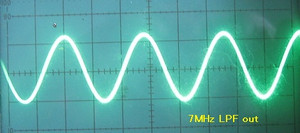

左の波形は7次バターワースLPFを通過した後の7MHz出力波形です。見た目での高調波歪はかなりよさそうです。 変調器との結合が出来たらスペアナでチェックする事にします。 この7次バターワースLPFの計算もPWM変調器用LPFと同じURLで計算しました。

コイルのインダクタンスが少し大きいとおもわれますので、現在の約1μHから約0.4μHくらいまで小さくし、シリーズコンデンサを約1500PFくらいまで増やしてみましたら、左のようなきれいなVd波形となりました。パワーは6Vで4W出ていますが、効率は、50%前後まで落ちました。

その後、13V 10Wの出力になるよう定数を変え、実験しましたが、テストした3種類のFETいずれでも55%以上の効率を確保できませんでした。 効率が上がらない理由は、FETも関係しますが、コイルやコンデンサ、トランスが最適になっていないのが原因のようです。

E級アンプの調整箇所を少なくして、検討しやすくする記事が見つかりました。 これによると、コイルにシリーズに入るコンデンサを無くした代わりに、コイルの前後にコンデンサを追加し、コイルとコンデンサ2個を最良状態にもっていけばいいようです。

フライホイール回路の直列共振コンデンサを廃止し、トランスも止めて、LCによるインピーダンス変換回路をジャングル配線で試したところ、2SK3234では55%の効率でしたが、FKI10531では75.5%まで改善しました。 ただし、5Vで1.5Wしか出ていません。 12V換算で9W弱ですから、目標にはまだまだですが、効率を上げる方法が判ってきました。

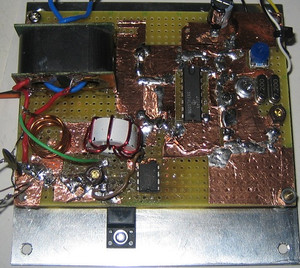

効率を上げようとすると、出力にリンギングが激しく乗ります。これを対策する事を含めて、各回路の配置をやり直し、かつトランスも廃止したのが左の写真です。

コイル両端のコンデンサをバリコンに置き換え、コイルも効率最大となる値になるよう試行錯誤した結果4.8Vの電源で1.8Wの出力が得られた時のIdは0.392Aでした。 効率は95.6%と計算されました。 この時の負荷インピーダンスは約12Ωです。

ここまで出来ると、後は、効率を我慢できるレベルまでダウンさせ、6Vの電源で何ワット出力できるか探ることにより、なんとか実用できそうです。

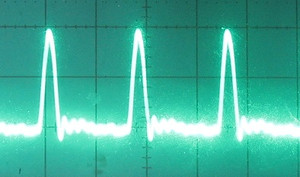

左は、この95.6%の効率の時のVdの波形です。従来の波形よりいびつですが、FET OFFの時のVdの面積が明らかに広くなっています。 また、この時の波高値は25Vくらいで、初期のころよりピークは小さくなっています。 この事は、Vdmax100VのFETでも電源電圧を19Vまでかけても良いという事になります。

左は、この95.6%の効率の時のVdの波形です。従来の波形よりいびつですが、FET OFFの時のVdの面積が明らかに広くなっています。 また、この時の波高値は25Vくらいで、初期のころよりピークは小さくなっています。 この事は、Vdmax100VのFETでも電源電圧を19Vまでかけても良いという事になります。

この状態の時の回路図を以下に示します。

当初の目標である6V 5Wの出力にトライし、効率78%を得ましたが、激しいリンギングが発生し、回路が安定しません。 リンギング対策は難航を極めました。 上のトランスの無い回路では、フライホイール回路に流れる歪んだ電流経路が多技に渡り、発振現象を押さえるのがとても難しくなりました。 そこで、最終的に、フライホイール回路のコイルの向きを90度変え、かつトランスを復活させフライホイール回路電流通路の単純化を行い、出力も3.4Wまで落とした結果、なんとか安定して動作するようになりました。この時の効率は70%くらいです。

また、OSCとFETドライバーの途中に挿入したバッファーもインバーターに換えました。 これはOSC回路が動作停止したとき、ファイナルのFETのゲート電圧が8Vで固定され、大電流が流れ、FETが壊れるのを防ぐ為です。

復活したトランスはTS930Sのファイナルの入力段に使用されていた小型のメガネコアに変えました。

変調器から見たインピーダンスは約7.2Ωとなりました。

ファイナルのFETはベースのアルミ板にビス止めしてある事もあり、ほとんど発熱しませんが、TC4422はかなり熱くなります。 このICはスペック的にデータが公表されているのは2MHzまでで、7MHzは実力で動作していますので、製品ロットでかなりバラツキがあるのかも知れません。 データシートによれば、FETのゲート容量1500PFで、8Vの時の消費電流は2MHzにて74mAくらいと予想できますが、実際の回路では7MHzで200mA流れています。 次回の検討では、このICよりもう少しドライブ能力の高いTC4452を手配してみる事にします。

修正した回路図 AMTX_2.pdfをダウンロード

TC4452手配がまだですので、先にパワーアップ検討を行いました。

E級アンプ 出力アップ検討 に続く。